## **TRIPS: Single Chip Teraflop Computing**

## Impact: High Performance and Adaptivity

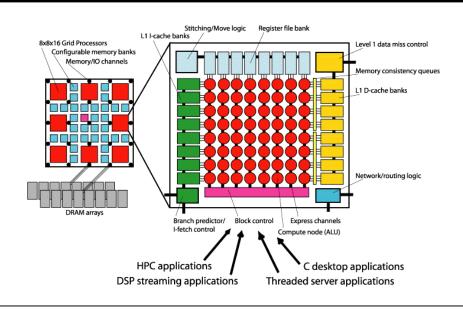

**Scalable Commercial Performance**: 500 GIPS in a 35 nanometer design, 60 GIPS in a 100nm prototype.

**High performance signal processing**: 5 Teraflops per chip in a 35 nanometer implementation, 300 GFLOPS in a 100nm prototype.

**Large economies of scale**: Merge the desktop, HPC, DSP, and server markets into a single family of TRIPS implementations by 2010.

## New TRIPS Technologies

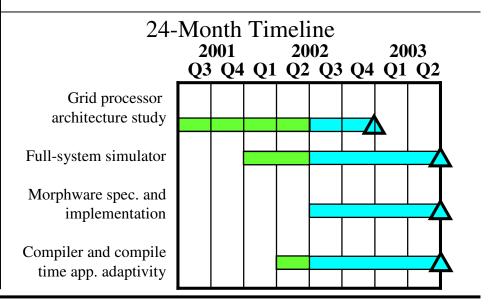

**Grid Processor Cores**: Technologically scalable, adaptive high performance for signal processing and commercial apps.

**Non Uniform Cache Architectures:** Automatically adapts to working set of applications, delivering stable performance.

**LibOS Morphware**: User-level software layers allowing high-performance morphing with reduced programming time.

**Application Adaptivity**: Library and compiler support for applications to run on multiple platforms and environments.

The University of Texas at Austin/IBM Austin Research Laboratory: PIs Stephen W. Keckler and Doug Burger