# Verifiable Computer Security and Hardware: Issues

William D. Young

Technical Report 70

September, 1991

Computational Logic Inc. 1717 W. 6th St. Suite 290 Austin, Texas 78703 (512) 322-9951

This work was sponsored in part at Computational Logic, Inc. by the Naval Research Laboratory, contract number N00014-90-C-2351 and is the final report on Task 1 of this contract. The views and conclusions contained in this document are those of the author(s) and should not be interpreted as representing the official policies, either expressed or implied, of Computational Logic, Inc., the Naval Research Laboratory, or the U.S. Government.

# Abstract

This report explores the influences of hardware on verifiable secure system design and envisions a mutually beneficial collaboration between the hardware verification and security communities. Hardware verification techniques offer the possibility of significantly enhanced assurance for secure systems at the lowest levels of system design and implementation. Security can provide an important and challenging applications arena in which hardware-oriented formal approaches can be tried and refined. We discuss some of the important concepts and issues that arise in trying to apply formal techniques to secure systems at the hardware level: the meaning of "security" in the context of hardware; the way to identify appropriate security properties at each level of system description, including the hardware level; and, a number of specific concerns related to hardware and its use in secure system development.

## 1. Introduction

The application of formal methods has been firmly entrenched as an approach to enhancing system security at least since the formulation of the A1 and beyond-A1 level requirements of the *Trusted Computer Systems Evaluation Criteria* (TCSEC) [99]. However, the formal analysis applied in secure system development to date has typically been carried out at rather high level of abstraction, leading some to question its usefulness and cost effectiveness in finding and eliminating security flaws in implemented systems. Some current work in verification [9] suggests that techniques and tools are becoming available for formal analysis at a level much closer to the actual implementation of a secure system. Formal analysis is addressing system issues that were previously intractable; distributed systems [28], real time systems [68], and particularly hardware [29, 79, 127] are coming within the scope of formal techniques. Future secure system development efforts could profitably apply these emerging technologies to further enhance system security.

Hardware is an obvious area in which to apply the latest formal analysis techniques. The *selection* of an adequate hardware base is obviously crucial in secure system development. It must be possible to build the protections mandated by the security model on top of the mechanisms provided by the machine. It is unlikely that the protection structures of the machine will match so closely the needs of the model as to be totally sufficient. But it is crucial that they not be incompatible with the requirements of the model. Consequently, attaining the highest possible assurance of security necessarily involves scrutinizing the hardware base upon which the secure system is built.

The *correct functioning* of the hardware is also crucial to the behavior of secure systems built on top of that hardware. Failures of hardware can seriously impact security. For example, one study [93] of the IBM 360/50 found "a total of 99 single-failure hazards [...] in the storage protection hardware and three [...] in the Program/Supervisor state logic. Any of these hazards could compromise the system security without causing a system crash" [130].

We envision a collaboration between the hardware verification and security communities that can be mutually beneficial. Hardware verification techniques offer the possibility of significantly enhanced assurance for secure systems at the lowest levels of system design and implementation. Security can provide an important and challenging applications arena in which hardware-oriented formal approaches can be tried and refined. Attaining assurance of correctness at the hardware level is an important but largely neglected area of concern in secure systems research. A number of studies have concentrated on the hardware security features of particular machines [26, 27, 48, 50, 62, 104, 118, 122, 129, 135]; several others [47, 49, 50, 64, 77, 78, 93] have focused on the general relationship between hardware and security. But almost no work has been done on the use of formal verification techniques to enhance the security of the hardware support for secure systems.

This report discusses some of the important concepts and issues that arise in trying to apply formal techniques to secure systems at the hardware level. In the following section we discuss the meaning of "security" in the context of hardware and the way in which we can identify appropriate security properties at each level of system description, including the hardware level. Section 3 describes a number of specific concerns related to hardware and its use in secure system development. The final section contains some conclusions about the use of formal approaches to enhancing system security at the hardware level of system design.

Many of the issues that we discuss in this paper deal with the use of general-purpose hardware used in the construction of secure systems. Various other issues arise when dealing with custom, application-specific hardware. For these, our discussions of security models, memory management, process support will not generally apply. The specific issues which do arise for these types are hardware are beyond the scope of this discussion.

## 2. Defining Security for Hardware

This study is principally concerned with the following two questions.

- How can hardware help or hinder system security?

- Can formal methods be usefully employed at the hardware level to enhance system security?

- To address these, we must first consider two more basic questions.

- What does it mean for hardware to be secure?

- Is it even meaningful to refer to secure hardware?

These are the questions we address in this section.

Security is a property of an information system as a whole, rather than of particular components of such a system. Portions of the system may have specific properties whose maintenance is critical to system security; these portions may then be described as *security-relevant* or *security-critical*. However, it is the system as a whole that is either secure or un-secure. Consequently, it is somewhat misleading to discuss security properties of hardware, unless, of course, the hardware in question constitutes a complete information system. Still, it is commonplace to refer to the security properties of a system component and we will use that terminology unless there is any danger of confusion. Keep in mind that we are referring to those properties of the system components that are required to *support system security*, whether or not they would be naturally identified as "security properties" in any obvious sense. We discuss this issue further in the following subsection. In Section 2.2 we consider the question of how to identify properties of hardware supportive of security and how to construct a specification that captures these properties. Section 2.3 discusses the role of formal techniques in assuring the security of systems. Finally, in Section 2.4 we talk about hardware verification specifically and how it can be an effective adjunct to other techniques used in enhancing the security of systems. Specific features of hardware and how they relate to security are discussed in Section 3 in the second half of the paper.

### 2.1 Security Models

Security for an information system is typically defined in terms of a *security model*, which is both an abstraction of a class of information systems and a characterization of what "security" means for that class of systems. The model may be very abstract (eg., the machine model used in the definition of noninterference [52]) or be fairly concrete and include specific security control *mechanisms* (eg., the Bell and LaPadula model [7]). At base, a security model is simply a *specification* of an information system (or class of systems) and its security properties.

What we are calling models here are no different than what are called specifications in the conventional software engineering process—and this is an important point: security models are nothing more than (usually formal) requirements statements and specifications for the security properties of a system design. As such, they are subject to the usual desiderata for specifications. [115]

Note that this is not a universally accepted view of models. There is considerable murkiness in the security literature about just what constitutes a security model, and endless confusion arising from the use of the overloaded word "model." Some argue that "model" should be thought of in the sense of a scientific theory (as Newton's laws are a model of the motion of bodies). Others construe models in the sense of a mathematical theory—a collection of a formal structures and axioms about their manipulation. Some of the attempts to clarify this issue merely exacerbate the confusion. Bell [6], for example, argues vehemently that the Bell and LaPadula model is an "abstraction" (but without once saying *of what* it is an abstraction). Some of the best books on the subject of secure systems [35, 47] give numerous properties and examples of models without ever defining the term "security model." This confusion and ambiguity leads some [58] to question the usefulness of the entire notion. We believe that our view of a security model as merely a specific type of system specification that characterizes security for the system in question is the most useful approach from a verification standpoint.

## 2.1-A Types of Security Models

Most security models assume a class of active entities (*subjects*) and a class of passive entities (*objects*). Frequently, subjects and objects have associated *security levels* drawn from some ordered set. The intent of the model is to constrain the flow of information among the subjects in the system in some way determined by the ordering. For example, in models based on military security the levels form a lattice [34] or potentially a collection of lattices [44]. Intuitively, information may only flow "upward" in the lattice. The model defines security in such a way as to formally capture this intuition.

Access control models attempt to limit the flow of information by specifying the types of access (e.g. read, write, execute) each subject may exercise with respect to each object. In its most general form, the security model of the system is conceptually a matrix indexed by subjects and objects and specifying what types of access each subject may exercise to each object. [60, 76] For example, subjects may have read access to files that are at or below their level in the lattice. The intent is to limit information flow by imposing certain operational constraints on subjects.

The Bell and LaPadula model [7] is an access control model that incorporates a number of rules designed to restrict the flow of information. Among these rules are the *simple security property* and \*-*property*—often summarized, respectively, as follows: a subject may only read an object at a level at or below his own level (in the security lattice), and a subject may only write to an object at or above his own level. Variants of the Bell and LaPadula model have been widely used in secure system development [3, 46, 55, 85, 102, 120] despite the fact that the model does not preclude some types of intuitively un-secure behavior (covert channels).

*Information flow models* tend to be more abstract than access control models. Rather than define security in terms of the permissible accesses of subjects, they define security in terms of the absence of certain prohibited information flows, without regard for the particular mechanism through which these flows may occur. Thus, un-secure information flow is proscribed, even if no action of any subject violates the access control rules of the system. Several of the most widely studied security models are noninterference and non-deducibility.

Noninterference [52, 53] is an information flow model. Subject a is noninterfering with subject b if no action of a can have any effect on subsequent actions of b. Any specific noninterference policy specifies pairs of subjects that must be *noninterfering*. A noninterference policy tends to be stronger than an access control policy since it precludes information flowing through mechanisms that are not easily captured in the framework of subject-object access. Noninterference is limited to deterministic systems. It has been used as the security model for at least one large system development effort [16, 119].

Non-deducibility [128] is a strengthening of noninterference suited to non-deterministic systems. The key idea is the following. Assume that subject *a* is prohibited by the policy from passing information to subject *b*. The system is non-deducibility secure if any possible set of observations of the system by *b* is *consistent* with any possible set of actions of *a*. Daryl McCullough [87] has proposed a variant called *restrictiveness* that has the so-called "hook-up" property—two restrictive systems can be combined to yield a restrictive system. This model of security is used in the Ulysses (later called Romulus) system [86, 111] of Odyssey Research Associates.

A large number of other security models [21, 30, 34, 65, 88, 108, 131, 132, 134] have been proposed. Some have been general purpose and others designed for fairly specialized applications. Most have been concerned with preventing information disclosure; but others have been concerned with *integrity* of information in the system [13] or with preventing the denial of service to legitimate users [51]. In real secure system development efforts, most of these have given way to variants of the Bell and LaPadula model or to noninterference and restrictiveness. Some systems have used a combination of models; for example, the LOCK system [119] uses noninterference for the most abstract characterization of security for the system and uses an access control policy at lower levels of abstraction.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>The reader will undoubtedly notice that there are many references in this paper to the LOCK system, developed by Honeywell and the Secure Computing Technology Corporation. We use LOCK heavily in our discussion both because it is a well-designed and innovative system and because it is the secure system development effort with which we have been most heavily involved and of which we have the most direct experience.

This discussion has concentrated on models for information systems as traditionally defined in "mainstream" computer security, i.e., mainly focused on the security of operating systems. There are many applications that are considered to be within the purview of security research<sup>2</sup> but that are not operating systems. These include secure distributed systems and networks, secure database systems, and various specialized devices such as crypto boxes and "guards." A considerable amount of attention is being directed to extending existing models to cover networks [100] and to using the facilities provided by secure operating systems to construct secure database systems [39]. Specialized devices require specialized models that may be quite different than those discussed above as suitable for operating system security. Some very successful modeling and verification efforts [73, 121, 124] have been directed at such applications.

The choice of hardware support for a secure system will likely depend on the model of security to which the system must conform because the model delimits the legitimate actions of any subject/process.

The choice of protection model is important because actions of programs operating on behalf of different users have different effects whenever different protection models are used to authorize those actions. For example, programs representing two different users may read and write a segment in a model that allows controlled sharing, such as the Access Matrix (AM) model. However, if those programs operate at different security levels, as defined by some Multilevel Security (MLS) model, then either one or the other of the programs is prevented from writing the segment. Thus, the action of writing a shared segment is a legitimate action within one model and a protection violation within another model. [48]

Certain types of hardware support are better suited to enforcing certain types of restrictions than others. Thus, in choosing a hardware base for a secure system, it matters what types of restrictions are intended. These in turn are determined by the model. In Section 3 we discuss specific hardware mechanisms and their relationship to particular types of security concerns.

## 2.1-B Properties of Security Models

As noted above, any specification of the system or class of systems defining the desired security properties of the system. As with any system specification it can be very formal or quite informal, abstract or concrete, complete or partial. The value and usefulness of the model depends upon each of these choices.

Ideally, a model should be formal. An informal model may be ambiguous, inconsistent or both. A formal model allows the application of rigorous reasoning techniques and tools to establish the consistency of the model and the conformance of the system model with its security requirements. [59]

Also, a model should be abstract. The careful use of abstraction can yield important clarity and intuitive structure to the system description and can provide significant help in formal analysis [67]. However, providing an appropriate level of abstraction can be a challenge. A model that is too concrete will often characterize security implicitly in terms of the mechanisms that are designed to provide it and thereby restrict the options of the implementor. A security model that is too abstract, on the other hand, may be too far removed from the realities of system design to provide much practical benefit.

The *style* of abstraction is important as well. We believe that it is dangerous to provide abstraction by neglecting system functionality in the model, i.e., by leaving the model incomplete. Completeness means that the model contains, in abstract form, all of the important essentials of the implementation. This issue is discussed further in the following subsection.

$<sup>^{2}</sup>$ Information security (INFOSEC) is sometimes defined to be the combination of computer security (COMPUSEC) and communication security (COMSEC).

## 2.2 Security Properties of System Components

Recall that the security model for a system refers to the secure operation of *the system as a whole*. How do we move from a system level model to appropriate specifications for the components that are comprised by the system, and ultimately to properties of the underlying hardware?

Assuming that we have defined an appropriate security model (specification) for the system as a whole, we can refine this into properties for the system's components in a very disciplined way. Since system behavior is determined by the behavior of the components and by the interactions among them, system properties, including security properties, must be implied by properties of the components and information about their interconnections. This suggests that the appropriate methodology for building secure systems is to begin with a high-level specification of the system and its desired security properties and to work downward toward an implementation. At the highest level of decomposition, the security properties of the system should be implied by (be provable from) the architecture of the system and the top-level properties of the component modules. These modules can, in turn, be refined into lower level modules whose properties should be those required to support the higher level abstraction. Thus, the properties of all modules in a secure system are *derived* from the requirement to support the properties of the level above. In other words, the security-relevant properties of any module in the system are exactly those properties that are required to support the architectural layer "above."

Of course, it is not usually practical in any real system development effort to follow a completely top-down approach. There is always a concern in any development effort that the lowest level hardware be adequate to support the requirements of the top-level specification. It is impractical to believe that the structure of the hardware can be completely ignored until all of the top level design issues have been thoroughly explored. However, we advocate as a general rule that our specification effort proceed top-down, with an informed understanding of what's below, and a willingness to iterate the process if the derived requirements are unimplementable on the available hardware base.

Deriving the specifications of system modules from the requirements of the calling environment is an obvious and intuitive approach to system development and one that has been institutionalized in, for example, the Gypsy Development Methodology [123].<sup>3</sup> Nevertheless, we are not aware of any actual sizable secure system development that has followed this approach. Used consistently in secure system development, it has the following important but possibly surprising consequences for defining the security properties of the various components of a secure system.

- This approach to secure system development will automatically delimit the "security perimeter" of the system.

- The highest level system specification should be "complete," in the sense of covering all system functionality.

- It is usually a mistake to attempt to define the security properties of low level modules *a priori*.

Let's elaborate on these points further.

## 2.2-A Determining the Security Perimeter

A common approach to building a secure system is to partition the components of the system according to a perceived "security perimeter" and apply rigorous analysis only to those system components lying within this perimeter. This security perimeter is often referred to as the "trusted computing base" or TCB and "serves to encapsulate all the security-relevant features of a system: nothing outside the TCB can impact the security of the system performance but will not result in any breach of security. The process of determining which aspects of the system are security-relevant is typically an informal and *ad hoc* process; the perimeter may have to be continually readjusted as the security implications of various system components" behaviors becomes more clear [113]. An overly lax appraisal of which system components

<sup>&</sup>lt;sup>3</sup>Some similar work formally deriving requirements from higher level specifications is reported in [94, 95].

are security-relevant may leave genuine security flaws in the system. An overly conservative drawing of the security perimeter will lead to costly and unnecessary analysis.

Our approach of using top down system specification and development leads to a formal derivation of the security perimeter. System modules within the perimeter are exactly those whose constraints contribute to the proof of the system-level security properties. Modules that can be left unconstrained when proving the top-level security property do not contribute to system security, and, conversely, cannot interfere with system security. Therefore, they can be safely excluded from formal analysis; they are truly outside the security perimeter. Modules that must be constrained in order for the higher level properties to be assured are those that contribute to the security of the system and that could possibly compromise it. They must be inside the security perimeter. By following a careful top-down style of security analysis, we automatically gain the very significant benefit that one of the most important and error-prone tasks of secure system development—determining the security perimeter—comes for free.

## 2.2-B Coverage of the Top-Level Model

Our approach to deciding what properties are required of the various components of the system assumes that the top level specification encompasses the *complete* secure system. If we specify only a portion of the system under some preconceived notion that some components are not security-relevant, it may turn out that our analysis will fail to uncover potential insecurities in the excluded portions. Thus, it is dangerous to leave out system components and functionality in the highest level description. Of course, we may still have intuitively un-secure behavior in the implementation due to a security model that is too weak to exclude it. But we will not have behavior counter to our security model because of security-relevant interactions with system components that were incorrectly believed to be security neutral.

Our highest level model must be "complete" for another reason. If we leave out aspects of the system in our highest level model, requirements on the system will likely force the addition of functionality in lower levels that is not reflected at all in the high levels. Thus, even if the high level design is provably secure, there may be additional capability in the implementation that can be exploited and that is accessible to a determined attacker.<sup>4</sup>

That said, we realize that it may initially seem unreasonable to reflect the entire system functionality in the highest level model. In doing so, don't we risk losing all of the benefits of abstraction? There are various ways of introducing abstraction into a formal specification—structural, behavioral, data, and temporal abstraction. [90] In each of these, we can use the abstraction mechanism either for safely *hiding details* in the model or for unsafely *eliminating details* from the model. Various abstraction in Ada (possibly implemented by interface assertions) allows suppressing the body of a routine while leaving the interface information for the routine complete and correct. This hides detail but without losing information that may be crucial to analyzing the correctness and security of a system.<sup>5</sup> For secure systems, we believe that any method of abstraction that loses information by selectively neglecting portions of the systems that may in fact be security-relevant is a dangerous luxury. This is because security is different than many other system properties that may be of interest.

Consider, for example, the correctness of a compiler. The purpose of a compiler is to *implement* the abstractions provided by a high-level language on the support provided by a lower level language or machine. The compiler is correct if each syntactically permissible program of the source language is translated into a syntactically correct and semantically equivalent program of the target language. However, there is nothing in the compiler that prohibits the machine user from accessing the lower level

<sup>&</sup>lt;sup>4</sup>An example of how the use of a high-level specification (of a password protection scheme) can hide exploitable insecurities at a lower-level is described in [138].

<sup>&</sup>lt;sup>5</sup>Of course, this is not quite true because of the possibility of non-local referencing and the probability that the system is accessible other than through the Ada compiler. Some languages, such as Gypsy [123] are designed in such a way that *all* of the potential effects of a routine are completely delimited by its interface specification. This supports the Gypsy *Independence Principle*: the specification of any Gypsy routine must be provable solely from its body and from the externally visible specifications of the routines it calls.

directly and performing actions that are not specifiable in the higher level (abstract) language. In fact, facilities are often added to high level languages to permit linking with assembly language routines. That is, the user's access to the machine is not limited to the abstractions provided by the high-level language through its compiler.<sup>6</sup>

Consider also the construction of safety-critical systems. Building secure systems is often compared to building safety-critical systems. Many of the same concerns for high assurance apply and many of hardware features that are potentially troublesome from the point of view of safety are of concern in security. For example, the British Ministry of Defence 00-55 draft standards [91] prohibit the use of certain types of hardware features, such as interrupts, in safety critical applications. However, this does not mean interrupts are not permitted on the hardware base on which a safety-critical system is constructed, but merely that they may not be used by the safety-critical system. Again, the machine user is not prohibited from accessing "dangerous" features; he simply may not access them via the abstractions provided by the safety critical system.

In contrast to these applications, security is not merely a collection of high level abstractions that are to be implemented by the lower level machine. Security is a property of the lowest level implementation, and it is crucial that the implementation perform the secure operations of the model *and nothing else*. If a hardware feature is dangerous from a security standpoint, not only may it not be used by the secure system, it should not be accessible on the hardware platform at all. A secure system must be designed with the presumption that if there is an available avenue of attack, malicious users will find and exploit it. It is this "and nothing else" constraint that makes it crucial that all of the possible actions of the implementation be reflected into the highest level models of the system to whatever degree possible. Otherwise, there may be accessible functionality at the low levels that can be exploited to violate security, but functionality which is not represented in the high level models. The fact that it is not represented in the high level models means that our high level analysis cannot find and exclude it. Our high level security specification may be *correctly implemented* and still intuitively un-secure.

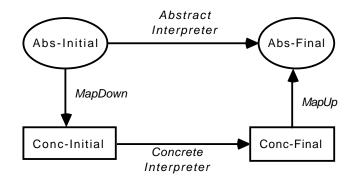

This suggests, by the way, that "implements" as that term is often used is too weak a relationship between a security model and its realization. If implements is defined in terms of a commuting diagram such as that shown in Figure 1, this is inadequate to establish the security of the system.<sup>7</sup> The proof of such a commuting diagram shows that the abstractions defined by the high-level system are "implemented" by the lower level, but not that dangerous features of the lower level support are not accessible outside the abstractions defined by the high level. An adequate proof of security requires that the two level of abstraction be formally *isomorphic* in the sense that any insecurities in one are reflected in the other. Implements may be necessary for security but not sufficient.

Only methods of abstraction that manage complexity without discarding it are adequate for secure system development. We believe strongly that by careful use of procedural and data abstraction and by structuring a system design appropriately, it is possible to achieve both completeness *and* abstractness. Good [57] illustrates an approach for a simple secure system which meets these aims.

We should note that a quite successful approach to introducing abstraction into the specification of a secure system while preserving completeness was taken on the LOCK project [19, 137]. There, the highest level (abstract) models were used principally to establish and refine the security properties of the system. The crucial proof of the system security properties with respect to a formal description of the complete system interface was actually carried out at the Formal Top-Level Specification (FTLS) level against a formal characterization of security appropriate to that level of abstraction. This is the highest level of abstraction at which the full interface to the trusted computing base is visible. An informal mapping was given to higher level models, but the proof of security of the system did not depend upon the correctness of this mapping because the model was fully redefined at each level in the hierarchy. Therefore, the proof of security was carried out with respect to a relatively complete representation of the system (as we have insisted must be done) and a definition of security appropriate for that model. The LOCK approach preserves many of the

<sup>&</sup>lt;sup>6</sup>There have been attempts to enforce security by permitting users to access a machine only through a high level language. [135] Such approaches are vulnerable to any means of directly accessing the machine at the assembly language level.

<sup>&</sup>lt;sup>7</sup>This is the style of proofs done on the CLI stack [9].

Figure 1: Implementation of Abstractions

benefits of abstraction as a tool for developing and honing intuitions about the secure system and its correctness properties, while gaining the benefits of "completeness" in the model.

## 2.2-C Modeling from the Top Down

Our final point noted above is that it is usually futile to attempt to specify a secure system from the "bottom-up." This is because we cannot know what properties are required of a module at the bottom of the call tree until we know its role in the system. The security properties of a module may depend upon the security properties of its component modules, upon their functionality, or on both. Thus, the specification of a module is driven by the requirements of its calling environment.

Consider, for example, how to determine what requirements should be placed on the utility that retrieves a file in a multi-level file system. This is arguably a security sensitive function and so must have some security properties. However, we can imagine that the level and access control information relating to a file could be maintained in either of two places: physically with the file or in a separate table. Fetching a file (securely) from disk could be implemented in at least two different ways, depending on where this information is stored.

- 1. Assume that each file is stored along with its associated security information (possibly in the file header). We can fetch the requested file, check its associated security information against that of the requesting subject and deliver the file if the access permissions match in the appropriate way. Notice that no security violation occurs *even if we fetch the wrong file*.

- 2. Alternatively, assume that the security control information is stored in a separate table. We check the recorded level of the file against that of the requesting subject; if the subject has appropriate access rights, we fetch the file and deliver it to the subject. Here, it is vitally important that the file delivered is the same file as that whose level we checked in the table.

In these two cases, the primitive **get\_file** utility will have different required properties in support of system security. In the first case, there is no need to guarantee that the file returned is the one requested (though we would certainly like that to be the case). In the second case, we do require that property. In both cases, the required properties are dictated by the security requirements of the calling environment.<sup>8</sup> Beginning at the "bottom" and specifying the routine without clearly understanding its role in the system and the way in which it contributes to the overall goal of secure system operation is likely to result in a specification that is not adequate to the goal of verifiable security.

Experience in building secure systems bears out this observation. On the Honeywell LOCK project, for example, it was found that the required properties of the security co-processor (SIDEARM) were "security" properties and those of the kernel interface software (KIS) were largely "functionality" properties.

<sup>&</sup>lt;sup>8</sup>A similar point is made by Neely and Freeman [101] who call modules that contribute to the security of a system "trust domains" and note that the constraints on each trust domain are determined by its environment.

The verification of the KIS should be somewhat simpler than that of the SIDEARM. The verification is functionally-oriented as opposed to property-oriented, as in the case of the SIDEARM. One only needs to verify that the KIS adheres to some low-level properties. For example, the KIS must be shown to totally clear the CPU registers during a context switch. [119]

Of course, it is largely a matter of opinion whether any specific property should best be regarded as a security property or a functionality property. Clearing of CPU registers could be regarded as a security property since it enhances the security of the system. Our point is that the specification of the module is more likely to be "the registers have been cleared" rather than "the KIS is secure"—in the words of the quote above, "functionally-oriented" rather than "property-oriented."

We believe it likely that the smaller the module and the closer it is to ''raw'' hardware, the less likely it is to have identifiable security properties and more likely to have required correctness or functionality properties. At the very lowest level of abstraction, it is difficult even to imagine what a security property looks like; the notion of a secure *AND* gate is hard to envision. For this reason, any attempt to specify security-specific properties of low level hardware modules is likely to fail. This suggests an answer to Don Good's question of what a *secure wire* looks like [58]; it probably looks exactly like a *correct wire*.

This is not to say that we cannot identify security-relevant properties or hardware, only that the most security relevant property of hardware is often that it behaves in a functionally correct fashion. In support of this position we quote the findings of a recent report by the National Resource Council on hardware influences on computer security: "the only essential, then, is to have simple hardware that is trustworthy" [97].

Of course, some hardware features have been correctly identified as generally useful in the construction of secure computing systems. We will address a number of such features in Section 3. We merely caution that defining what it means to be a secure system, a secure module, and particularly secure hardware requires more care than is often given. A "secure adder" or a "secure UART" is largely meaningless except in the context of a larger system.

## 2.3 Formal Verification and Security

Much of the experience in applying formal techniques in secure system development to date has been driven by the requirements of the National Security Agency's *Trusted Computer Systems Evaluation Criteria* [99] (Orange Book). It is unclear how much of this experience is applicable to verifying secure hardware.

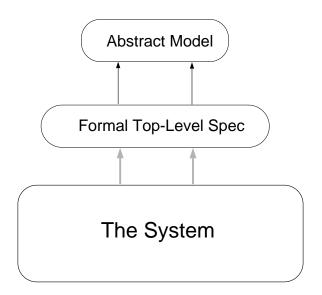

The approach mandated by the Orange Book requirements takes the following pattern:

- Formulate an abstract model of security for the system and analyze it using currently available formal techniques.

- Devise a Formal Top Level Specification (FTLS) for the system and show by "a combination of formal and informal techniques...that the FTLS is consistent with the model."

- Show correspondence of the FTLS to the TCB source code by "manual or other mapping."

- Conduct a covert channel analysis involving the use of formal methods.

This pattern of specification, illustrated in Figure 2, has become institutionalized by the promulgation of the A1 level requirements and is sometimes taken as illustrative of state-of-the-art formal methods in the security arena [8]. We continue to expect and accept this style and level of analysis for two major reasons.

- The common wisdom holds that this is the best we can do; code level verification of large systems is deemed beyond the current state of the verifier's art. The feeble mechanical support provided by the tools currently appearing on the NCSC's Endorsed Tools List [98] fosters this impression.

- The driving force behind contractor adoption of formal techniques has been the list of certification requirements in the Orange Book. By institutionalizing the *status quo* we have eliminated much of the motivation for innovative approaches to enhanced assurance.

Figure 2: Current Secure System Verification

There are good reasons for questioning the usefulness of this style of high level analysis. Rather than reasoning about implemented systems, it largely involves reasoning about the *specifications* of systems. We hope that these specifications will be reflected in the implementation in such a way that insights gleaned from the formal analysis will affect the ultimate quality of the system. Yet the link from the formalism to the nuts and bolts system is often a rather tenuous correspondence argument, the believability of which relies on an understanding of the semantics of *two* abstractions—the specification language and implementation—either of which may not be fully formalized. Even in those situations where the formal analysis has a significant influence on the actual design, the problem of establishing a convincing correspondence between a high-level Gypsy specification and a low-level C implementation, say, is daunting [138].

It has even been suggested that design-level analysis may actually be dangerous by fostering unwarranted assurance in "verified" systems. This perception is exacerbated by the fact that the formal methods community has been too glib in the past about stating what has been and can be accomplished with formal methods. Enthusiastic pronouncements by advocates of formal methods have been taken out of context [45] to provide a misleading picture of the goals and expectations of formal analysis. Marketing claims made regarding some "verified" products may not have been justified by the actual formal analysis. [24, 31] This again has the potential for fostering unrealistic and ultimately deflated expectations. Whereas we believe that design level verification has a role in improving the quality of systems, we feel that the technology is now available to combine these high level approaches with much lower levels of analysis. Particularly for safety-critical and secure systems, hardware verification can play a role in delivering very high assurance systems.

## 2.4 The Role of Hardware Verification

Hardware verification is a rapidly expanding research area. Researchers have considered verification of hardware at various levels of abstraction from circuit designs written in high-level hardware description languages such as VHDL [84, 117] down to low-level models of MOS circuits [25, 133]. Techniques have been developed that are adequate for handling small circuits [5] to handling entire microprocessors [66, 69]. There is a rapidly growing literature in this area [29, 79, 127, 136].

In many ways, verifying hardware is a more tractable problem than verifying software because hardware tends to be more regular. However many of the concerns are different and others are potentially much

worse in hardware. For example, pointers are traditionally quite difficult to reason formally about and many "verifiable" languages such as Gypsy exclude pointer manipulations. However, addresses are merely pointers and are pervasive in hardware operations. Consequently, imposing a discipline on address manipulation is essential to formal treatment of hardware. Such a discipline is exactly what is provided by memory protection hardware. A simple base and bounds scheme can guarantee that a program's access to memory will not extend beyond its permitted boundaries. Thus, the hardware mechanisms provide an essential structuring that can be relied upon by the verification of the higher-level protection mechanisms that are built on top of it.

This suggests the use of hardware verification techniques as a natural evolution of the application of formal methods in secure system development described in Section 2.3. The Orange Book A1 requirements call for "verification evidence consistent with that provided within the state-of-the-art." The discussion of "Beyond (Class) A1" systems acknowledges that "consideration will be given to the correctness of the tools used in TCB development (e.g., compilers, assemblers, loaders) and to the correct functioning of the hardware/firmware on which the TCB will run" [99]. Hardware has not been entirely neglected in secure systems specification and verification. Both the SCOMP [46] and LOCK [16, 119] specifications included protection mechanisms that were implemented in hardware as well as in software. However, these efforts considered features largely modeled at a level of abstraction where the distinction between hardware and software does not matter.

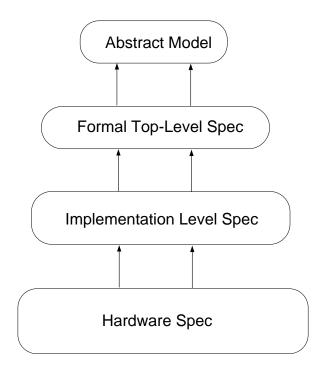

The paradigm of secure system development illustrated in Figure 2 may be extended "downward" toward the hardware level as shown in Figure 3. There are significant research issues involved in relating levels of abstraction involving both verified hardware and verified software. The CLI "stack" effort [9] may offer some directions. However, as we indicated in Section 2.2, the correctness properties of a compiler or assembler are different than the security of a system; *implements* is simply the wrong relationship between the layers of the hierarchy in a secure system development. We are aware of only a few efforts [12, 14], other than the CLI stack, in which properties defined formally at a fairly high level of abstraction have been "pushed down" to the hardware level; none of these were explicitly security properties.

Figure 3: Proposed Secure System Verification

As an example of a significant and challenging research area where hardware modeling and verification could contribute consider hardware features such as memory protection mechanisms and support for process isolation. Such features often form a base upon which secure systems are constructed. For example, many of the security models discussed in Section 2.1 above take as primitive the notion of identifiable and separate "subjects" that are the active agents in the system. In implementations, these are often identified with processes supplied by the underlying operating system or hardware mechanisms. Process isolation, then, is crucially relied upon by the security mechanisms and taken more or less for granted in the model. Yet, such underlying mechanisms have often been found to be the source of security flaws in implemented systems [1, 2, 62, 83, 135].<sup>9</sup> Few serious attempts have been made to formally model and verify these crucial underlying facilities;<sup>10</sup> these facilities are obvious candidates for formal scrutiny at the hardware level.

But how can we go about assuring the correctness of such basic mechanisms? There is no fundamental difference between, for example, proving the correctness of a process isolation scheme and the correctness of some application built relying upon process isolation. Both require a clear and unambiguous (formal) specification and a proof that an implementation meets this specification. Some proofs have been done on specific instances of this problem; Bevier [11], for example, gives a specification for process isolation on a particular target machine. However, what is really needed is a *generic* axiomatization of memory and memory management, of process isolation, and of the other basic mechanisms of hardware support for secure systems in particular and operating systems in general, rather than treatments that focus upon specific security models or processor architectures.<sup>11</sup> Such notions as memory management are the underlying abstractions upon which security mechanisms rely and should be formally viewed as such. [67]

We are not aware of a rigorous generic axiomatization of features such as memory protection, though Popek and Goldberg [109] sketched the outlines of such a project in 1974. Such a presentation, submitted to the social process, would provide a convincing specification as a basis for formal analysis and a viable target for implementations. Landwehr and Carroll [77] provide a start toward a security-specific version of such a specification by enumerating logical requirements on an abstract machine. Their presentation falls short of a formal treatment of this issue but is a step in the right direction. It is rather surprising that more effort has not been expended in this area, given the importance of these issues for system correctness and system security. Such a formal treatment is outside the range of the current report, but is a potentially productive area for future research. This is a challenging research area and one calling for increased collaboration between the hardware verification and security communities.

# 3. Aspects of Hardware Support for Secure Systems

Various fairly standard features of microprocessors have traditionally been regarded as supportive of system security; these include memory protection schemes, support for interprocess communication, and support for multiple execution domains.

It is fortunate that most of the hardware mechanisms needed to implement a secure system are also required by conventional operating systems; otherwise, there would be little hope of seeing these features on today's machines. This is not a coincidence: good protection features are essential to an efficient and reliable operating system. [47]

This section describes a number of such features, the way in which they support system security, and the implications for verified secure systems. We make no claim that our list is complete in any sense. Almost any hardware feature accessible to an end user could have potential use in some covert activity. This motivated our insistence in Section 2.2 that our formal system model be as inclusive as possible. We focus

<sup>&</sup>lt;sup>9</sup>Rushby [114] is the source of this list.

<sup>&</sup>lt;sup>10</sup>Bevier [10] is the only attempt of which we are aware to model and prove the correctness of a process isolation scheme down to the machine code level.

<sup>&</sup>lt;sup>11</sup>See [70] for some work on the generic specification of hardware.

on aspects of hardware that seem particularly relevant from a security perspective. There is no special order to the list of subtopics in this section. In the Appendix we give a prioritized list of hardware features which should be examined in a secure system development effort.

Notice that most of the features described in this section could be implemented in hardware, in firmware, or in software. Our choice to describe them as "hardware support for secure systems" is driven by the fact that they are usually implemented in hardware, chiefly to enhance system performance and to yield a cleaner and better structured architecture. There is no reason to believe that modeling techniques would be significantly different for a hardware implementation than for a software implementation.

## 3.1 Influence of System Architecture

One key factor influencing the verifiability of any piece of complex hardware is the structure of the architecture. It is well known from software verification experience that a well-structured program is more likely to be comprehensible and easy to verify than a poorly-structured program. The lessons of modularity and structured design arose in the same environments as formal program analysis techniques. These same lessons apply to hardware. Modular design and good engineering practice lead to hardware designs that are accessible to formal techniques.

An architecture that matches in structure the systems that are built upon it can greatly enhance their verifiability. Dijkstra [38] illustrated the benefits of a layered architecture for operating system design. Similar benefits accrue for a hardware architecture. For example, the hardware of the PDP 11/45 was layered to support three levels: kernel, supervisor, and user. A protection system that matches the hardware layering closely gains in comprehensibility and verifiability because the mechanisms in the protection system match closely those of the machine. Many researchers have recognized the benefits of localizing the protection functionality of the machine into a small *kernel*, the lowest level of the system layering. Popek and Kline [110] assert that the kernel should "contain the security relevant portions of the operating system primitive, and nothing else." Spier [126] wants the kernel to contain only the interrupt and I/O handling routines, CPU multiplexor and scheduler, and memory management routines. "Kernelizing" the protection mechanisms isolates them from the influences of other hardware and software. In Section 3.3-E we discuss the notion of a reference monitor, one instantiation of kernelized protection.

One very significant benefit that can be gained by careful structuring of a system architecture is that the amount of verification required to gain a particular level of assurance can be reduced. High levels of assurance come at a price; formal verification techniques tend to be expensive and difficult to apply. Consequently, there is a strong economic incentive to reduce the percentage of system functionality that must be verified. This is much of the reason for the process discussed in Section 2.2 of delimiting the security perimeter, i.e., the goal is to exclude as much as possible of the system from formal analysis. The architecture of a secure system strongly influences how much of the system needs to be verified. For example, as we will discuss in Section 3.5 smart I/O device controllers can be a security risk and must be either trusted or verified on conventional secure system designs. This need was avoided on LOCK [119] by segregating nonprimary memory and communications ports from the CPU and main memory by a bulk encryption device. The result is that:

- contents of secondary memory are encrypted and need not be physically secured; and,

- device controllers need not be trusted, allowing the use of commodity controllers.

The result is a significant reduction in verification effort with no loss in system assurance.

Other architectures which use physical arrangement of system components to gain security and reduce the need for verification are discussed below in Section 3.3-E(2).

## **3.2 Memory Protection**

One of the most crucial aspects of hardware support for secure system development is the ability to define distinct memory spaces for separate users/processes. Access to memory is usually restricted on modern processors by some scheme of implementing *virtual memory* [56, 109]. There are myriad variants of virtual memory management; but all have one or more of the following goals:

- 1. they isolate process address spaces;

- 2. they permit a process to have a larger address space than available main store;

- 3. they free the user from having to deal with storage management; and,

- 4. they utilize main store efficiently by maintaining unused portions of program and data on secondary storage until needed.

Virtual memory management schemes are aimed at high efficiency of resource utilization and satisfactory performance. The economies of computing have changed over the years as hardware (and particularly memory) costs have fallen, but these requirements remain.

Typical memory management schemes involve mapping user-supplied (virtual) addresses to physical addresses via some virtual memory mapping. This process is typically supported by hardware using index registers and address registers. This translation is transparent to the programmer. See any book on machine architecture (such as [63]) for further discussion of the details of memory management schemes.

Some early machines implementing virtual memory required that a process' address space lie in contiguous physical memory; physical addresses are computed from virtual addresses by adding an offset. This is simple to implement with base and bounds registers storing the limits of the accessible region. This scheme requires that all accesses check these limits and that the registers not be accessible to the user program.

Requiring contiguous memory leads to storage *fragmentation*. To avoid this, we can divide memory into fixed-size pages and allocate to each process either a fixed or variable number of pages. In *demand paging* schemes, pages are stored on secondary storage until required. This permits a process to have a virtual address space larger than the main store. To be efficient demand paging requires hardware support in the form of hardware mapping registers and page descriptors and efficient support for swapping pages in from secondary store.

Some systems add an alternative or an additional layer of memory division in the form of *segments*. The segments are typically variable sized memory partitions that may hold distinct objects or may be merely an extra layer of memory partitioning. A translation mechanism for virtual memory that accommodates variable-size segments on top of demand paging requires an additional level of memory descriptors. There will usually be hardware support for this mapping.

Virtual memory management is an obvious mechanism for controlling the access of users to memory objects. A crude scheme is to divide memory into user and system segments that are separately protected. The user may not write into the system segment. Functionality of the operating system is accessible only via special entry points. If this partitioning is static, this scheme is easy to enforce with hardware.

As we suggested in Section 2.4 above, virtual memory mechanisms and the hardware support for them are obvious candidates for formal scrutiny. They provide foundation for much secure system development effort but have been largely neglected in formal efforts to assure the correct functioning of such systems.

## **3.3 Execution Domains**

Since security implies the isolation of information or other resources from unauthorized access, several authors such as Landwehr and Carroll [77] take as the key abstraction within a secure system the notion of a protection *domain*—''a set of information and authorizations for the manipulation of that information within a computer system.'' A domain is essentially the name/value space accessible to a particular user. With respect to security models, a domain may be identified with a *subject* and its associated access rights to objects in the systems. Important factors to consider in implementation of protection domains are:

- how the protection structures of the model map onto those provided by the machine architecture;

- how domains are initialized;

- how users are linked to domains;

- how communication occurs between domains; and,

- how domains are isolated from one another.

The principal concern of secure system developers is providing required domain isolation while still providing appropriate communication between domains and efficient provision of the other services of the machine such as creation and initialization.

## **3.3-A Processes**

Within a given implementation, a protection domain may be identified with a process, with an abstract data type, or with an object (in an object oriented system). At the hardware level, it is often a *process* that is associated with a protected domain. This is natural because many conventional architectures provide fairly extensive hardware support for processes. Consequently, the hardware process support is often relied upon by the operating system as a foundation for the security mechanisms.

Almost all security models take the notion of "per-process" virtual environments as primitive—so primitive, indeed, that this notion is generally unstated and unregarded. The key assumption is that the active entities of a security model ("subjects" in security jargon) are assumed to be fundamentally distinct and distinguishable from each other. Now, in a concrete system design or implementation, the subjects of the model are generally associated with "processes" provided by the operating system nucleus and in order for the security model to be an accurate description of the concrete system, it is therefore necessary to ensure that the processes of the concrete system are indeed distinct and distinguishable—that is to say, each process must have its own "virtual" environment. [114]

Thus, the machine facilities that support the per-process virtual environments and keep them separate are often crucial to the maintenance of system security.

The main required support for processes is the ability to switch from one process to another. This requires a mechanism for storing enough process state so that a suspended process can be re-dispatched. For a multi-level secure system, if processes are associated with subjects, there are likely to be numerous processes and the need for frequent process switching. This calls for an efficient interprocess switching mechanism. This mechanism must store the process internal state including at least the program counter and user-visible registers. In addition, there must be a mechanism for preserving the user-addressable memory. The mechanism for this depends upon the particular memory management strategy of the machine.

## **3.3-B** Initialization

Landwehr and Carroll point out the need for reliable system initialization in secure system operation.

The ability to define and separate domains in a machine will be of little use unless there is a reliable way of getting started. This implies that the logical structure of the system must allow the programmer to distinguish the occurrence of a system initialization event and to establish a consistent state for the system—a state from which additional domains can be initiated and separated. [77]

From a modeling standpoint, initialization is crucial. Security properties are often stated as *invariants* on the system state; the system remains secure if each transition in the system is security preserving.<sup>12</sup> However, the implicit induction here requires that the system be initially secure. Also, because of the need

<sup>&</sup>lt;sup>12</sup>See [89] for discussion on some of the subtleties of this approach to security.

at start-up to establish all of the security mechanism including the tables that contain access control information, the initialization mechanism must have privileged functionality that likely is not under the mediation of the security control mechanisms.<sup>13</sup> Thus, special care is needed in the initialization of the system to preserve security.

Hardware can contribute to secure system initialization in a variety of ways. Secure initialization routines can be isolated from other portions of the memory by using virtual memory techniques as discussed in the previous section, by storing security tables in ROM, or having by a processor dedicated to initialization. Via these techniques it is possible to ensure that a secure initial state is established. LOCK [119], for example, avoids the problem of having to bypass the security controls during initialization by having the entire security kernel segregated on a separate processor with its own memory.

Initialization can be a particularly difficult challenge when reasoning formally about hardware. For example, a recent proof about a hardware reset mechanism [72] found considerable difficulty in proving that a microprocessor reaches a "safe" and predictable state following a reset. Such issues are often neglected in formal approaches to hardware correctness.

## **3.3-C** Linking Users with Domains

It is always necessary to associate the actions of an active entity (subject/process/domain) in a secure computing system with an individual user. Thus, it is necessary to have a reliable way to link users with domains, both when the domains are created and as they execute. Such accountability provides a strong deterrent as well as provides a way to diagnose security breaches *post hoc* through audit procedures.

Most systems implement a password mechanism to prevent unauthorized persons from gaining access. A password mechanism can also prevent users who are already logged in from performing unauthorized activities, such as accessing restricted directories and gaining access to more privileged "modes" such as super-user mode on Unix.<sup>14</sup> The user must authenticate the machine as well, to avoid so-called "spoofing" attacks in which a program masquerades as the login procedure on the target machine until a user divulges his password. Two way authentication can occur via a series of questions and answers. Hardware mechanisms that can assist in this process include devices in which the user uses some physical device such as a magnetic-striped key card rather than a typed identification. Such a login scheme for mutual identification of user and system is described in [43].

After access to the machine is obtained, the integrity of the connection must be maintained. This can be accomplished by periodically reauthenticating the user to ensure that the user has not changed and logging out users who have been inactive for some period of time. A hardware watchdog timer can be useful in implementing such schemes.

Related to the issue of linking users with domains is the question of what *audit facilities* are provided by the machine. Audit facilities are intended to record occurrences of selected system activities so that actual or attempted security violations can be attributed to particular users. An audit facility has the goals of allowing reconstruction of events leading up to and including system violations and allowing monitoring of user actions so that attempts to violate system security may be perceived and acted upon before a violation occurs. [92, 105]

There are two main issues related to audit data: data must be adequate to meet the audit goals of the system, and both the audit mechanism and storage of audit data must be tamperproof. Selection of auditable system activities is an art. Too much audit data can swamp the system and make extracting relevant information

<sup>&</sup>lt;sup>13</sup>This is an instance of a more general problem—most security models are *too strong*. To operate well, most systems require functionality that is formally in violation of the security policy. For example, it may occasionally be necessary to downgrade documents, in violation of the proscription of downward flow of information (\*-property). A general utility such as a printer demon may need to read and write documents at all levels, in violation of most security models. The solution is typically to have a collection of "trusted processes" which are privileged to violate the security policy in specific ways.

<sup>&</sup>lt;sup>14</sup>See [96] for an interesting history of the password security mechanisms on Unix.

very difficult; too little audit data may allow a clever perpetrator to escape detection. Selection of auditable events is a system design rather than a hardware issue. However, hardware can be used to make recording audit data less obtrusive. In a system with hardware support for kernel calls, the hardware can also write the relevant audit data. This is generally much more efficient than software monitoring of system behavior. Moreover, it may add additional assurance that the mechanism is tamper resistant. Previously recorded audit data can be protected by the standard protection mechanisms of the system. However, for purposes of reconstructing *past* security violations, there is no reason to assume that audit data has not be compromised along with other system resources, if all were protected by the same mechanisms. Some system such as LOCK [119] store audit data on a write-once medium. This provides additional assurance of tamper resistance.

## 3.3-D Communication Between Domains

Communication between processes/domains is critical to security, since the entire purpose of a secure system is to control communication between subjects. Again, the support for and protection of communication between domains may not match the required level of protection called for in the security model. For example, if a hardware supported domain cuts across logical subject boundaries or if there is more than one level subject within the domain, communication must occur in a manner consistent with the policy.

Information can pass from domain to domain in a number of ways:

- one domain may request service from another and transfer control to it;

- two domains may share memory;

- domains may pass messages.

There are various ways in which hardware can support the restriction of interdomain requests. Spier [125] outlines a protection scheme that depends on "the availability of dedicated supporting protective hardware...where an inter-domain call is just as efficient as a common intra-domain call." Required is a hardware return stack inaccessible to the user program and paging tables. On LOCK all permissible domain transitions for any subject are encoded in the Domain Transition Table (DTT). Hardware mechanisms support the checking of this table whenever an attempt is made to move from one domain to another. In some ring architectures, a domain change can only occur by transferring control through a **call** instruction to prescribed locations in special *gate segments* that are designated as entry points to inner rings [47]. Such mechanisms allow a protected domain to control its invocation.

Entering a less privileged domain requires that the arguments passed be checked to prohibit the calling process from illegally obtaining access to restricted data. Most such checks are performed by software. Hardware can help in address validation to ensure that passed pointers refer to legitimate locations within the user space. See [47] for an extended description of the various types of pointer validation and hardware supported schemes for carrying them out.

Other systems implement interprocess communication via shared memory or message passing. These approaches to communication are typically controlled by the assignment of *access rights* restricting what privileges any particular domain has to shared memory or to which other domains a message may be sent. These topics are covered in the following subsection.

## **3.3-E** Isolation of Domains

Undoubtedly the most crucial function of a secure system is to enforce (partial) isolation of domains. Of course, a domain cannot be entirely isolated or it could never interact with its environment or communicate its results to the external world. However, the communication between domain must be constrained in such a way that only information flow allowed by the security policy is allowed in the system. This means that all other information flows must be prohibited.

Rushby and Randell [116] note that there are conceptually four ways to provide domain/process separation: temporally, physically, cryptographically, or logically. These methods of domain separation can be realized physically in a number of ways.

#### **3.3-E(1)** Temporal Isolation of Domains.

In the absence of any more sophisticated separation mechanisms, early machines utilized the *temporal* isolation of domains. That is, any user would have access to the complete memory space of the machine, but separate users were isolated in time, since only one user has access to the machine at a given time. Such machines either had no memory management software (eg. the IBM 1130 and Elliott 905) or a simple resident executive to control sequencing (eg. the IBM 7090, and scientific configurations of the Elliott 4130 and ICL 1900). On these machines, there is no sharing of resources among users. The special hardware required to implement this is only a fixed protected area of memory for the resident. User programs did not have access to this protected region to prevent corruption of the executive. This protection scheme is particularly easy to implement and to prove correct.

Another style of temporal isolation is enforced in some multi-user settings where the machine is utilized in "single-level mode" by groups at different security levels. After use by a high-level group, the store is "scrubbed" before the machine is turned over to a group at a different level. Security concerns arise when information on the system survives between uses. User-accessible store that has not been adequately cleansed may contain residual information that is accessible to the next user. Even if user-accessible store is cleansed, boot-strap routines, initialization software, and other system software provides a potential mechanism for preserving sensitive information from one use of the machine to the next, if the machine does not provide adequate protection of system space. Also, it is known that information can be gleaned from some physical media even after they have been logically sanitized. For example, information stored on a magnetic media can often be recovered even if it has been overwritten. Thus, tapes used for secure applications and subsequently retired must be "de-gaussed" to prevent retrieval of the stored information.

## **3.3-E(2)** Physical Isolation.

An obvious approach to maintaining isolation between processes is to schedule them on physically isolated processors with minimal and carefully controlled opportunities for communication. This approach of using distributed computing as a means of attaining security has been suggested by several authors [32, 40, 112, 116]. The underlying motivation is that "manifest physical separation is one of the simplest and most easily verifiable forms of separation" [40]. The advantage of such schemes is that all interprocess communication mechanisms are simple and explicit and there is little need to fear covert channels through the system state. However, the efficiency advantages of shared state are sacrificed.

Physical isolation is used rather heavily in cryptological equipment. Red/black separation is realized in many COMSEC applications by isolating red and black system components on separate processors with a tightly controlled bypass. The verification of such a system is described in [124].

Another use of physical isolation is to scatter resources to make an attacker's penetration of a single system component less profitable. Such a scheme is used by the SATURNE project [37]. File fragments are distributed to various storage devices to impede security penetrators.

A rather radical architectural approach using physical isolation to gain security is suggested by Davida, DeMillo, and Lipton [32]. They propose three different system architectures for which it is claimed that "the security of the total system derives from a few very simple hardware devices by socially acceptable arguments" (i.e., requiring no verification, other than the "social process" touted by the authors in another paper [33]). The basic scheme in its simplest incarnation is to segregate users at different levels on separate processors and to allow communication among processors via hardware-enforced one-way links. This structure physically enforces the information flow constraints of the model. The practicality of the scheme has apparently never been tested in practice.

With the advent of cheap yet powerful personal computers and workstations, there is an increasing tendency to return to the paradigm of single-user machines to enforce domain separation. This is a form of physical isolation. Like early machines, this obviates "internal" security mechanisms to isolate users from one another. However, networking such machines introduces many of the security concerns of multi-user computing on a single machine.

#### **3.3-E(3)** Cryptographic Isolation.

An adjunct to other approaches to security is to encrypt sensitive data. Encryption of secure data has the effect of reducing its effective information content. However, the effectiveness of encryption as a protection scheme is directly related to the "strength" of the encryption scheme and to the security of the key. Details of various encryption schemes are well described elsewhere [35].

Encryption is not a complete solution since the key data must be protected and potentially distributed. However, encryption can be useful in protecting data in remote storage or in transit. Remote access systems are particularly vulnerable to penetration. Not only is the computer susceptible to attack; transmissions between the computer and the remote user can be intercepted or subverted. End-to-end encryption, as is used in modern secure telephone technology, can give protection in remote access systems.

LOCK is an example of a secure system which uses cryptographic techniques in a variety of ways. As we saw in Section 3.1, LOCK uses bulk encryption to store secure data during periods of time when no program needs to access it. This reduces the need for physical security on the storage medium. "In addition, cryptography is used to close covert channels<sup>15</sup>, protect security-critical data bases, and defend against attacks by subverted device controller hardware and firmware." [17]

The use of cryptographic isolation may eliminate some of the verification requirements on I/O controllers and other portions of the system. However, it puts a correctness premium on the portions of the system that perform encryption and decryption. These units are often critical to system security. Yet the crypto devices are often of classified design and may be difficult to incorporate into secure systems.

Free-standing cryptographic units have been difficult to integrate, both physically and functionally, into modern computerized hosts. The classified nature of the products has often imposed physical security constraints which are incompatible with operational needs. The 'communications-only' bias of the products has inhibited cryptographic solutions to computer security problems, such as authentication of critical but forgeable user/computer dialogues and the security of classified information on removable media. [74]