# A Verified OS Kernel. Now What?

Australian Government

Department of Communications, Information Technology and the Arts

Australian Research Council

**NICTA Partners**

# The Team

# The Team

#

1 microkernel

8,700 lines of C

0 bugs\*

qed

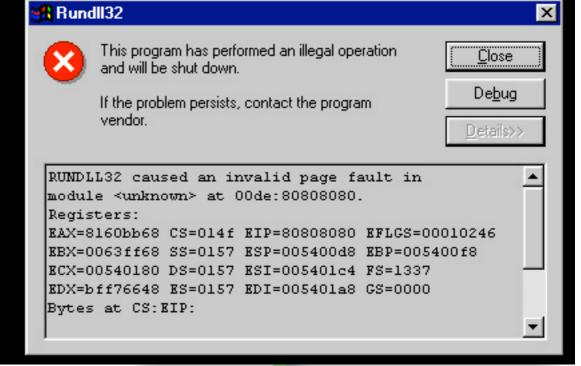

#### Windows

An exception 06 has occured at 0028:C11B3ADC in VxD DiskTSD(03) + 00001660. This was called from 0028:C11B40C8 in VxD voltrack(04) + 00000000. It may be possible to continue normally.

- Press any key to attempt to continue.

- Press CTRL+ALT+RESET to restart your computer. You will lose any unsaved information in all applications.

Press any key to continue

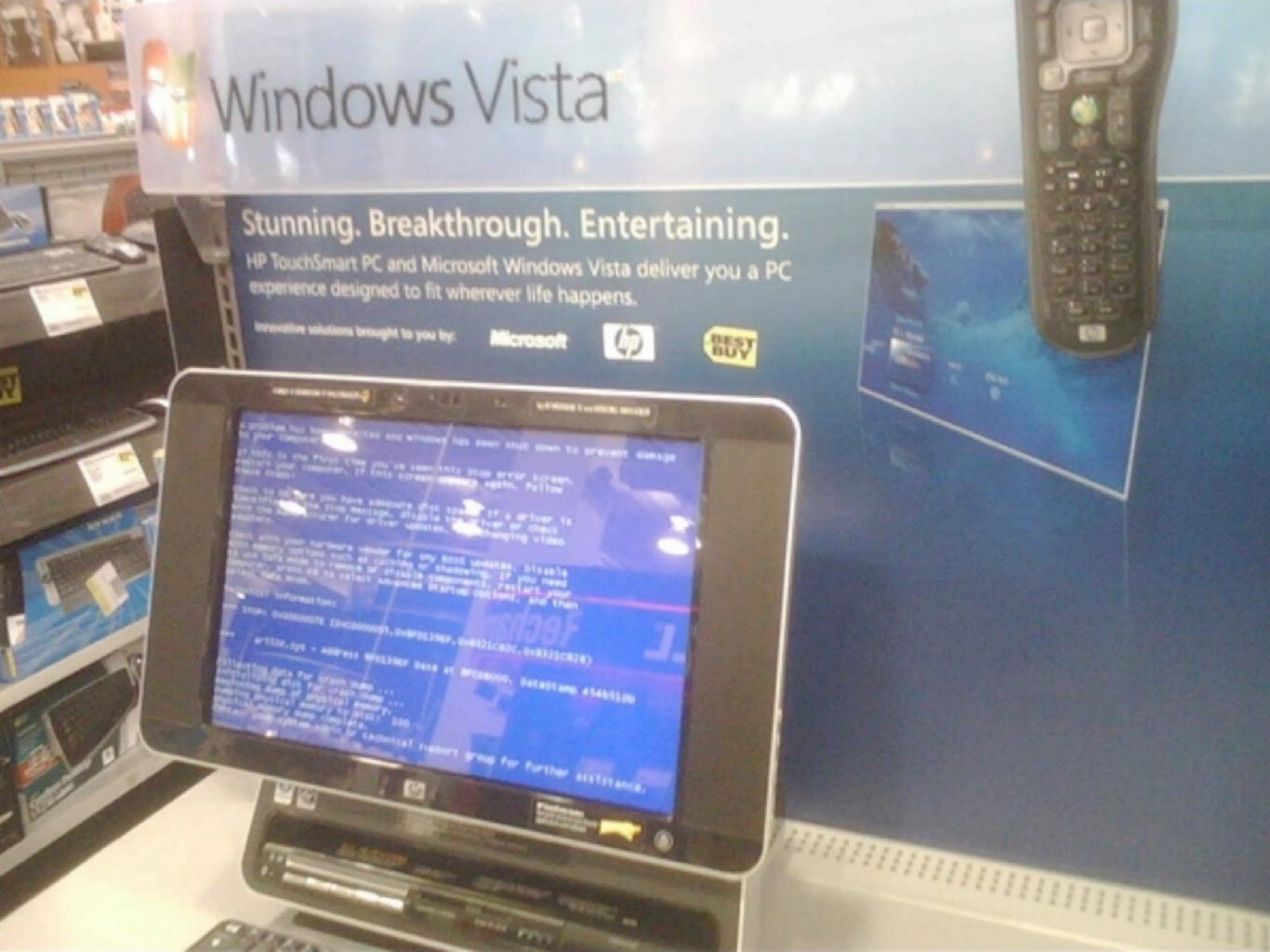

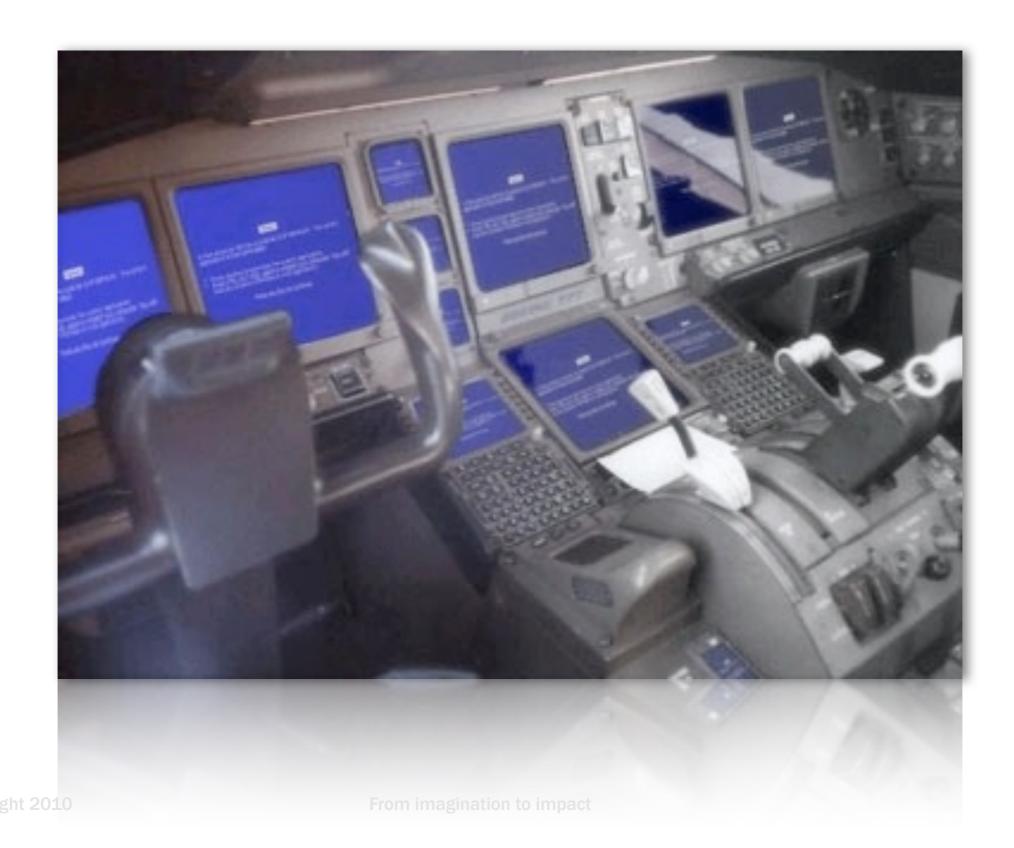

# The Problem

7

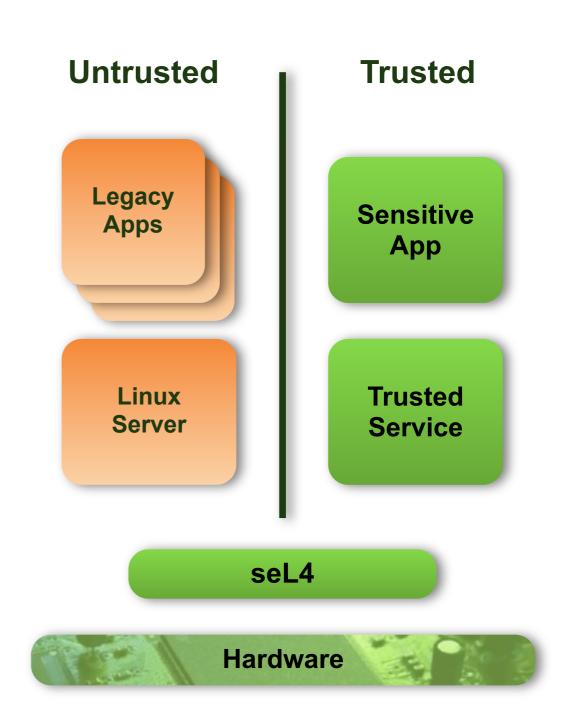

## **Small Kernels**

#### **Small trustworthy foundation**

- hypervisor, microkernel, nano-kernel, virtual machine, separation kernel, exokernel ...

- High assurance components in presence of other components

#### seL4 API:

- IPC

- Threads

- VM

- IRQ

- Capabilities

## **Small Kernels**

#### **Small trustworthy foundation**

- hypervisor, microkernel, nano-kernel, virtual machine, separation kernel, exokernel ...

- High assurance components in presence of other components

#### seL4 API:

- IPC

- Threads

- VM

- IRQ

- Capabilities

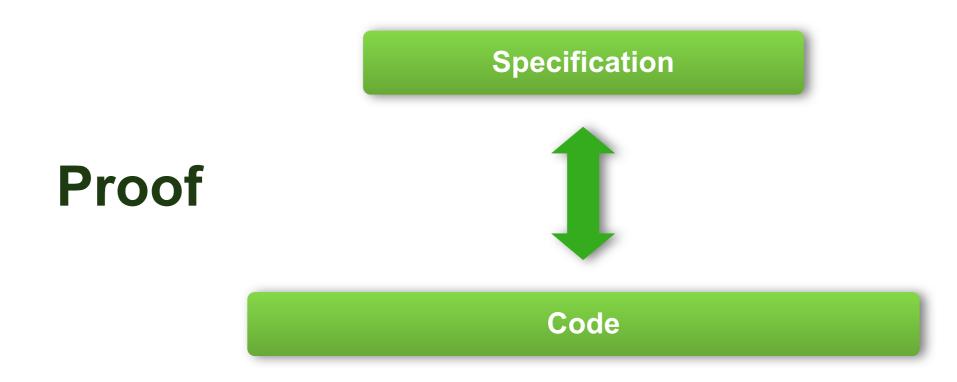

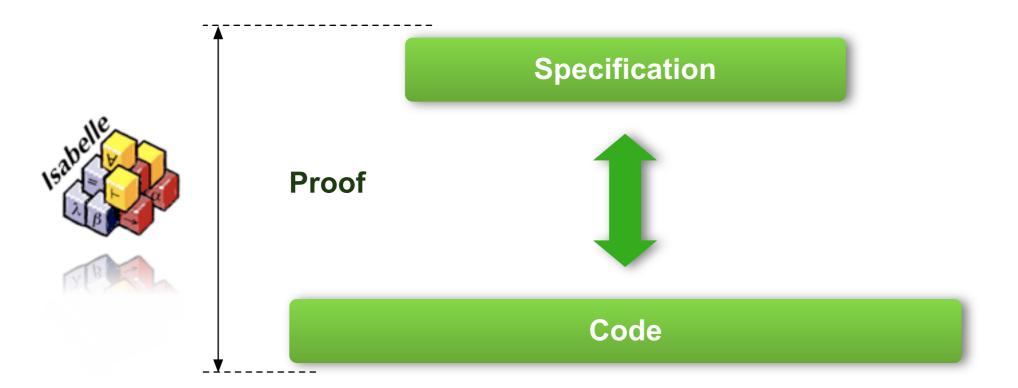

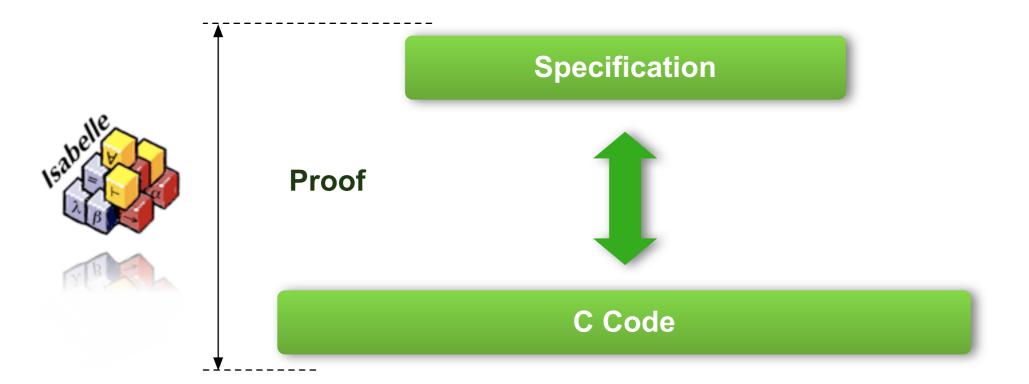

# The Proof

# The Proof

# **Functional Correctness**

## **Functional Correctness**

# What

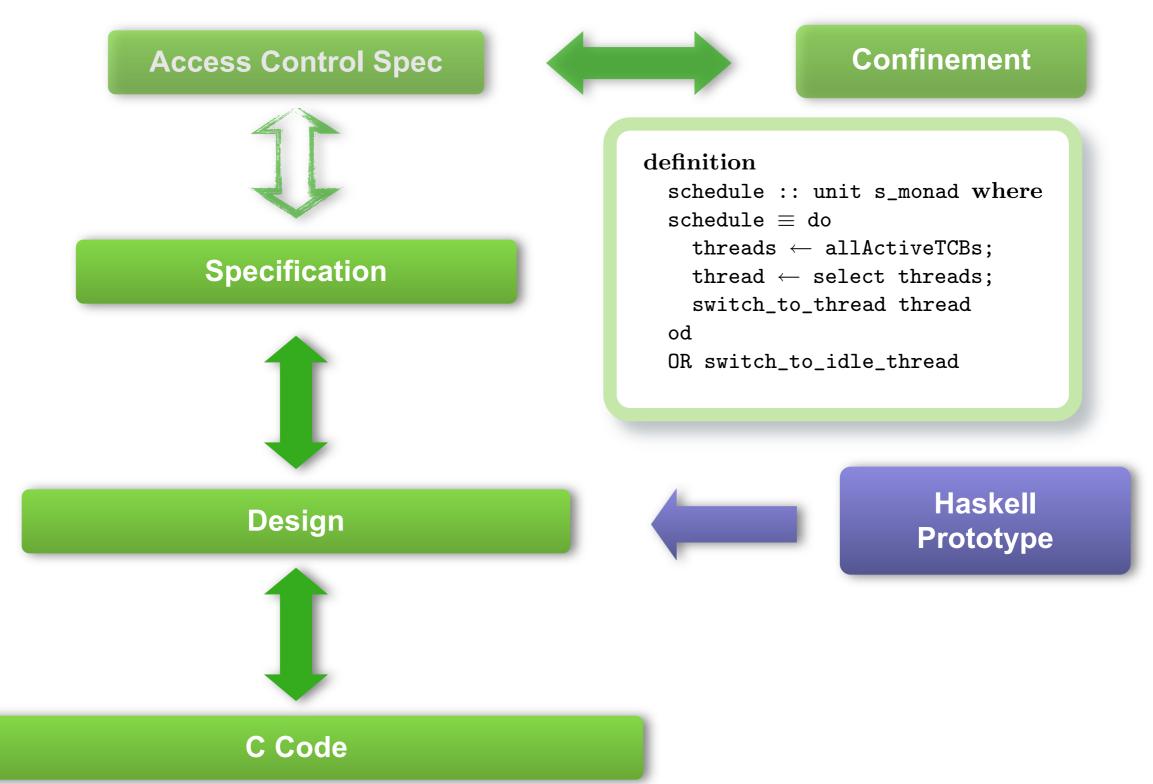

**Specification**

Code

#### definition

```

schedule :: unit s_monad where

schedule \equiv do

threads \leftarrow allActiveTCBs;

thread \leftarrow select threads;

switch_to_thread thread

od

OR switch_to_idle_thread

```

### **Functional Correctness**

# What

**Specification**

```

definition

schedule :: unit s_monad where

schedule ≡ do

threads ← allActiveTCBs;

thread ← select threads;

switch_to_thread thread

od

OR switch_to_idle_thread

```

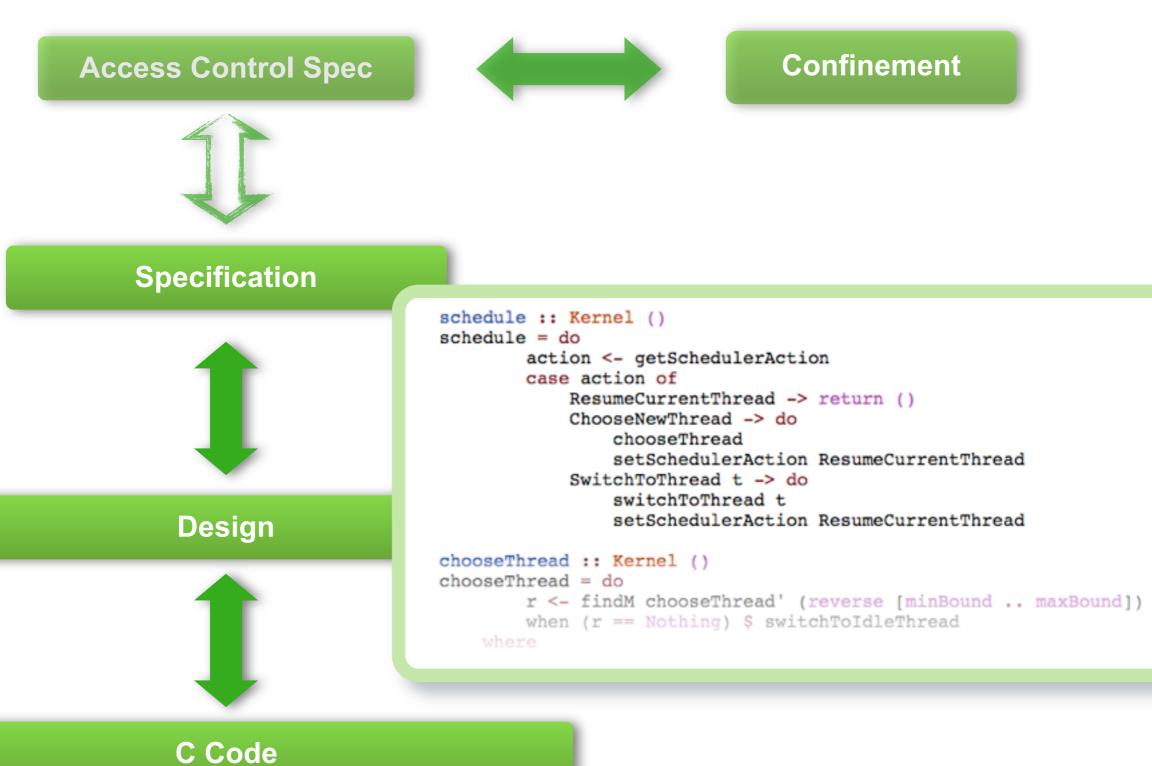

## **Proof**

How

```

void

schedule(void) {

switch ((word t)ksSchedulerAction) {

case (word_t)SchedulerAction ResumeCurrentThread:

break;

case (word t)SchedulerAction ChooseNewThread:

chooseThread();

ksSchedulerAction = SchedulerAction ResumeCurrentThread;

break;

default: /* SwitchToThread */

switchToThread(ksSchedulerAction);

ksSchedulerAction = SchedulerAction ResumeCurrentThread;

break;

void

chooseThread(void) {

prio t prio;

tcb t *thread, *next;

```

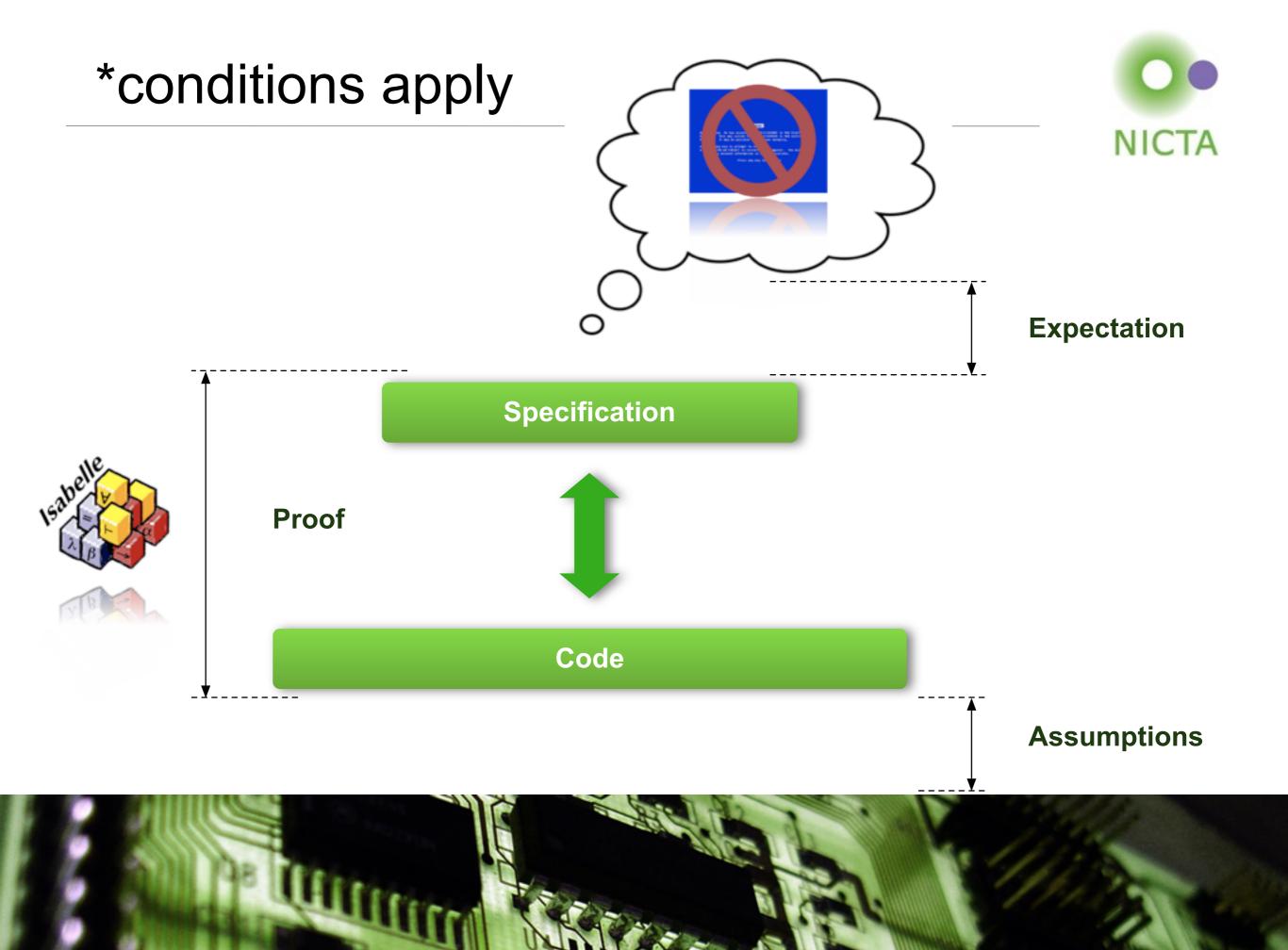

# \*conditions apply

# \*conditions apply

#### **Assume correct:**

- compiler + linker (wrt. C op-sem)

- assembly code (600 loc)

- hardware (ARMv6)

- cache and TLB management

- boot code (1,200 loc)

**Assumptions**

#### **Execution always defined:**

- no null pointer de-reference

- no buffer overflows

- no code injection

- no memory leaks/out of kernel memory

- no div by zero, no undefined shift

- no undefined execution

- no infinite loops/recursion

#### Not implied:

- "secure" (define secure)

- zero bugs from expectation to physical world

- covert channel analysis

In association with

#### **Execution always defined:**

- no null pointer de-reference

- no buffer overflows

- no code injection

- no memory leaks/out of kernel me

- no div by zero, no undefined shift

- no undefined execution

- no infinite loops/recursion

# 14 August 2009, 12:14 « previous | next » Critical vulnerability in the Linux kernel affects all

versions since 2001

The H open source

Last 7 days News Archive Features Forums Newsletter RSS

Google security specialists Tavis Ormandy and Julien Tiennes report that a critical security vulnerability in the <u>Linux kernel</u> affects all versions of 2.4 and 2.6 since 2001, on all architectures. The vulnerability enables users with limited rights to get root rights on the system. The cause is a NULL pointer dereference in connection with the initialisation of sockets for rarely used protocols.

#### Not implied:

- "secure" (define secure)

- zero bugs from expectation to physical world

- covert channel analysis

security

#### NICTA

#### **Execution always defined:**

- no null pointer de-reference

- no buffer overflows

# The Tao of Windows Buffer Overflow

as taught by

DilDog

cDc Ninja Strike Force

9-dan of the Architecture

Sensei of the Undocumented Opcode

**Begin**

#### **Execution always defined:**

- no null pointer de-reference

- no buffer overflows

- no code injection

- no memory leaks/out of kernel memory

- no div by zero, no undefined shift

- no undefined execution

- no infinite loops/recursion

#### Not implied:

- "secure" (define secure)

- zero bugs from expectation to physical world

- covert channel analysis

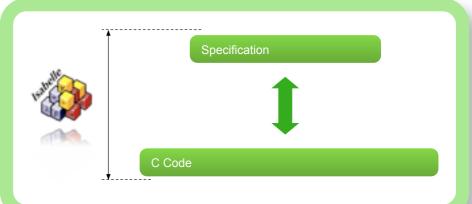

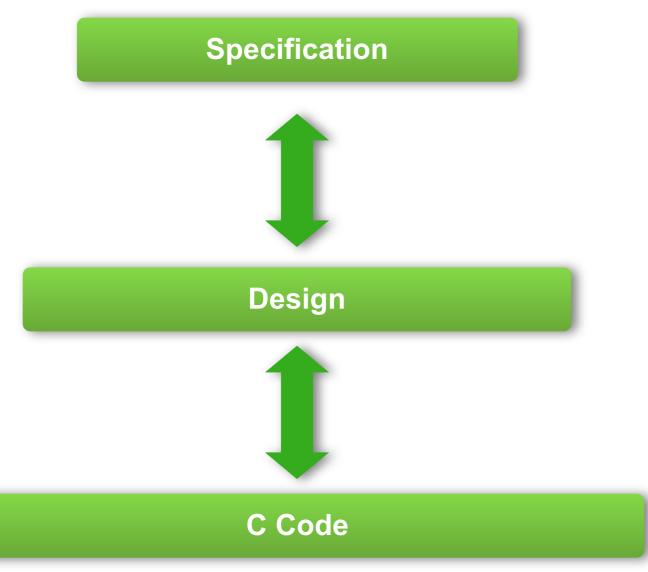

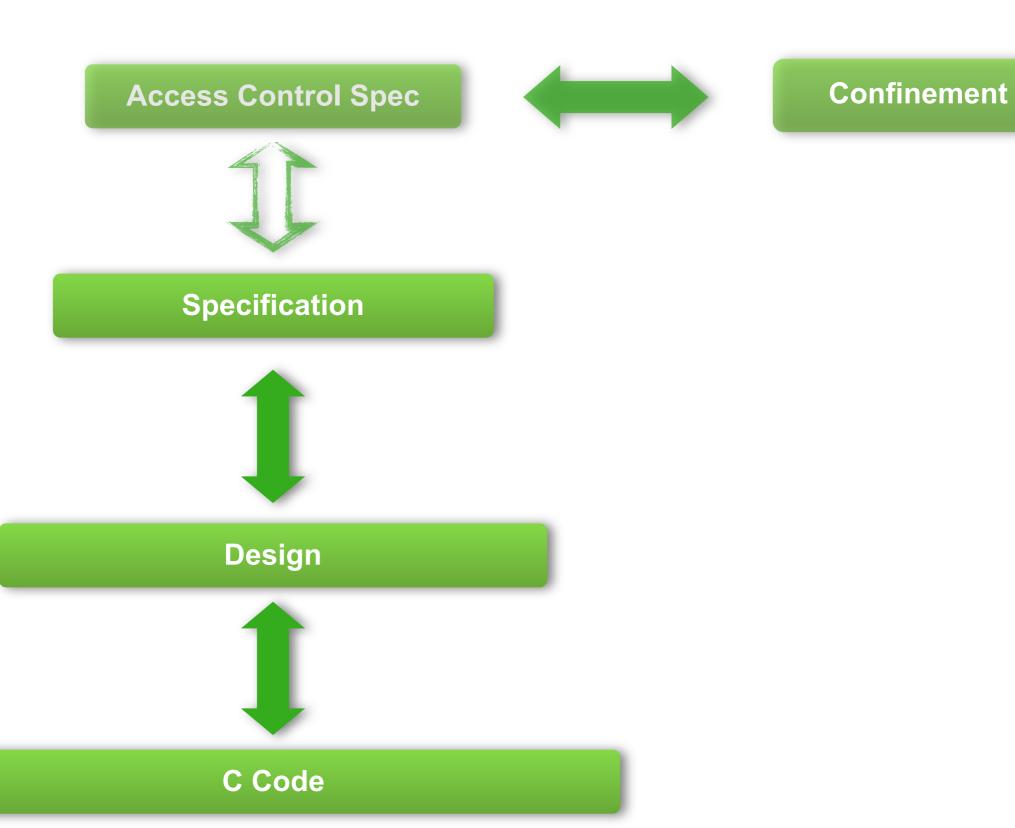

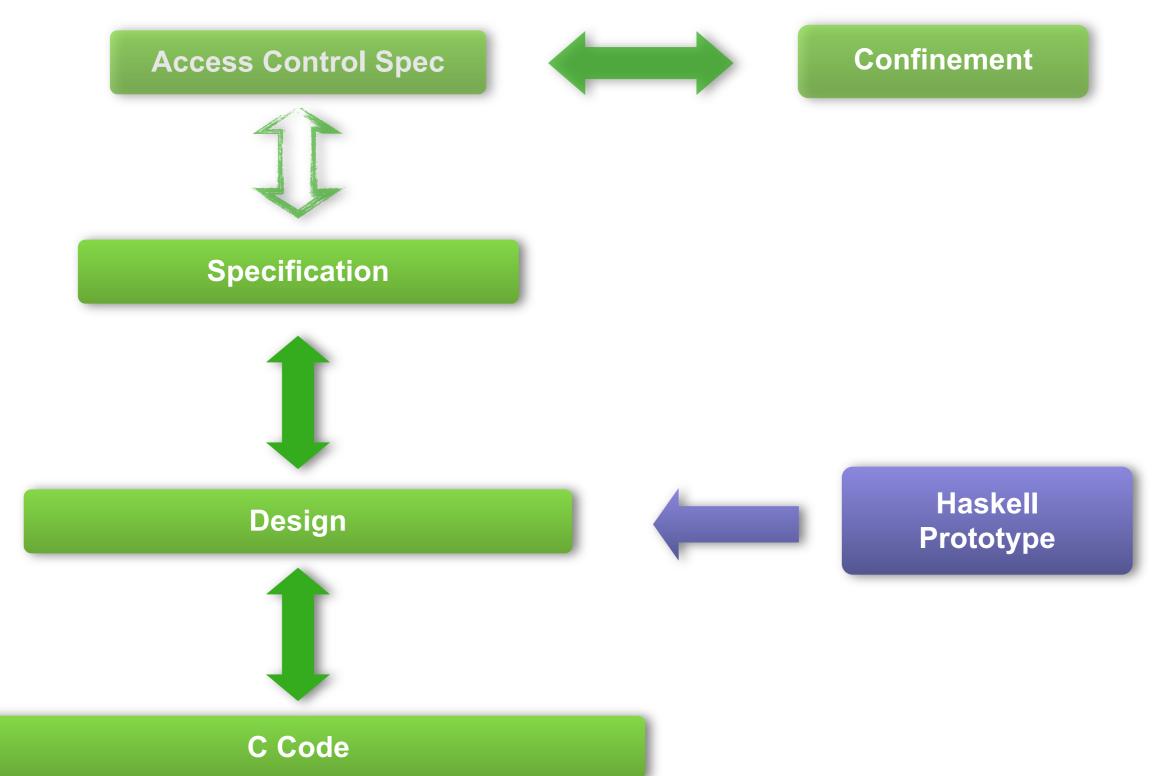

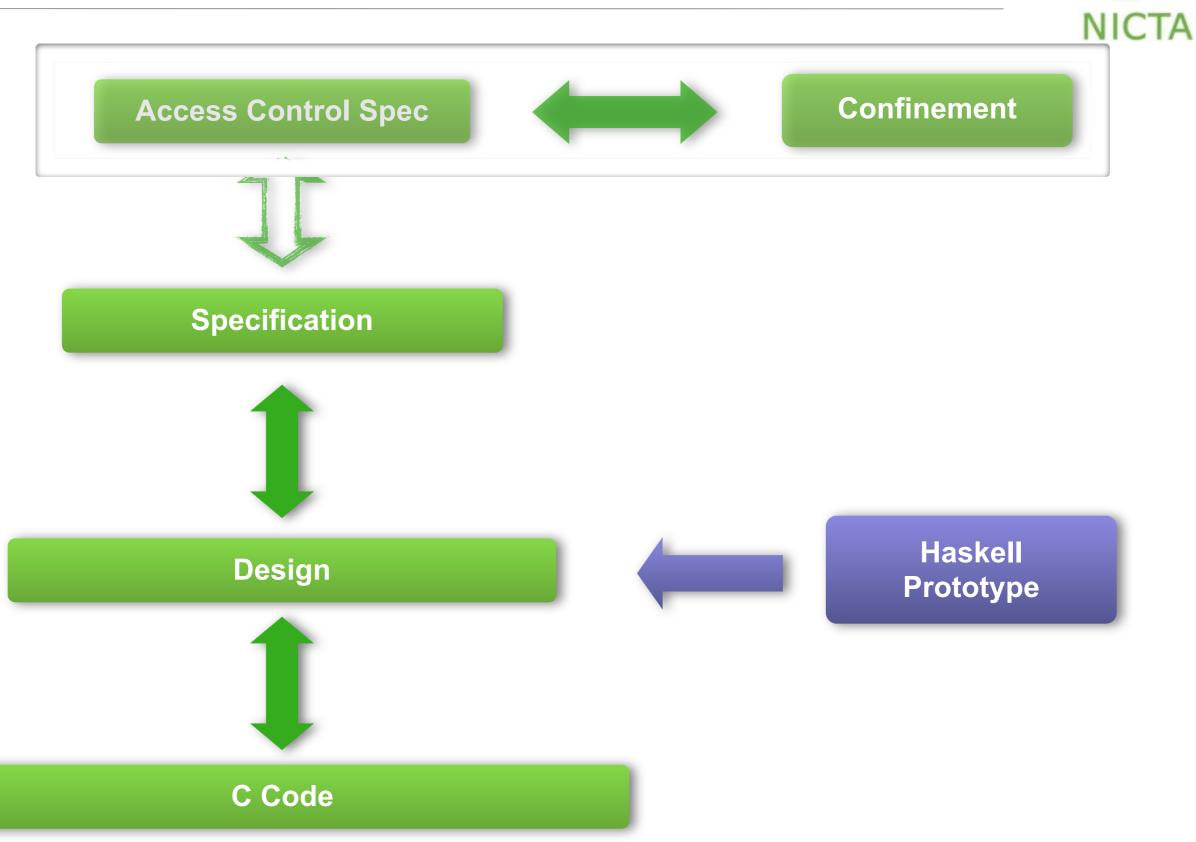

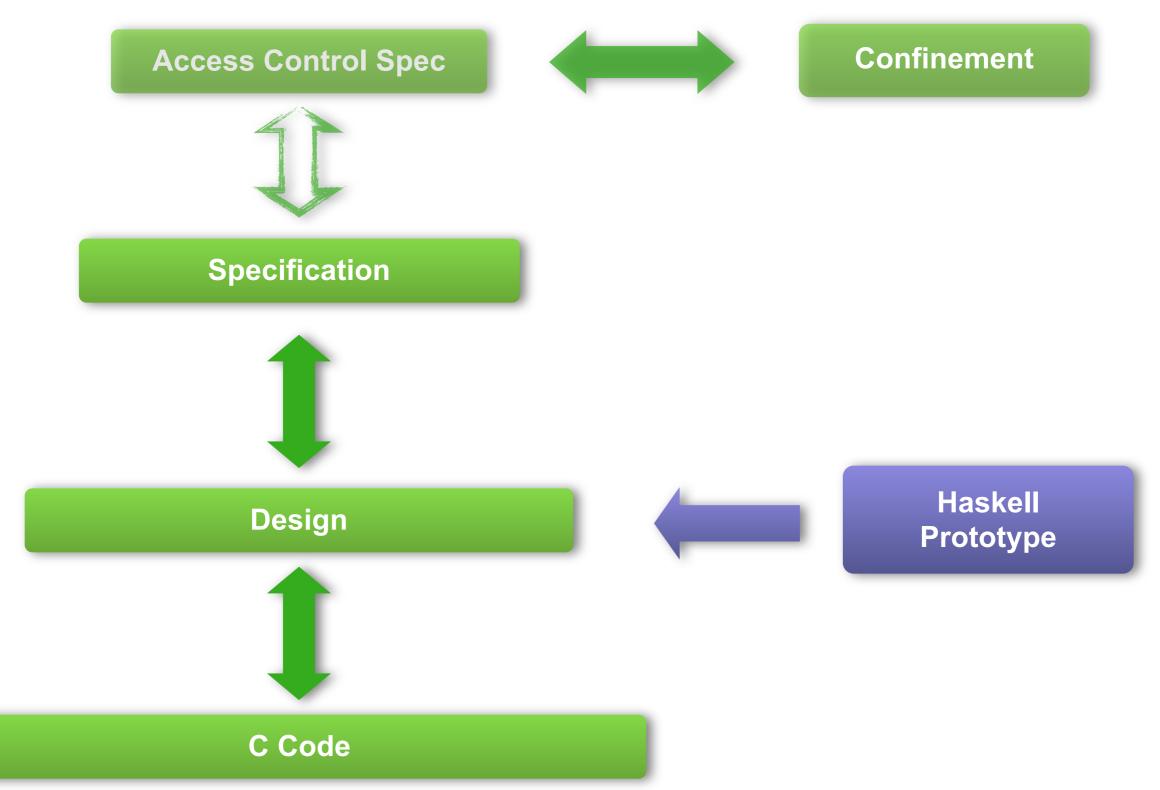

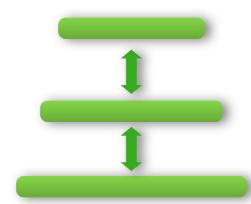

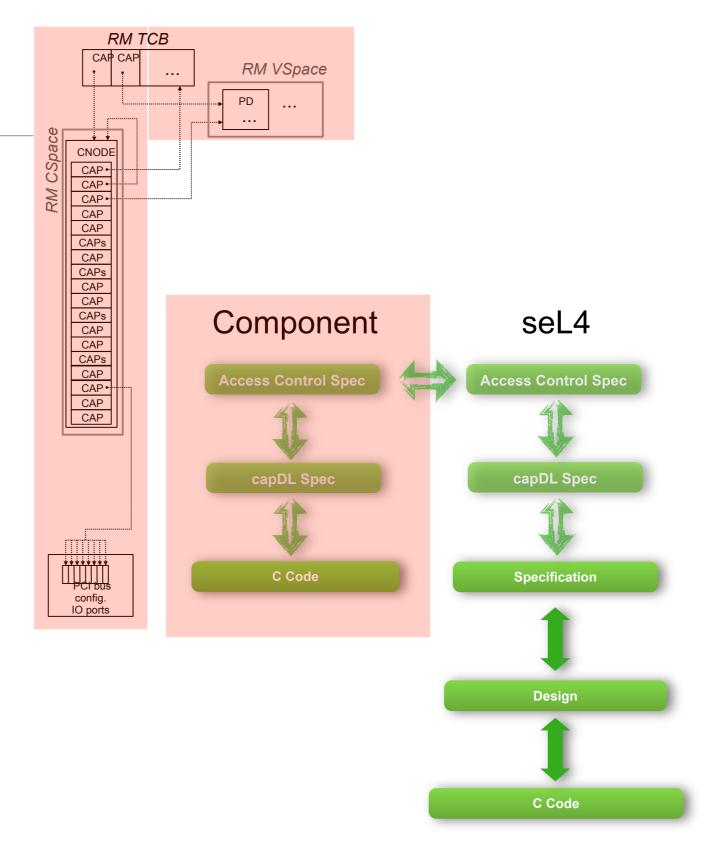

#### **Access Control Spec**

#### Confinement

#### **Specification**

#### Design

C Code

```

void

schedule(void) {

switch ((word t)ksSchedulerAction) {

case (word_t)SchedulerAction_ResumeCurrentThread:

break;

case (word t)SchedulerAction ChooseNewThread:

chooseThread();

ksSchedulerAction = SchedulerAction ResumeCurrentThread;

break;

default: /* SwitchToThread */

switchToThread(ksSchedulerAction);

ksSchedulerAction = SchedulerAction ResumeCurrentThread;

break;

void

chooseThread(void) {

prio t prio;

tcb t *thread, *next;

```

SOLIA

# Did you find any Bugs?

### **Bugs found**

• in C: 160

in design: ~150

• in spec: ~150

**460 bugs**

```

void

schedule(void) {

switch ((word t)ksSchedulerAction) {

case (word t)SchedulerAction ResumeCurrentThread:

break;

case (word t)SchedulerAction ChooseNewThread:

chooseThread();

ksSchedulerAction = SchedulerAction ResumeCurrentThread;

hrosk.

Effort

ead;

Haskell design

2 py

First C impl.

2 weeks

2 months

Debugging/Testing

void

chooseThr

prio

Kernel verification

12 py

tcb t

Formal frameworks

10 py

for(p

Total

25 py

ii(:iskunnabie(thread)) {

next = thread->tcbSchedNext;

tcbSchedDequeue(thread);

switchToThread(thread);

```

# Did you find any Bugs?

## **Bugs found**

in C: 160

in design: ~150

in spec: ~150

**460** bugs

void

schedule(void) {

void

chooseThr prio tcb t for(p

```

break;

case (word t)SchedulerAction ChooseNewThread:

chooseThread();

ksSchedulerAction = SchedulerAction ResumeCurrentThread;

```

case (word t)SchedulerAction ResumeCurrentThread:

#### **Effort**

switch ((word\_t)ksSchedulerAction) {

2 py First C impl. 2 weeks 2 months **Debugging/Testing** Kernel verification 12 py

10 py

**Total** 25 py

```

ii(:iskunnabie(thread)) {

next = thread->tcbSchedNext;

tcbSchedDequeue(thread);

switchToThread(thread);

```

Haskell design

**Formal frameworks**

ead;

# **Access Control**

# **Access Control**

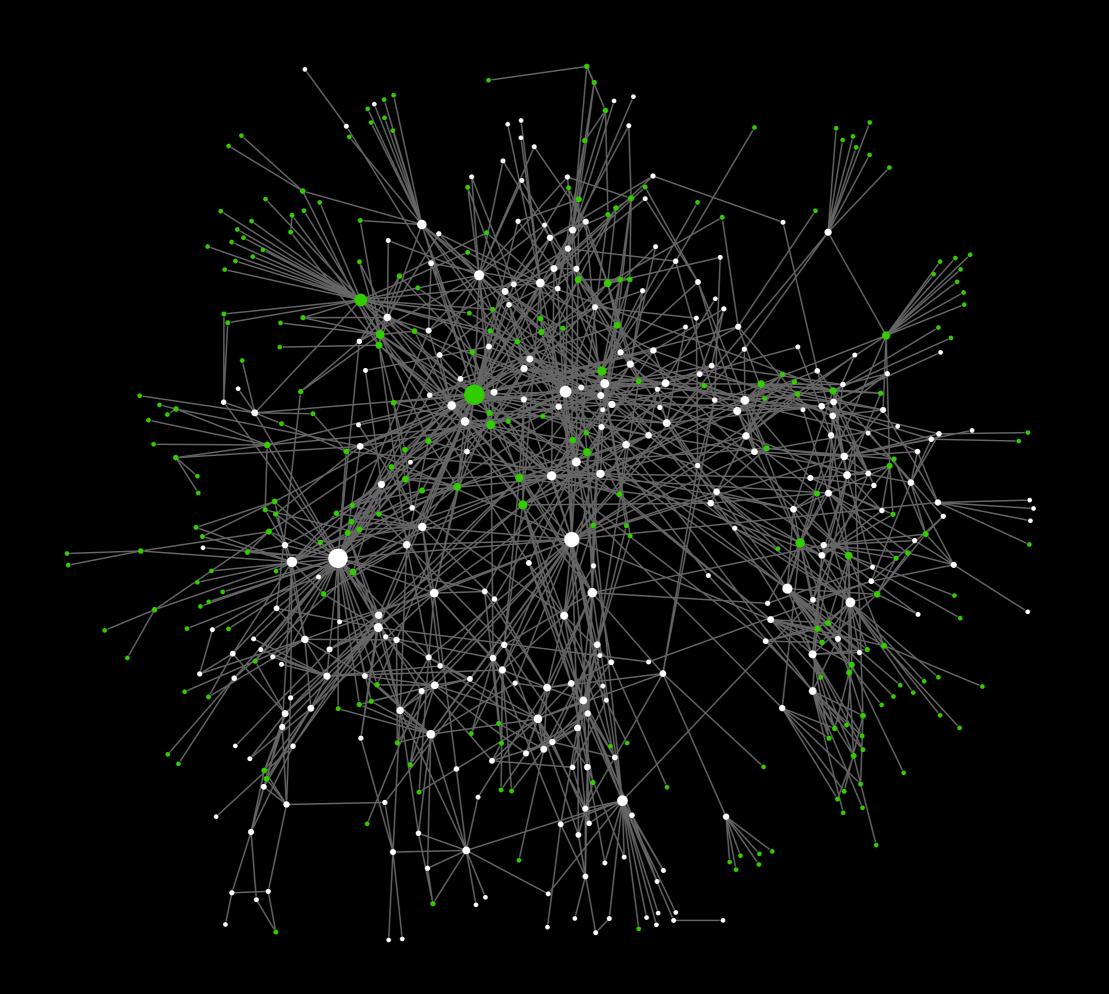

### **Proof Architecture**

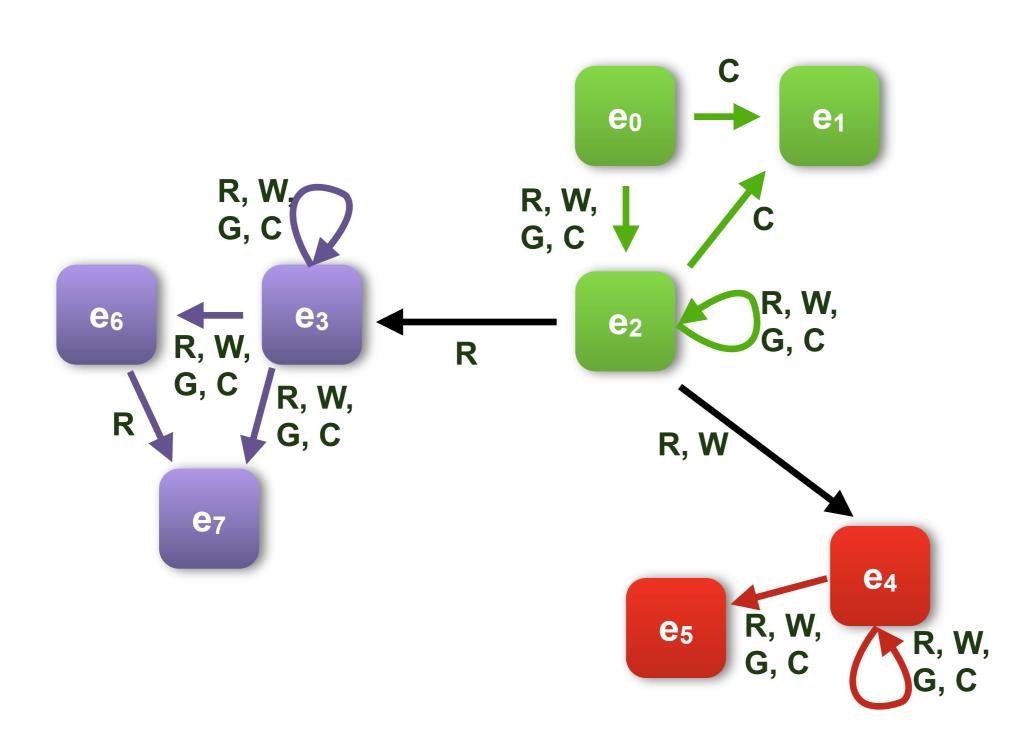

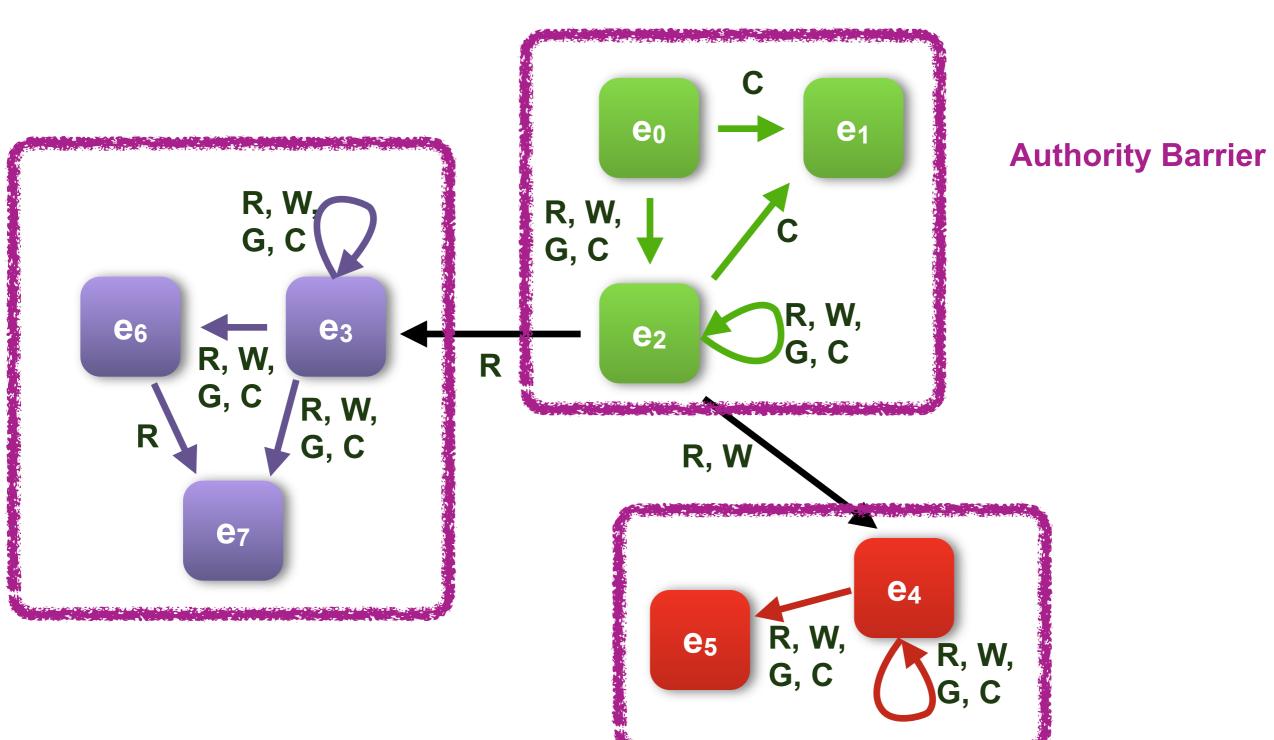

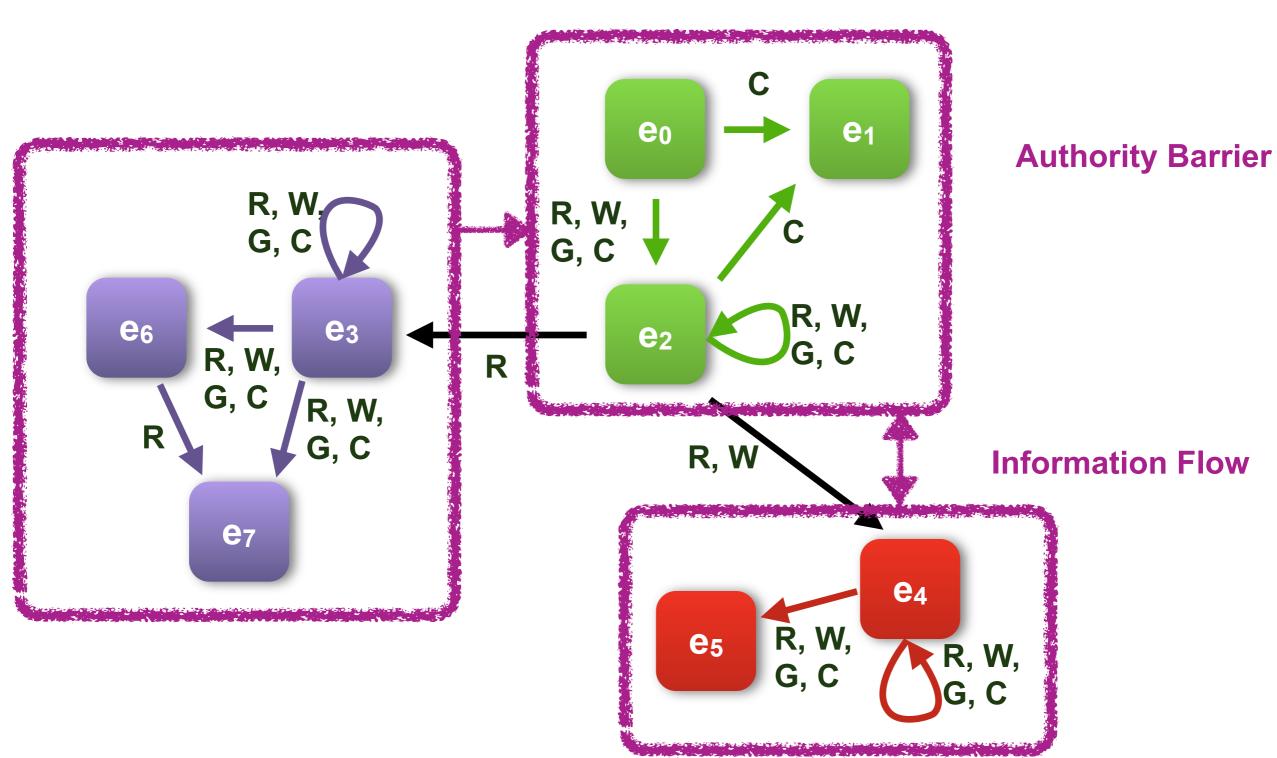

### Take-Grant model

#### **Lipton and Snyder:**

- entities represented as nodes of a graph

- capabilities represented as edges of a graph

- rights are contained in capabilities

The Rights: Read

Write

Create

Take

Grant

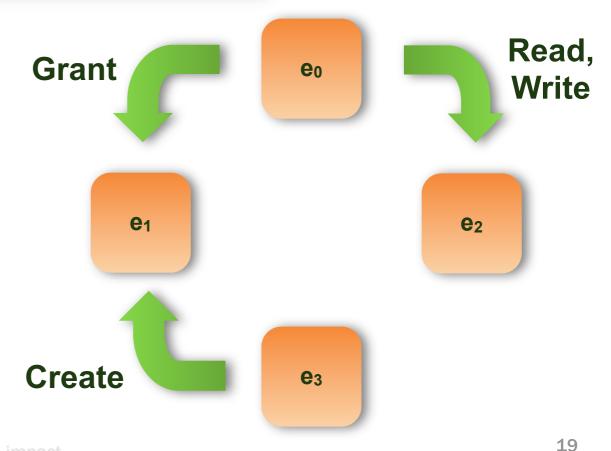

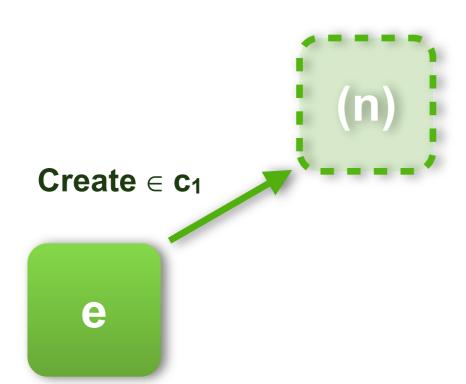

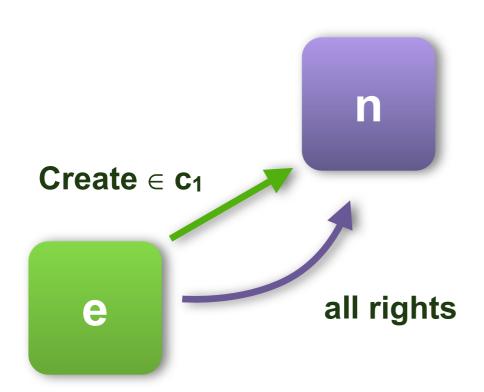

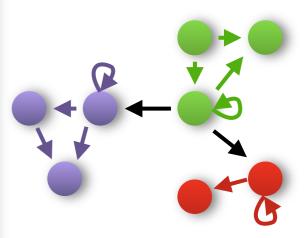

# Operations - Create

Create new entity

# Operations - Create

Create new entity

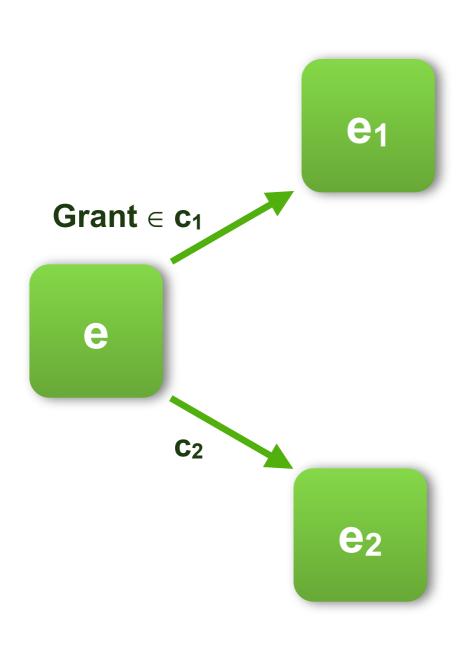

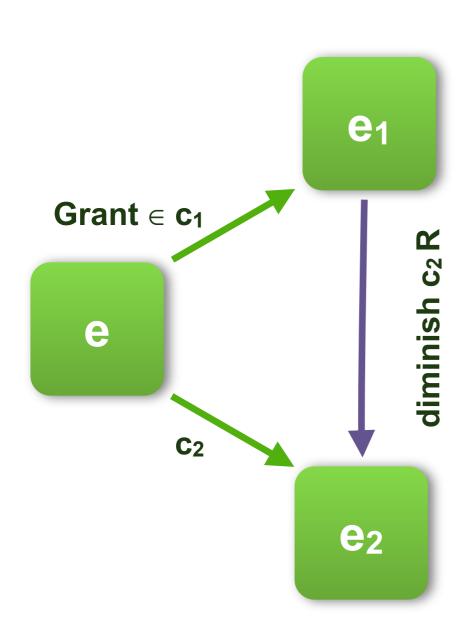

# Operations - Grant

# Grant c<sub>2</sub> to e<sub>1</sub> with mask R

# Operations - Grant

# Grant c<sub>2</sub> to e<sub>1</sub> with mask R

# Operations - Remove/Delete

### **Remove** capability c<sub>2</sub>

### **Delete** entity e<sub>2</sub>

# Operations - Remove/Delete

### **Remove** capability c<sub>2</sub>

### **Delete** entity e<sub>2</sub>

# Operations - Remove/Delete

### **Remove** capability c<sub>2</sub>

### **Delete** entity e<sub>2</sub>

## Questions

### For any state in the future:

- Can E gain authority to do X?

- Can E gain more authority than it has?

- How much more?

- Can **information** flow from A to B?

# Example

# Example

# Example

# **Now What?**

## **Current Proof**

# **Current Proof**

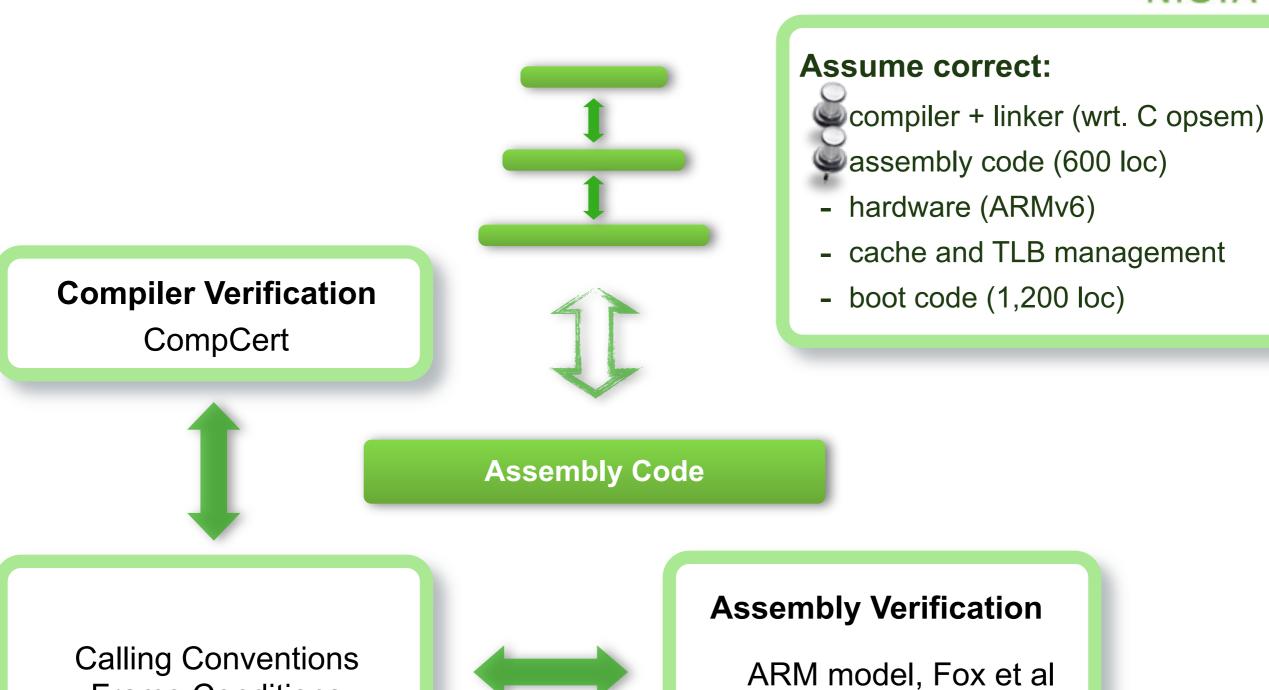

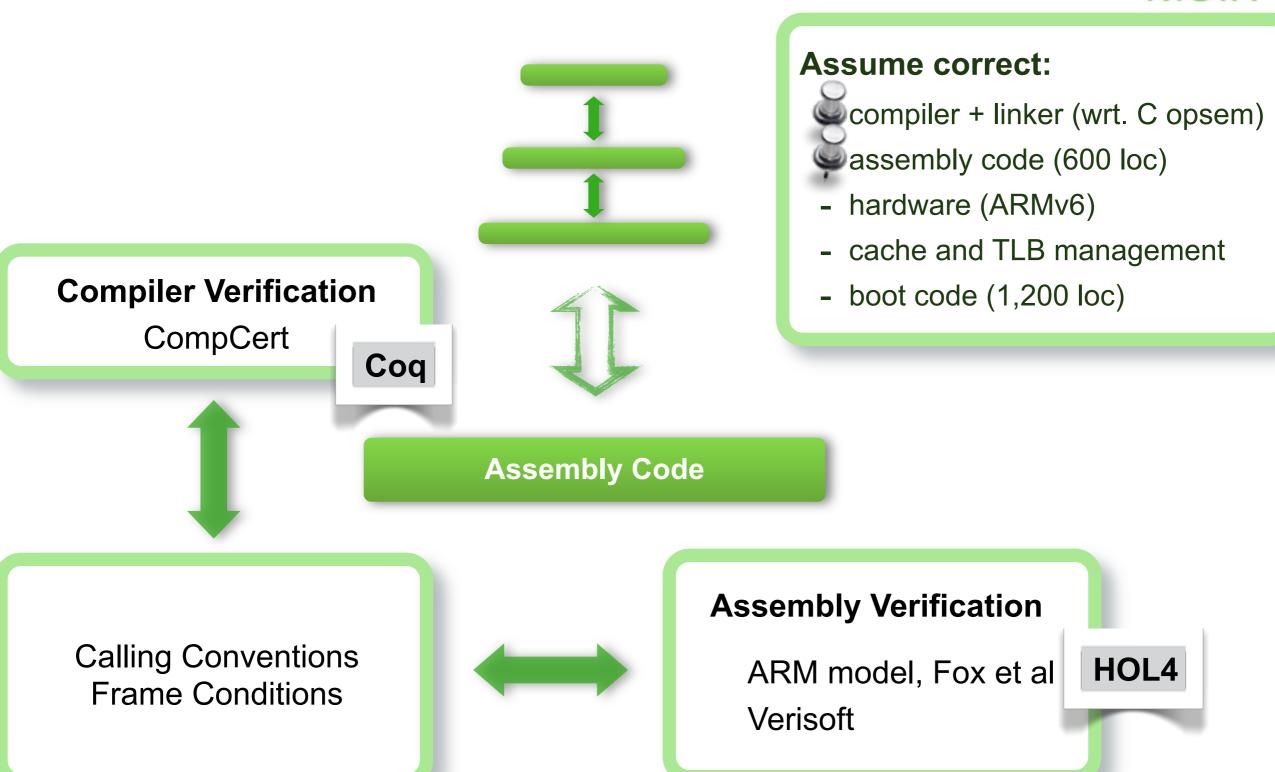

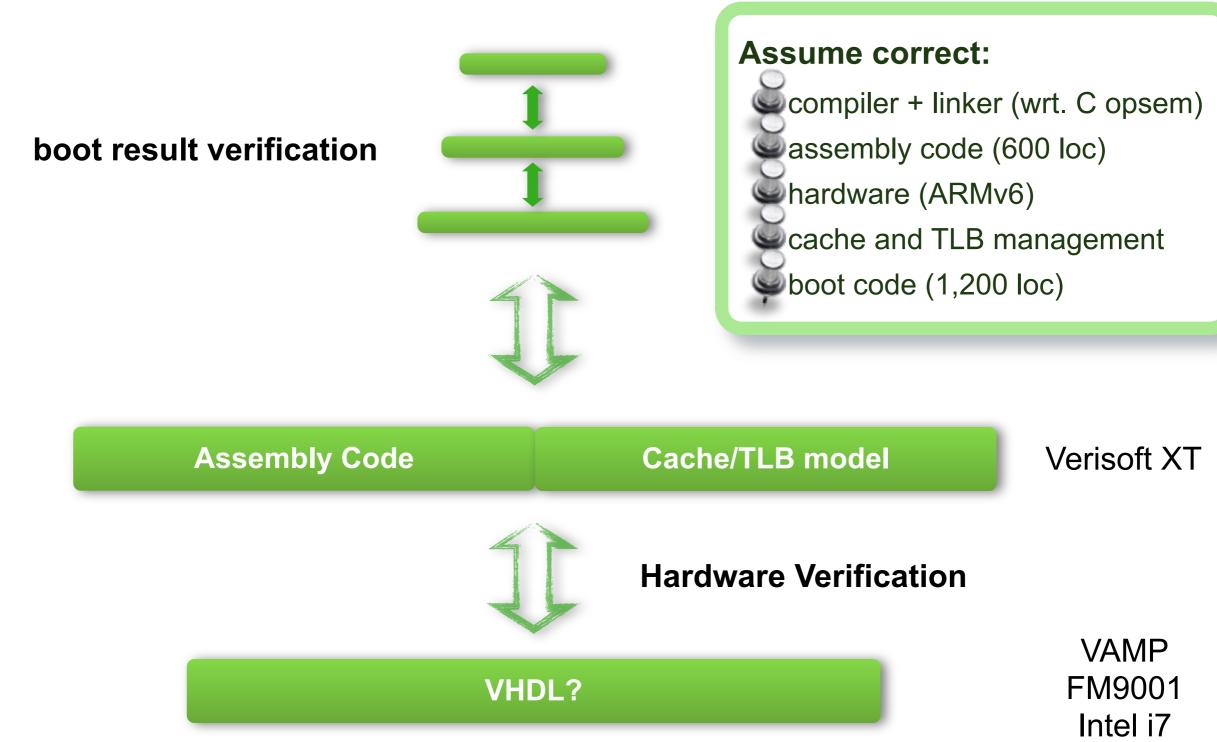

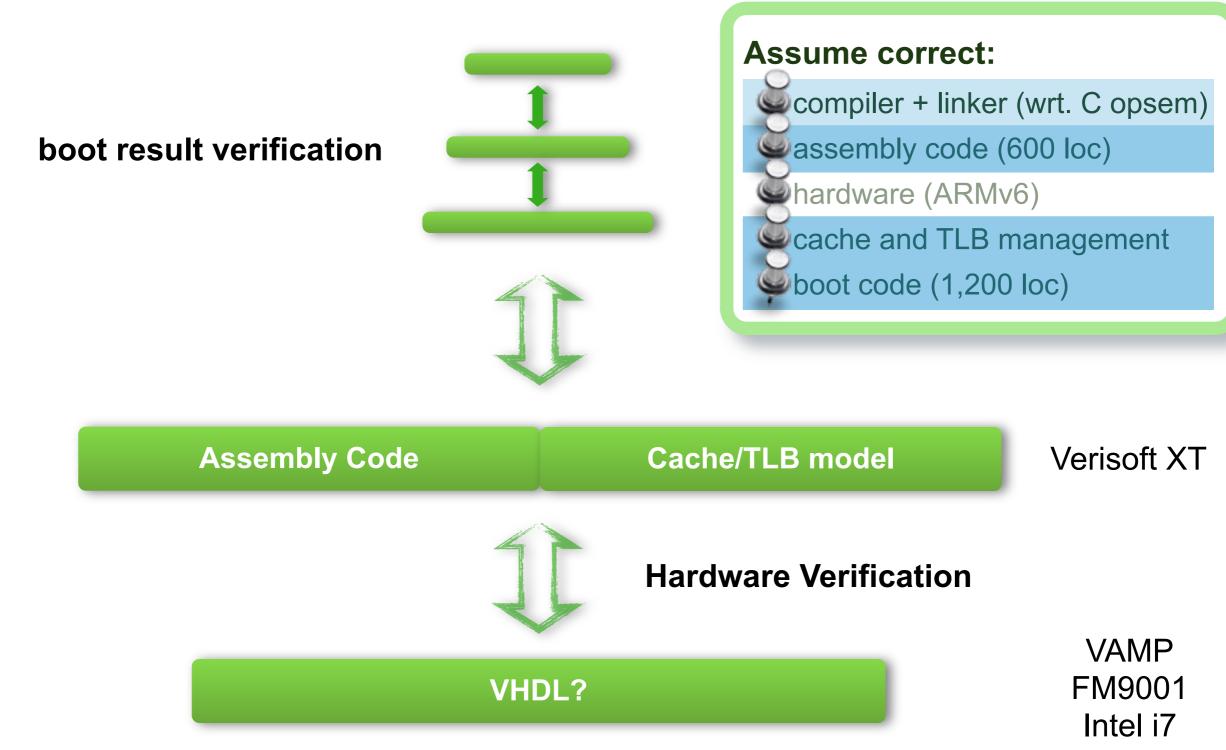

#### **Assume correct:**

- compiler + linker (wrt. C opsem)

- assembly code (600 loc)

- hardware (ARMv6)

- cache and TLB management

- boot code (1,200 loc)

**Assembly Code**

Compiler Verification

CompCert

#### **Assume correct:**

- assembly code (600 loc)

- hardware (ARMv6)

- cache and TLB management

- boot code (1,200 loc)

**Assembly Code**

Compiler Verification

CompCert

#### **Assume correct:**

compiler + linker (wrt. C opsem)

assembly code (600 loc)

- hardware (ARMv6)

- cache and TLB management

- boot code (1,200 loc)

**Assembly Code**

#### **Assembly Verification**

ARM model, Fox et al Verisoft

Frame Conditions

Verisoft

#### **Assume correct:**

- compiler + linker (wrt. C opsem)

- assembly code (600 loc)

- hardware (ARMv6)

- cache and TLB management

- boot code (1,200 loc)

**Assembly Code**

#### **Assume correct:**

compiler + linker (wrt. C opsem)

assembly code (600 loc)

- hardware (ARMv6)

cache and TLB management

- boot code (1,200 loc)

**Assembly Code**

Cache/TLB model

Verisoft XT

28

boot result verification

Assume correct:

compiler + linker (wrt. C opsem)

assembly code (600 loc)

- hardware (ARMv6)

cache and TLB management

boot code (1,200 loc)

Assembly Code

Cache/TLB model

Verisoft XT

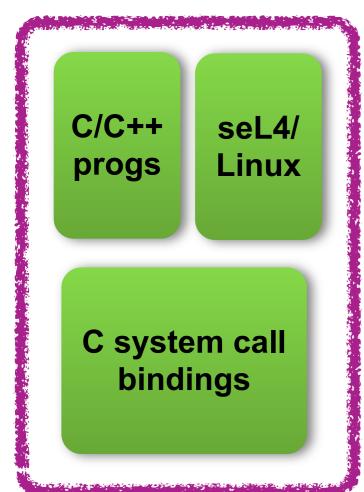

#### **Exists:**

- standard seL4 library

- used in seL4/Linux

- not hard to formally verify

- verification scheduled

C/C++ progs

seL4/ Linux

C system call bindings

Haskell Programs

**Haskell** runtime

#### seL4/Haskell:

- early prototype Haskell runtime

- has seL4 systems call bindings

- verification hard

- runtime verification progress in HASP project @ PSU & Galois

C system call bindings

Haskell Programs

Haskell runtime

Java Programs

**JVM**

- any takers?

- JVM extensively formalised

- widely used

- EAL7 smart card implementations exist

C system call bindings

Haskell Programs

Haskell runtime

Java Programs

**JVM**

# Other Architectures

### Other Architectures

#### Intel 32bit

#### seL4/x86:

- x86 version exists, supports Linux

- verification likely, not started yet

#### Other Architectures

30

#### Intel 32bit + IOMMU

#### seL4/x86:

- x86 version exists, supports Linux

- verification likely, not started yet

- Intel VT-d/IOMMU implemented

- enables untrusted device DMA

- verification possible

#### Other Architectures

30

#### Intel 32bit + IOMMU + multi core

#### seL4/x86:

- x86 version exists, supports Linux

- verification likely, not started yet

- Intel VT-d/IOMMU implemented

- enables untrusted device DMA

- verification possible

- experimental multi processor version

- initial proofs exist

#### Other Architectures

#### Intel 32bit + IOMMU + multi core

#### seL4/x86:

- x86 version exists, supports Linux

- verification likely, not started yet

- Intel VT-d/IOMMU implemented

- enables untrusted device DMA

- verification possible

- experimental multi processor version

- initial proofs exist

#### **New Architectures**

- ca 1/3 of seL4 arch dependent

- close to ARM

- -> easy to implement and verify

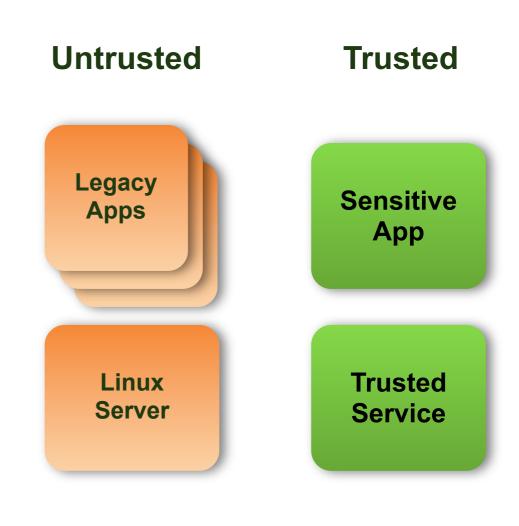

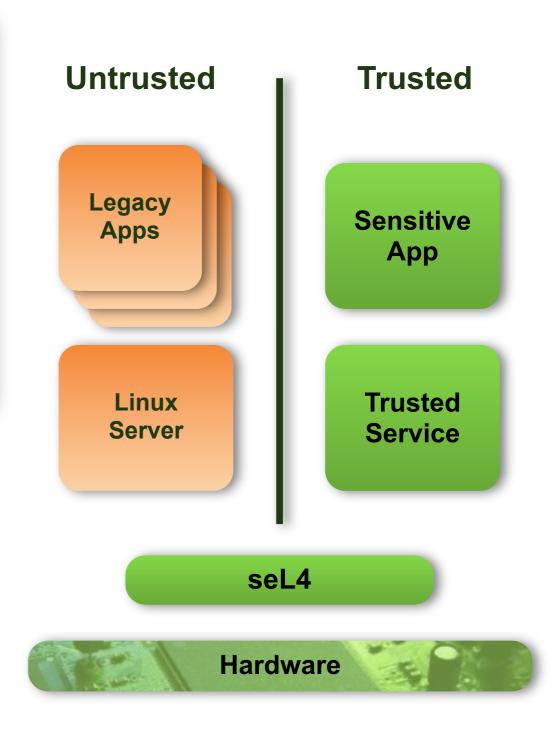

# Looking Forward

# Looking Forward

# Trustworthy Embedded Systems

L4.verified: functional correctness 10,000 loc

Next step: formal guarantees for > 1,000,000 loc

#### How?

# **Exploit:**

- seL4 isolation

- verified properties

- MILS architectures

# Challenges

- Find right architecture

- Security analysis

- identify trusted components

- -ideally take-grant style

- behaviour of trusted components

- Code-level theorem in the end

- connect to kernel proof

- ideally prove trusted component only

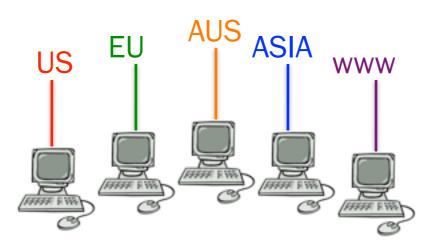

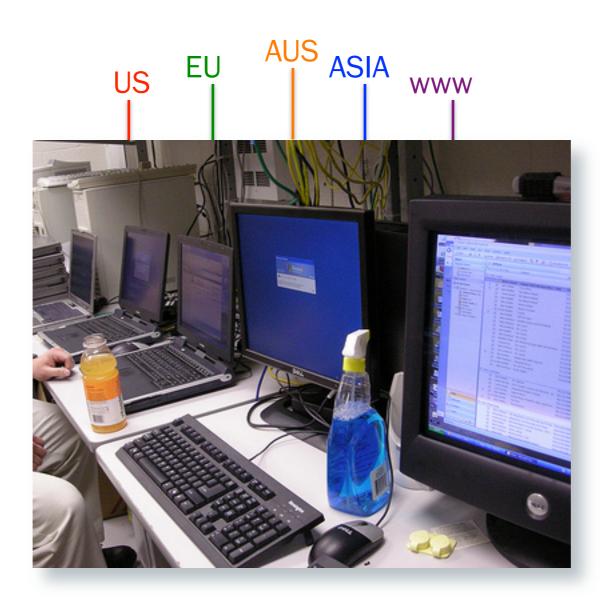

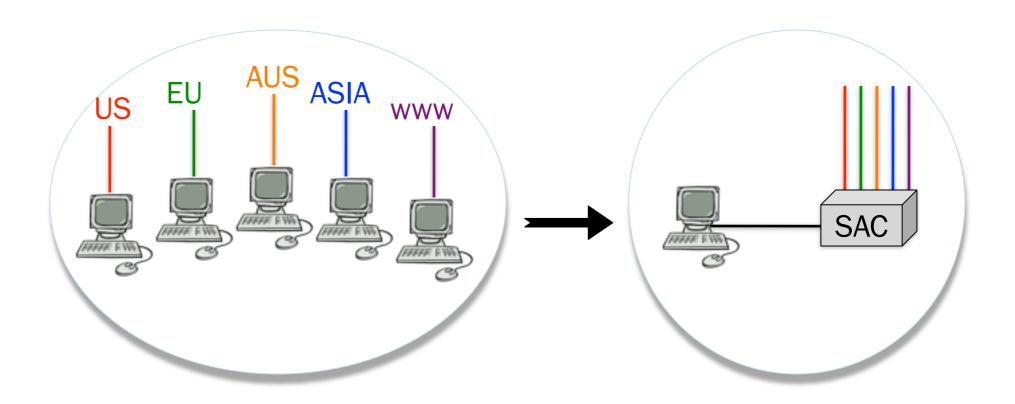

Scenario:

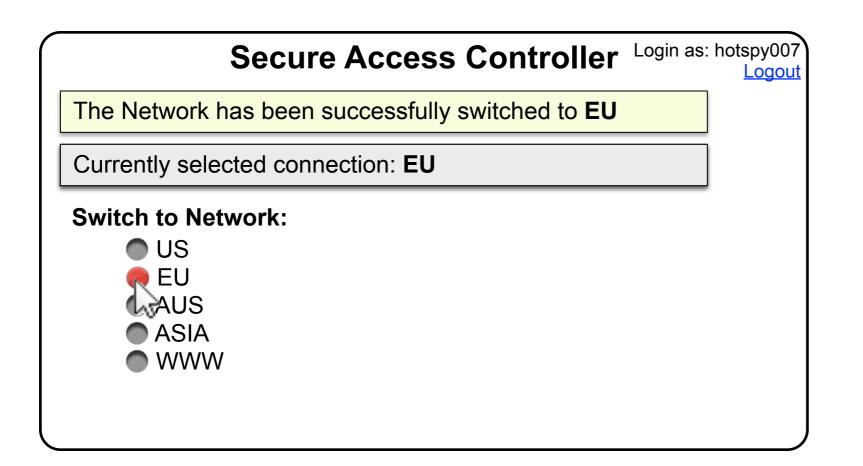

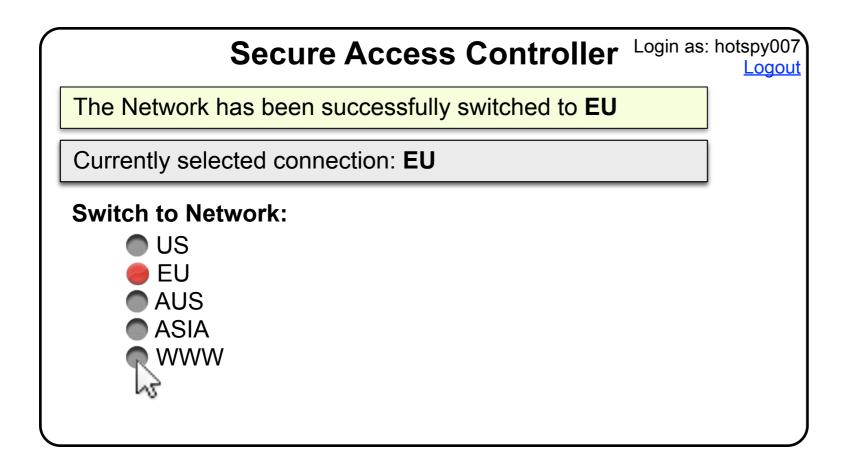

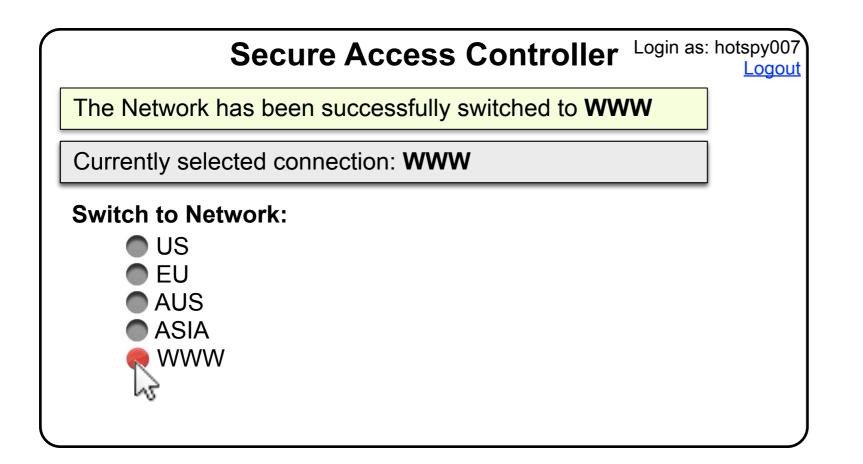

#### • Scenario:

Multilevel Secure Access Device

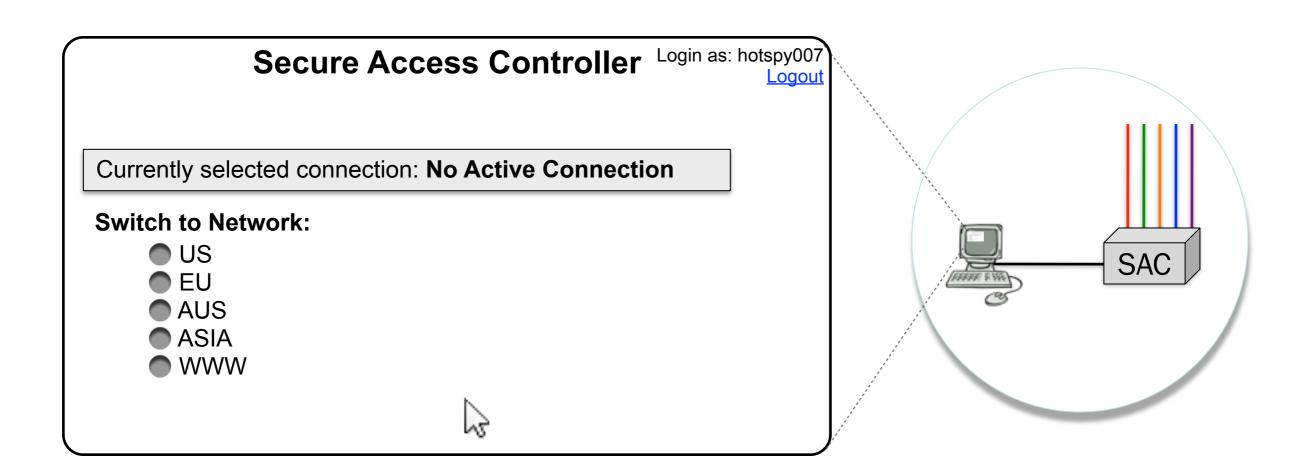

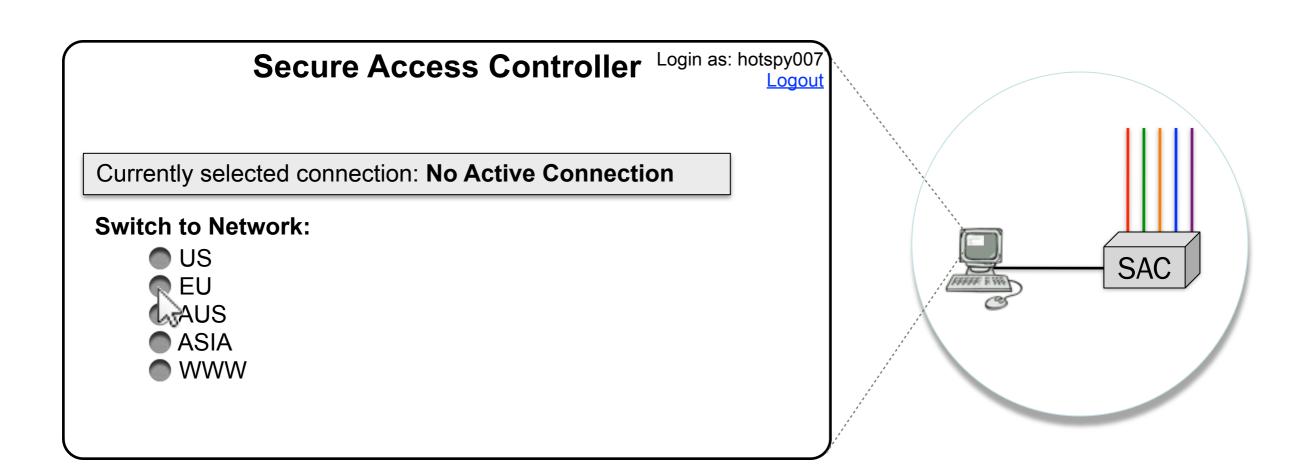

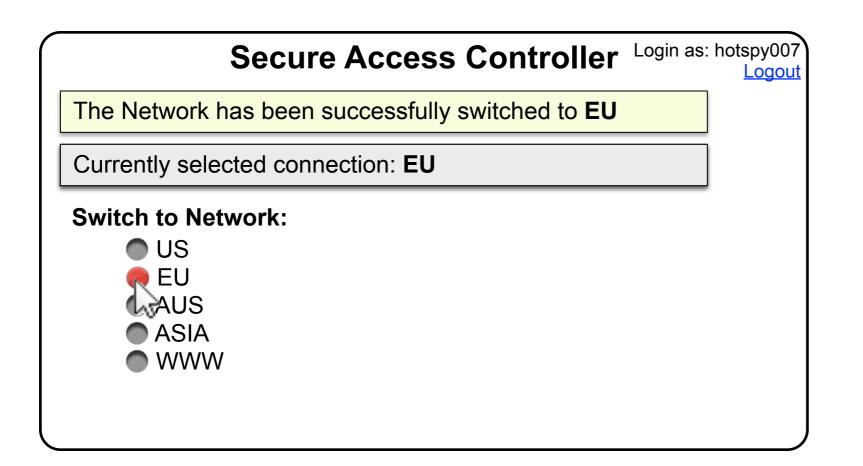

# Secure Access Controller Login as: hotspy007 Logout Currently selected connection: No Active Connection Switch to Network: US EU AUS ASIA WWW

39

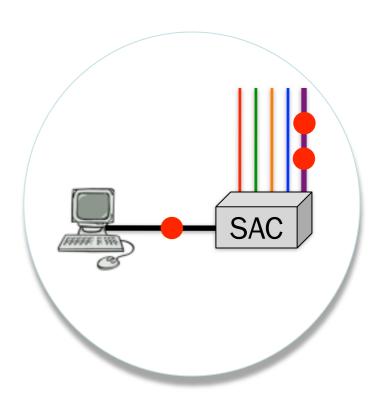

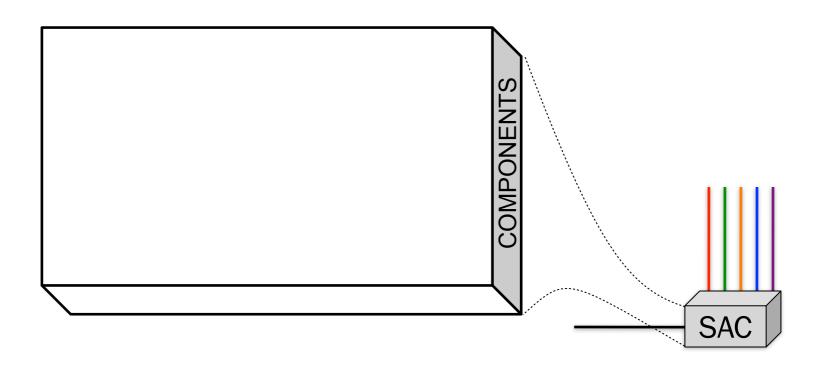

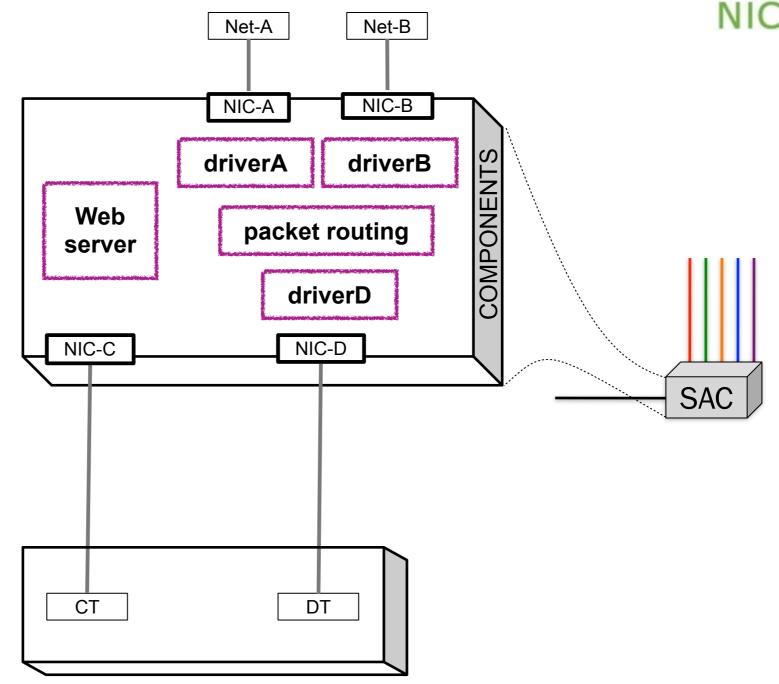

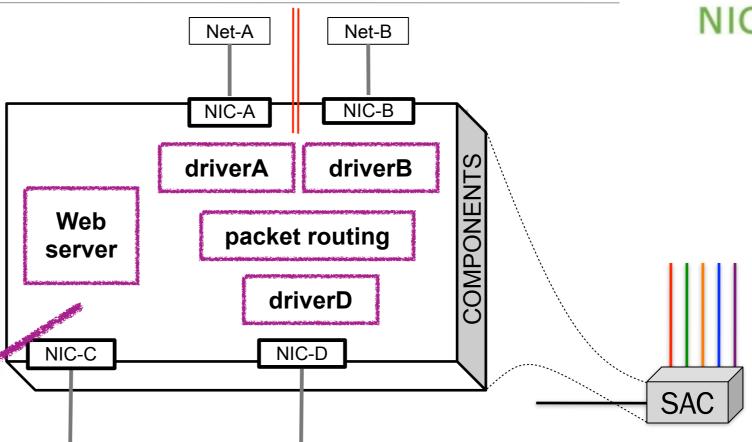

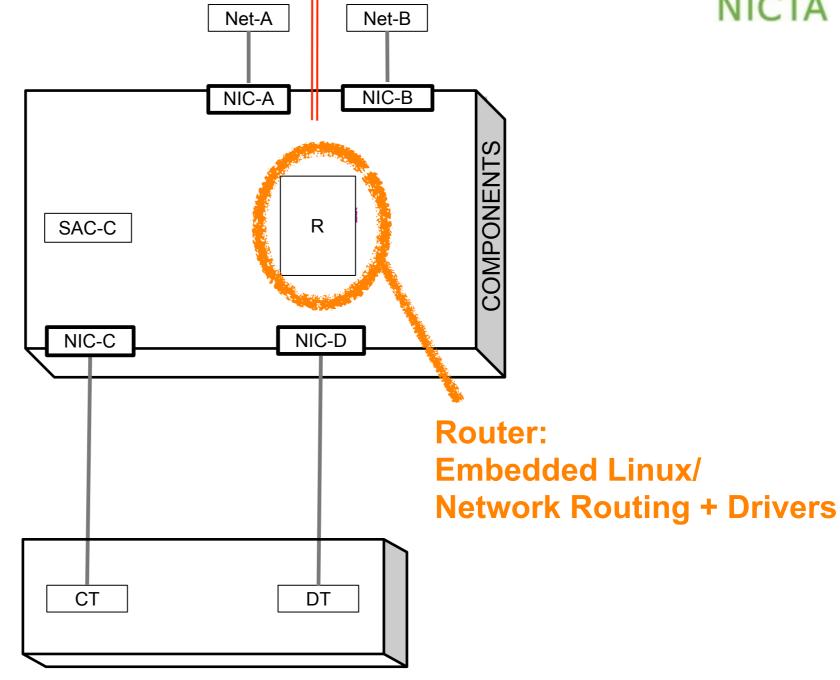

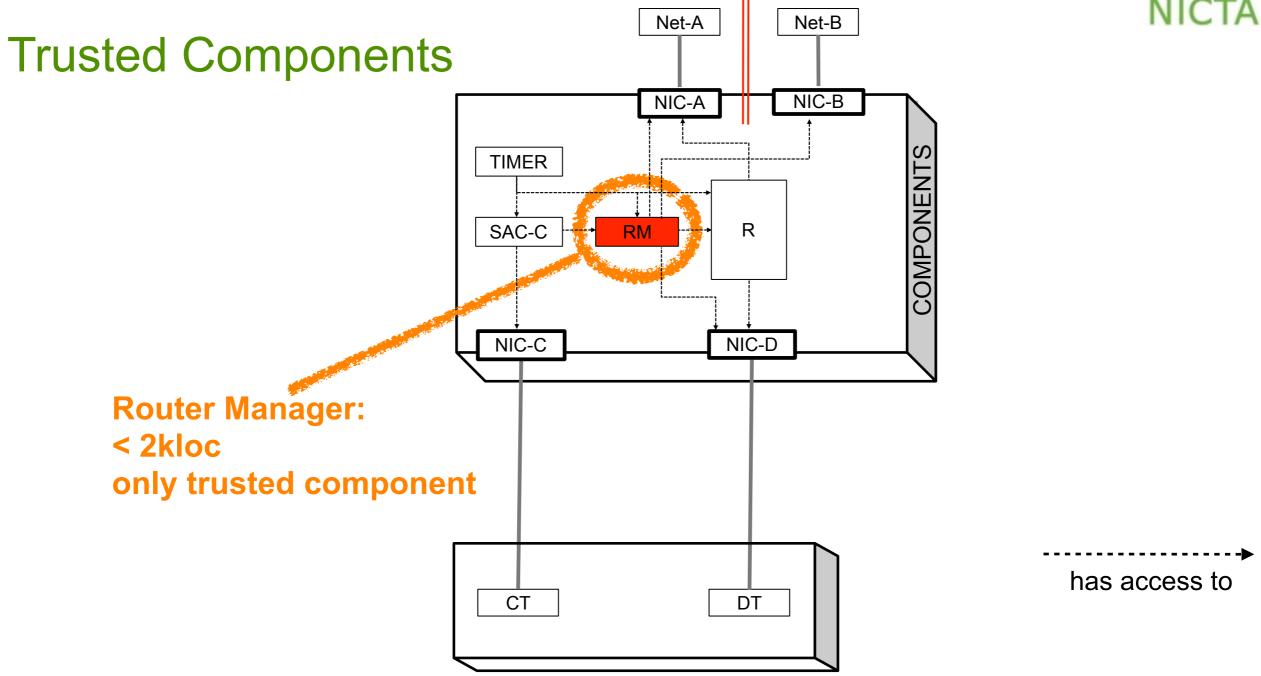

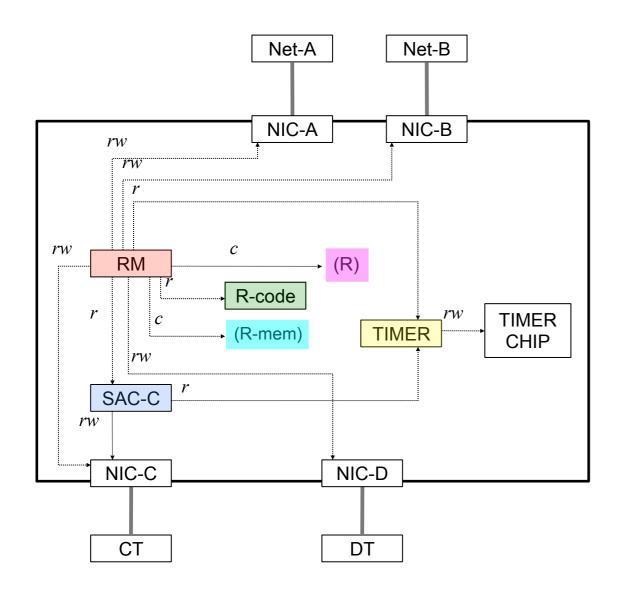

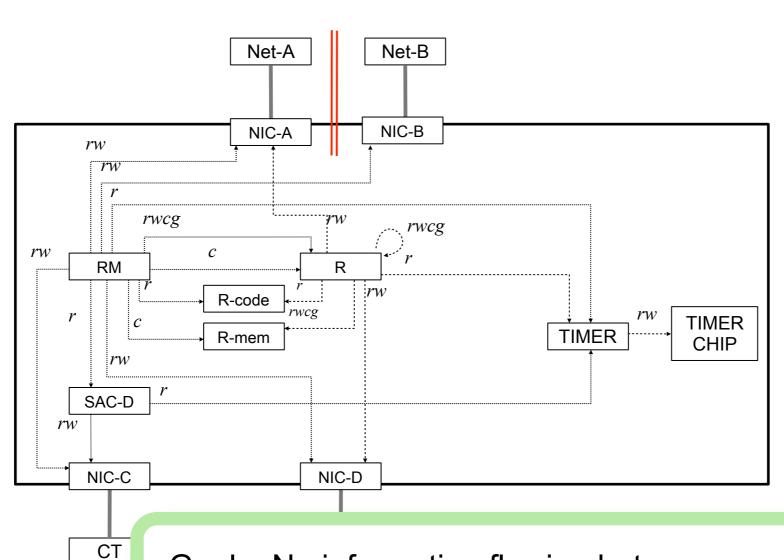

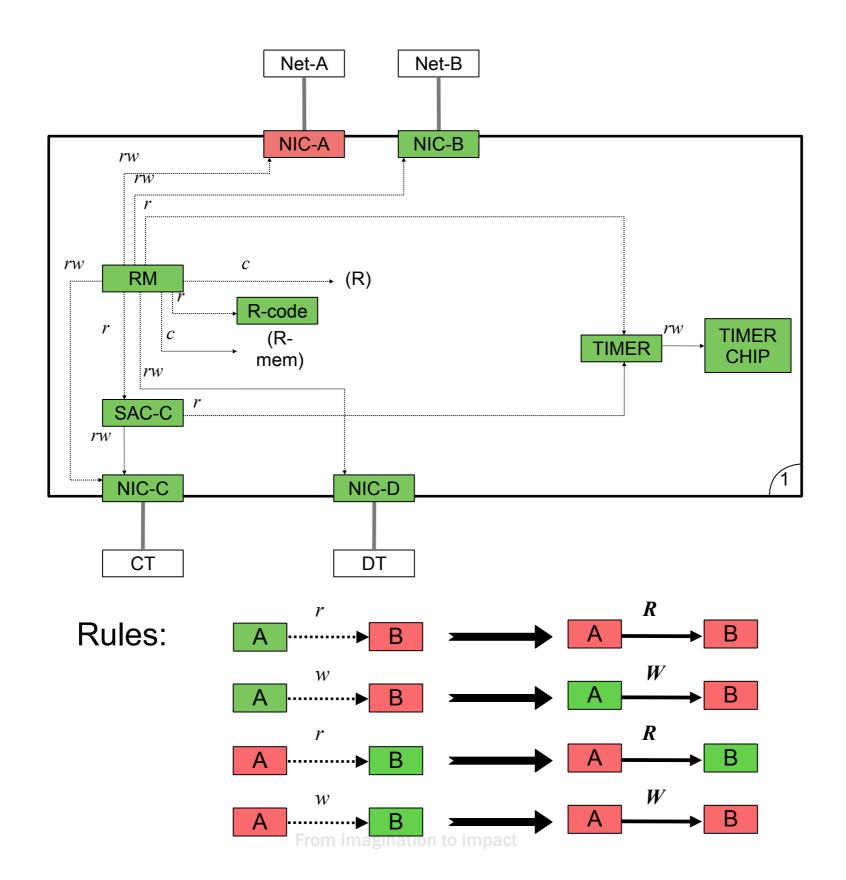

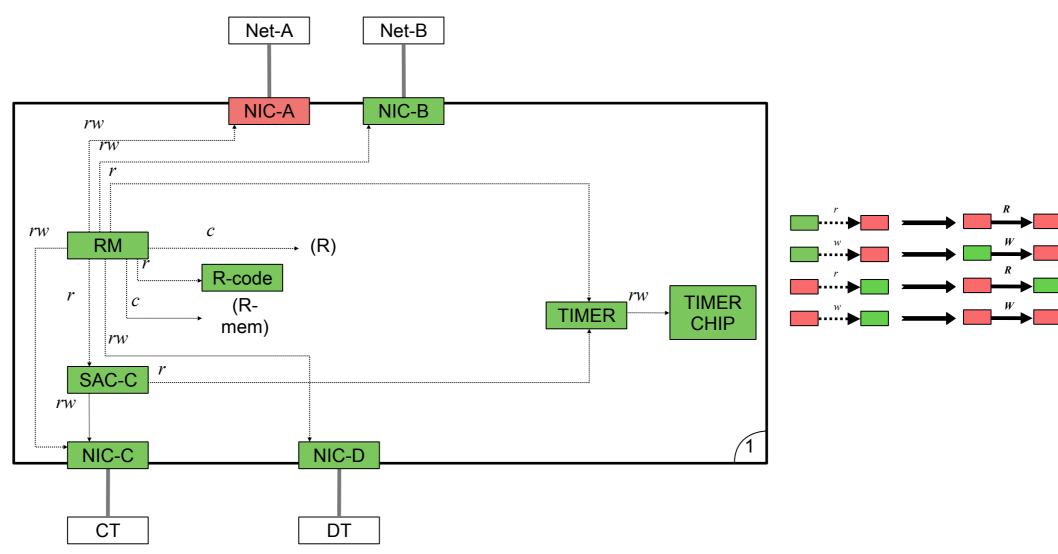

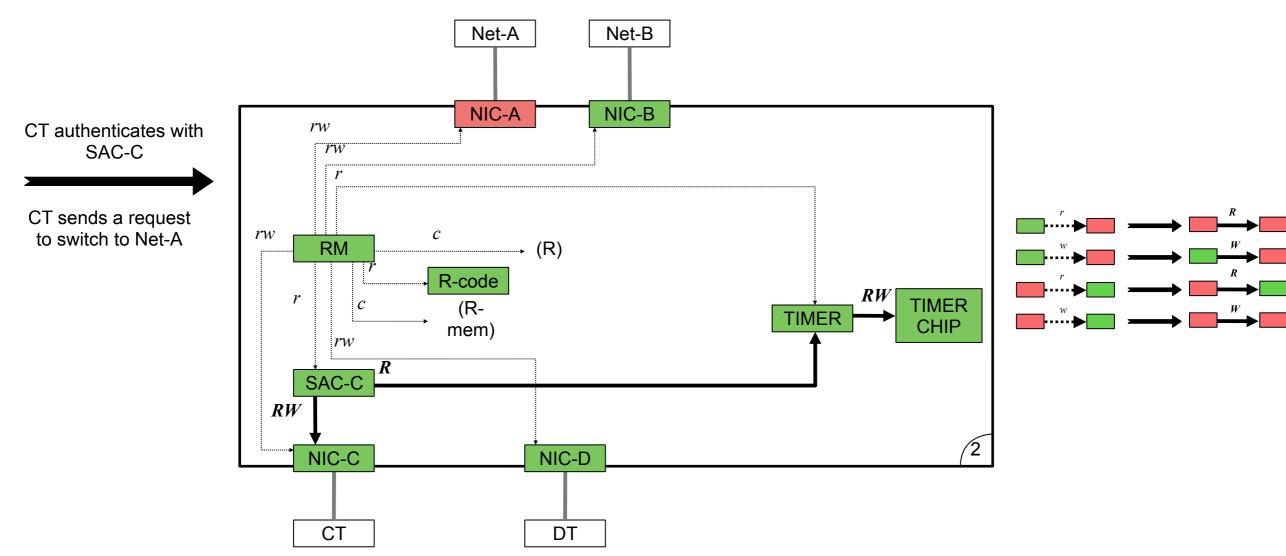

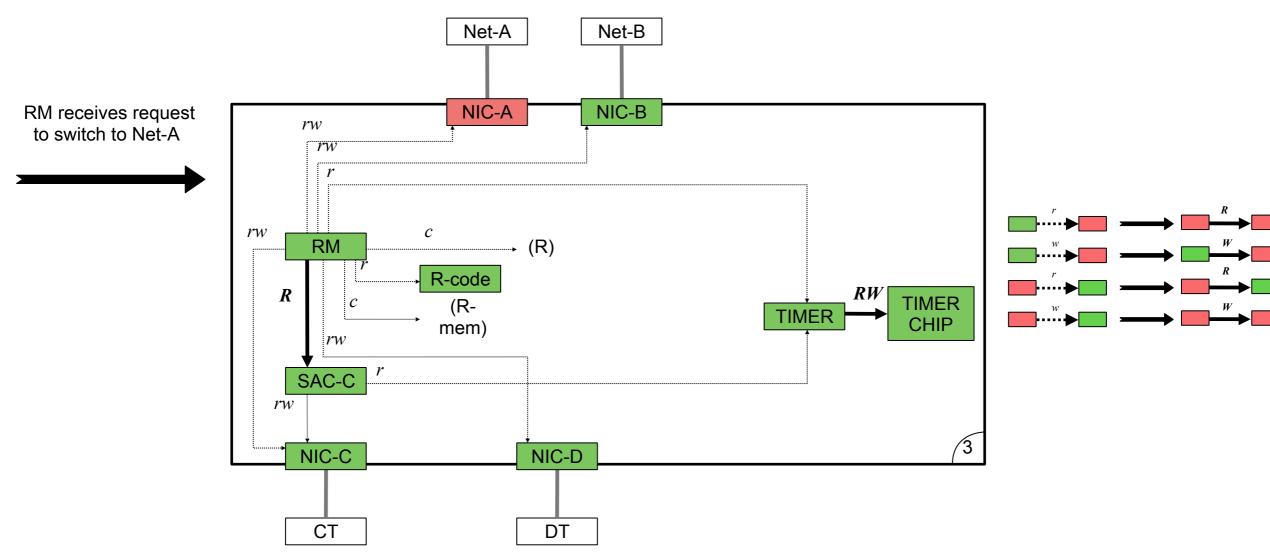

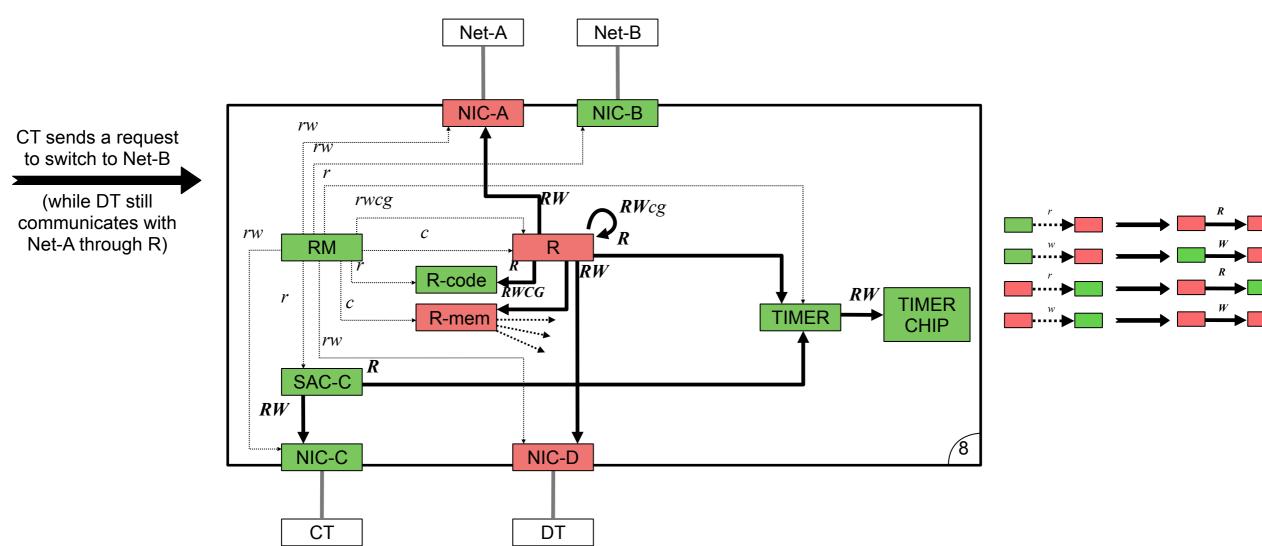

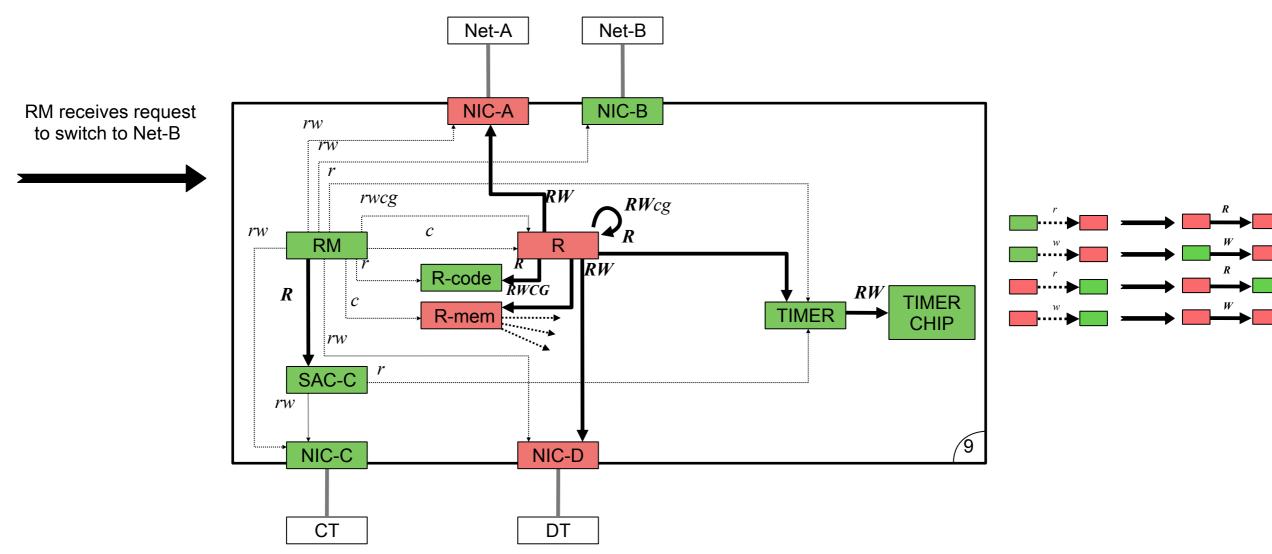

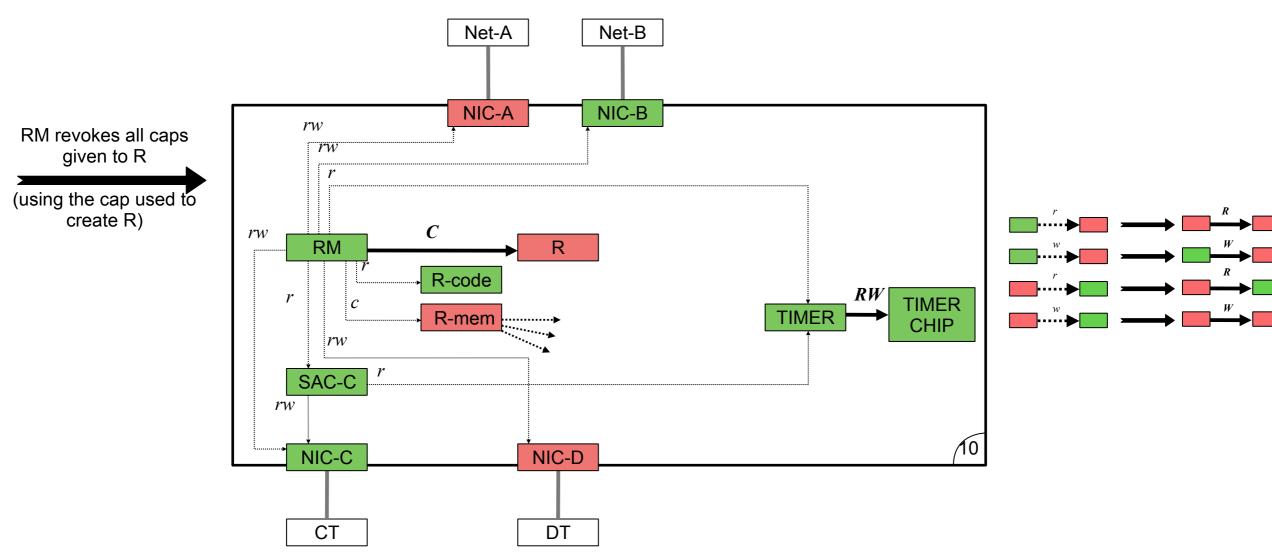

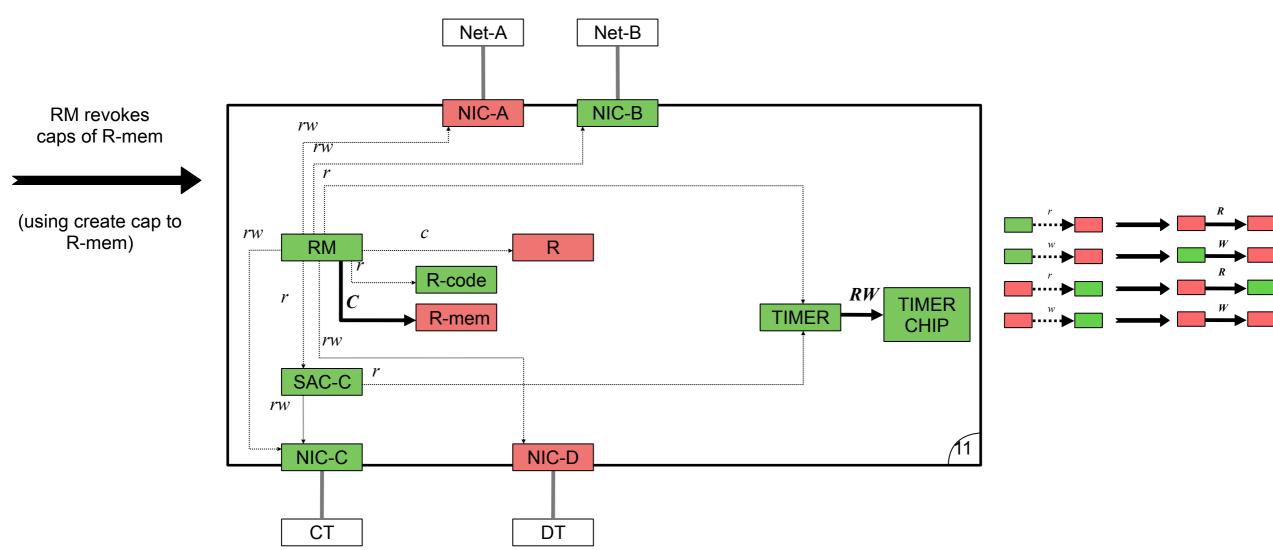

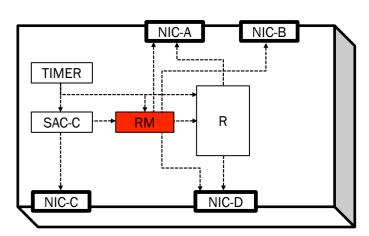

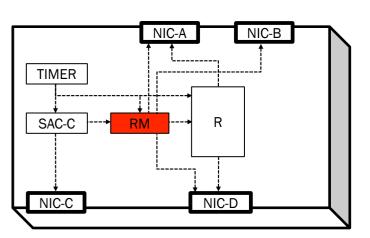

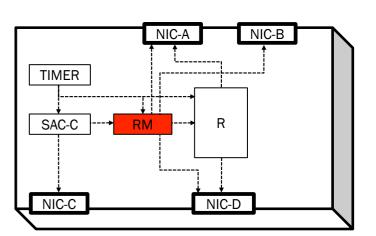

## Components

# NICTA

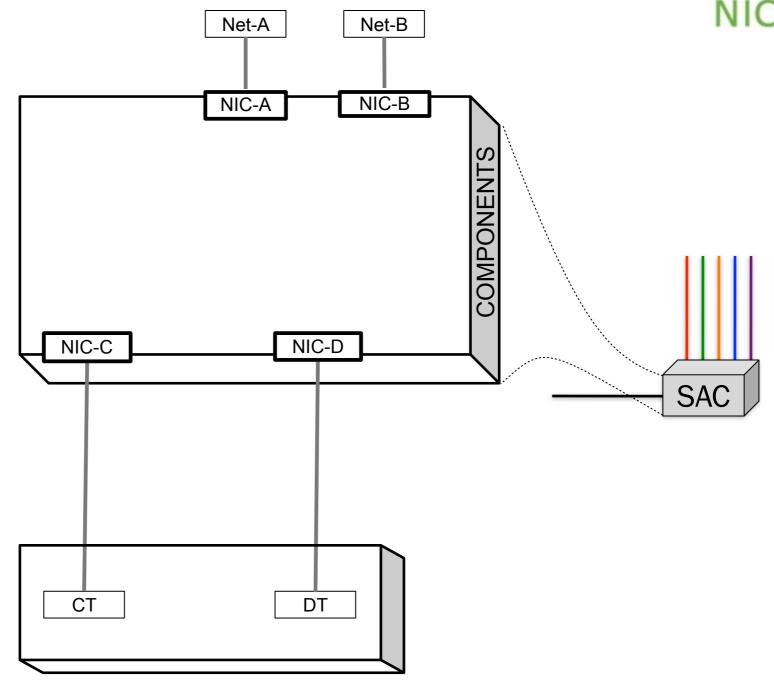

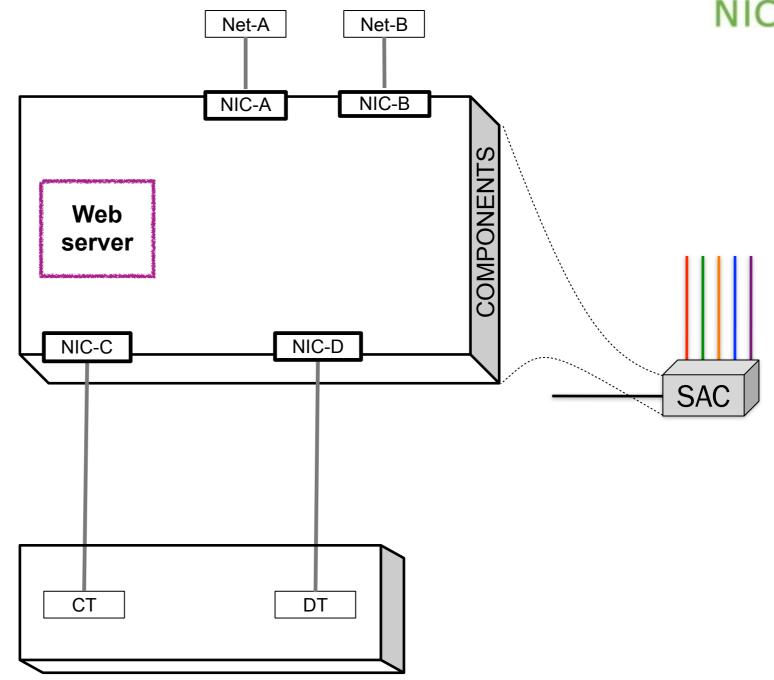

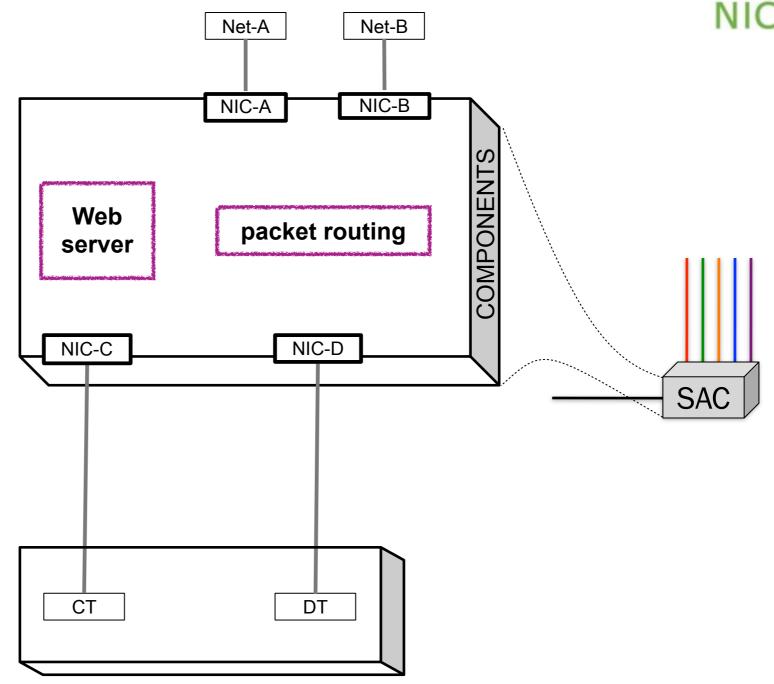

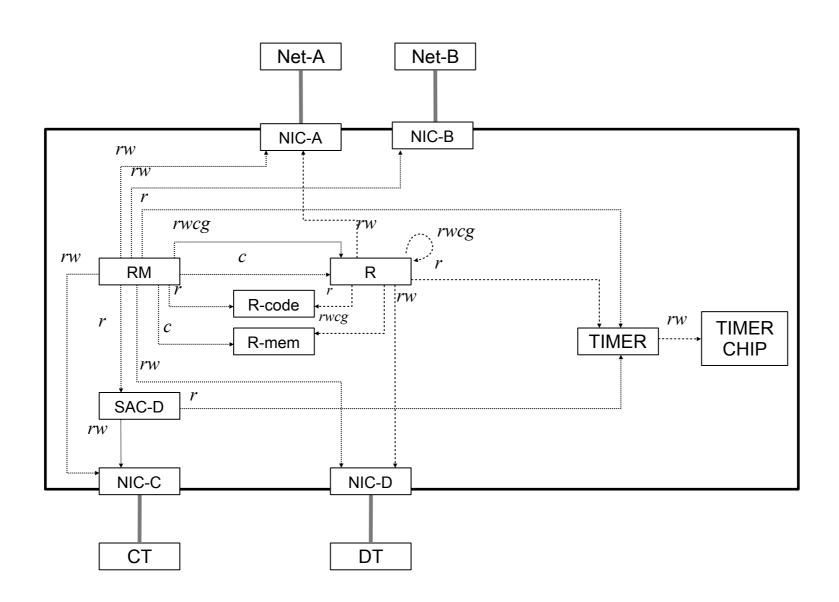

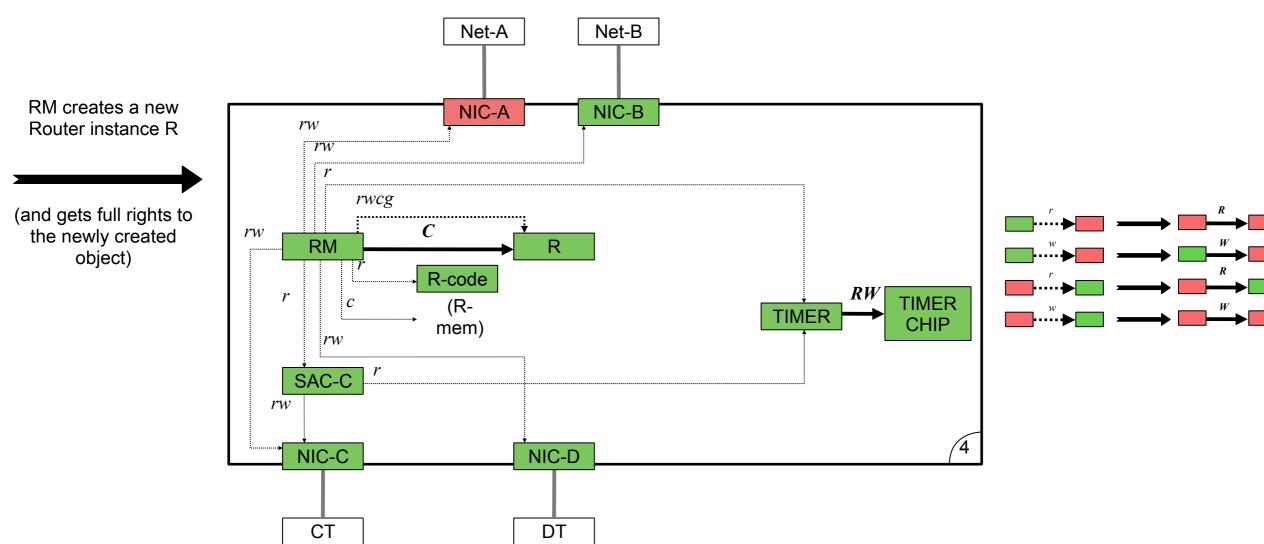

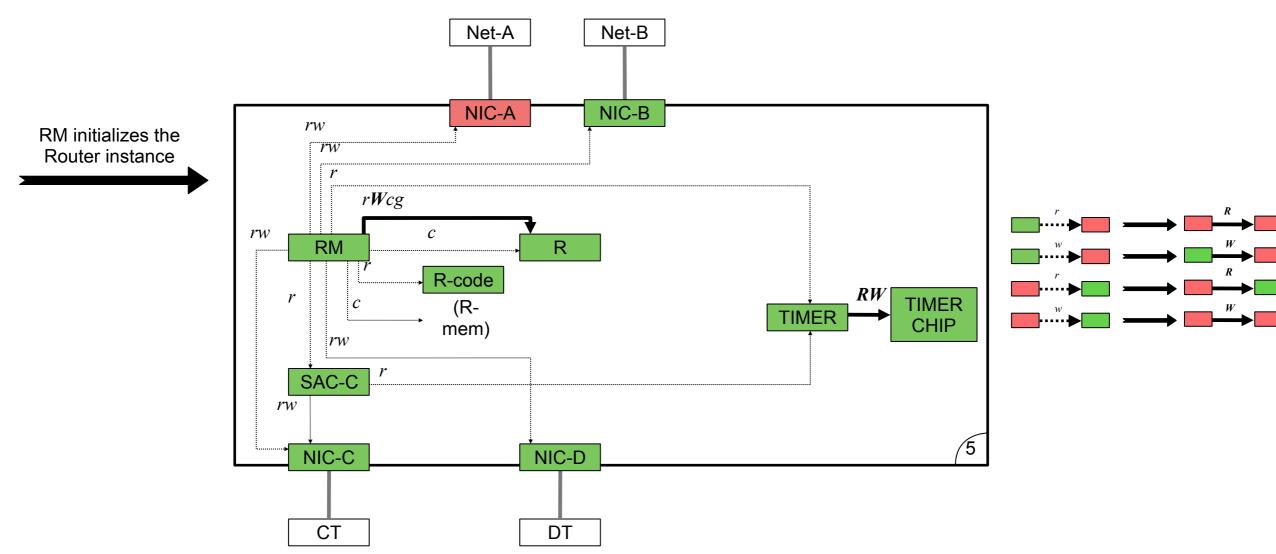

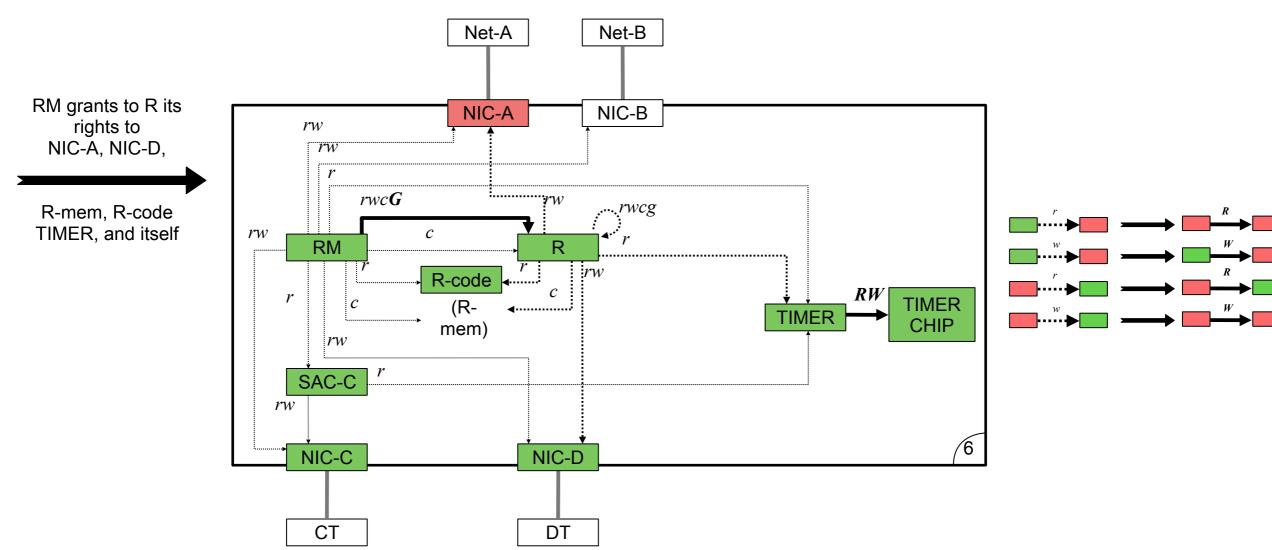

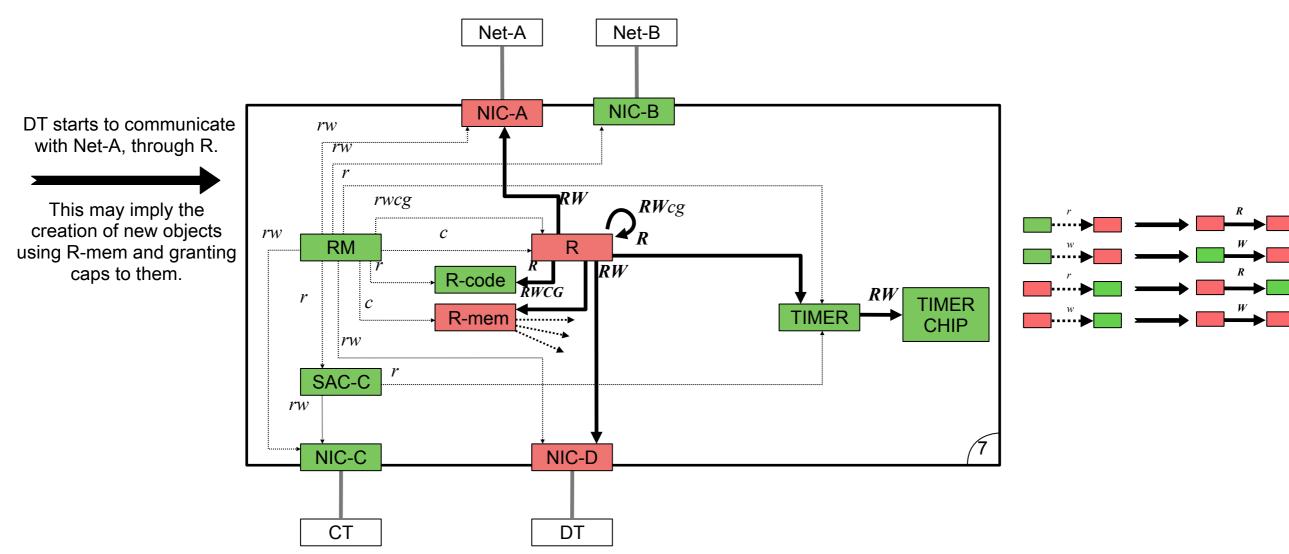

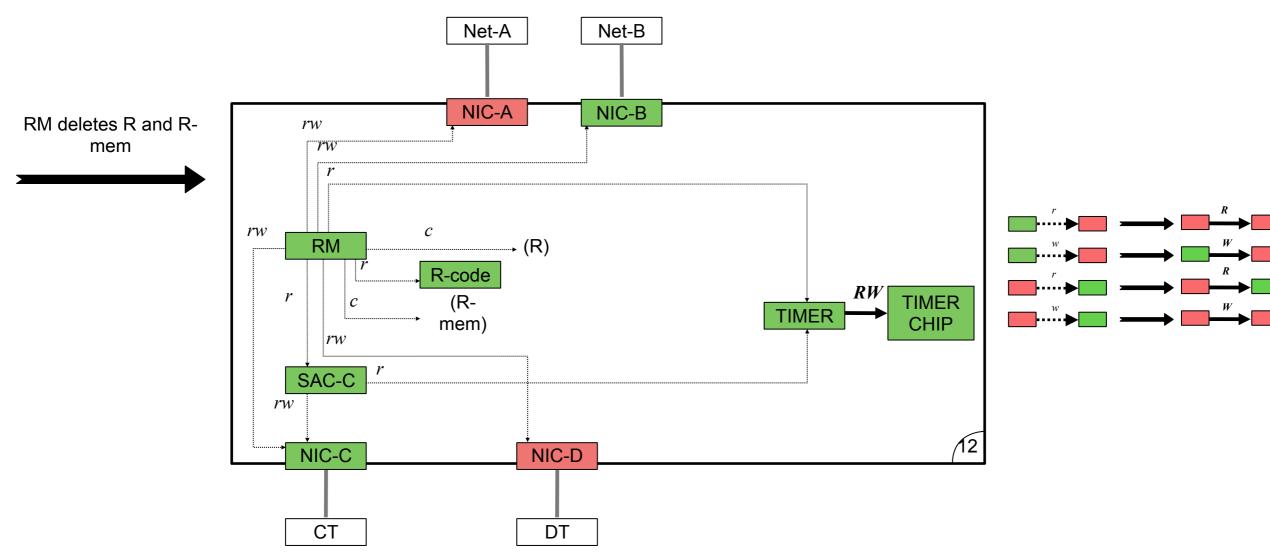

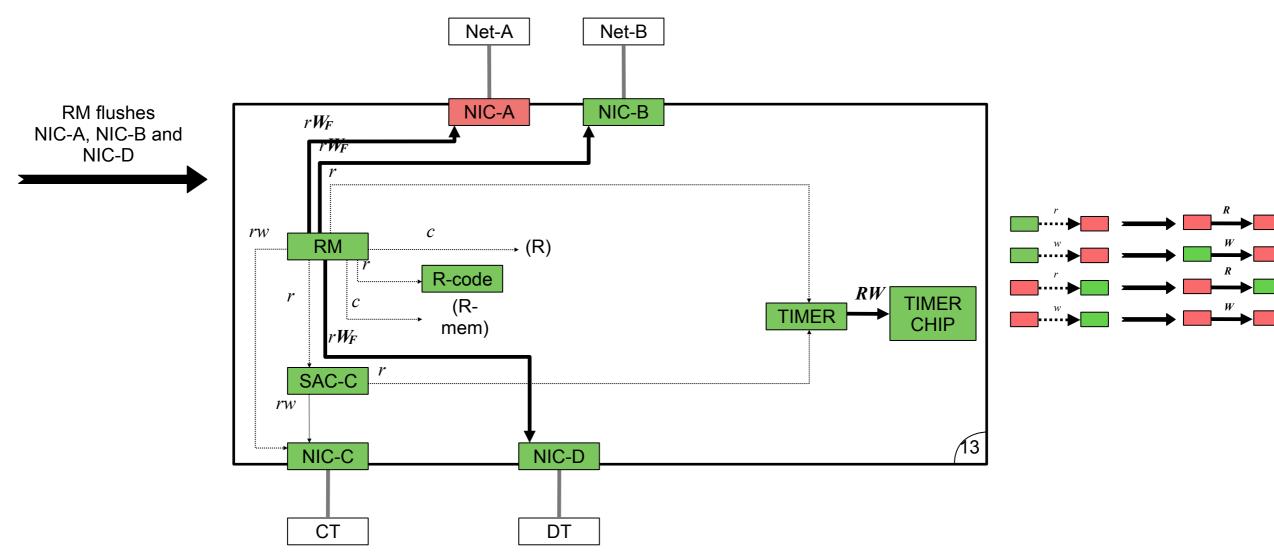

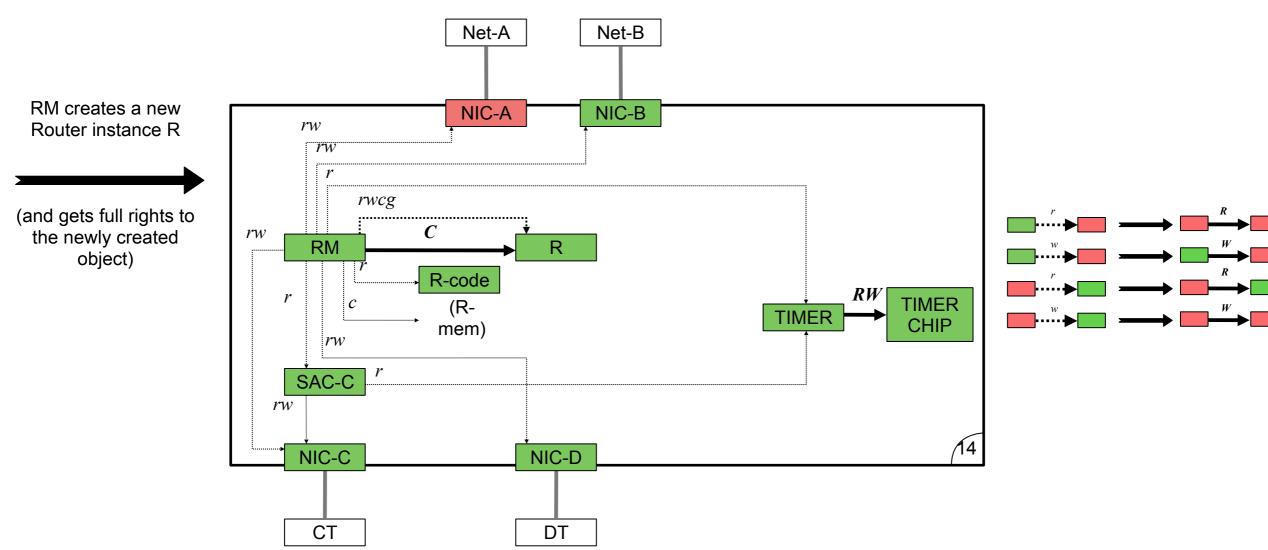

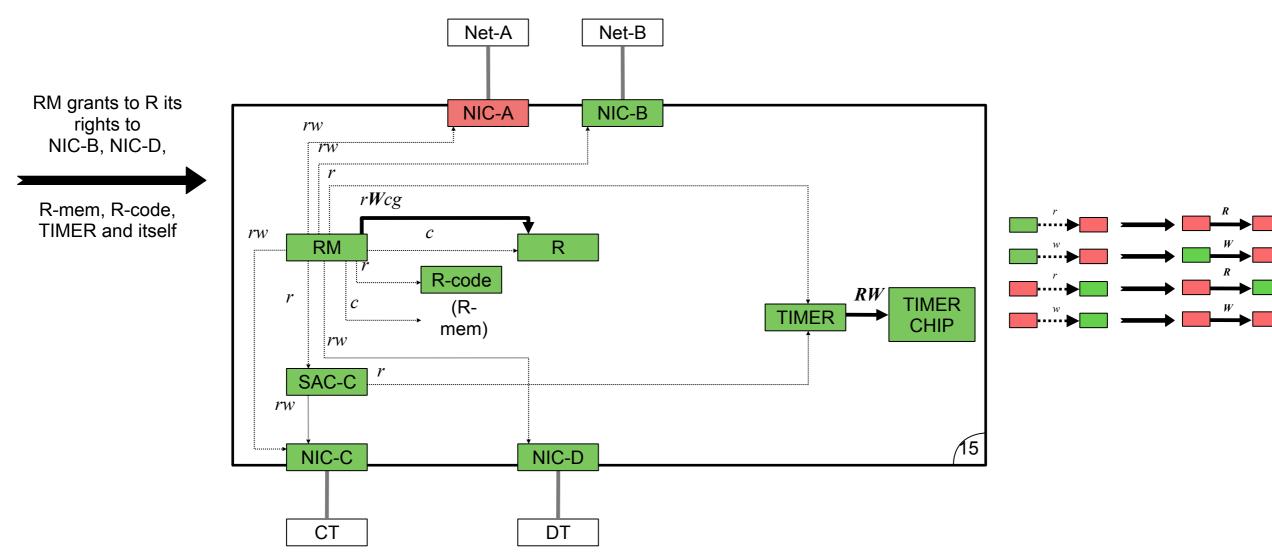

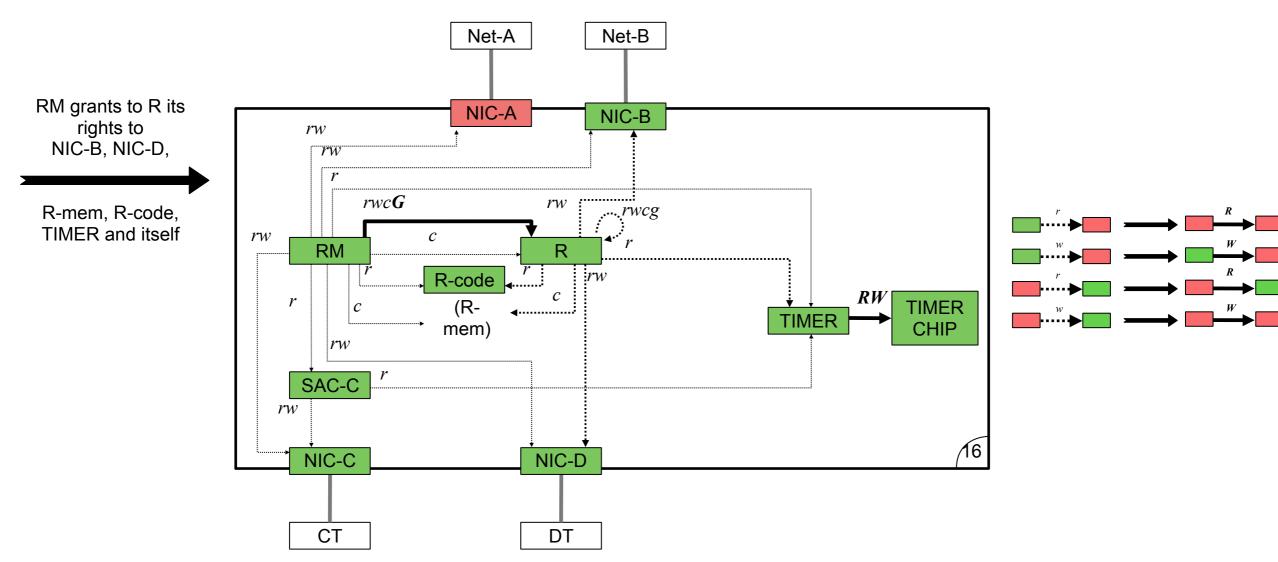

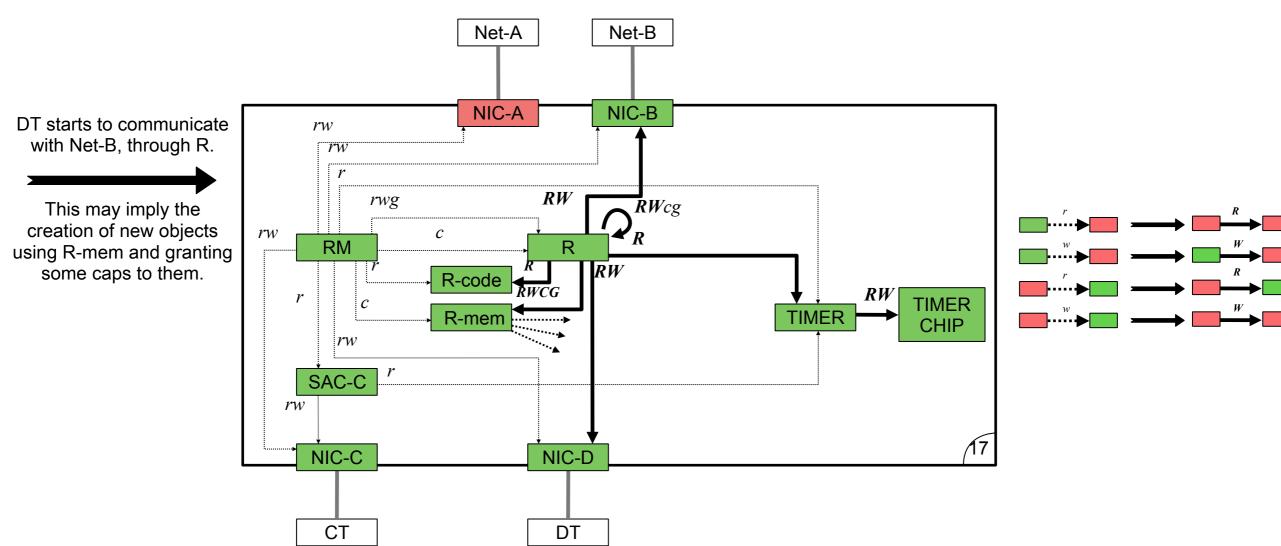

#### Components

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

# NICTA

#### Components

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

# NICTA

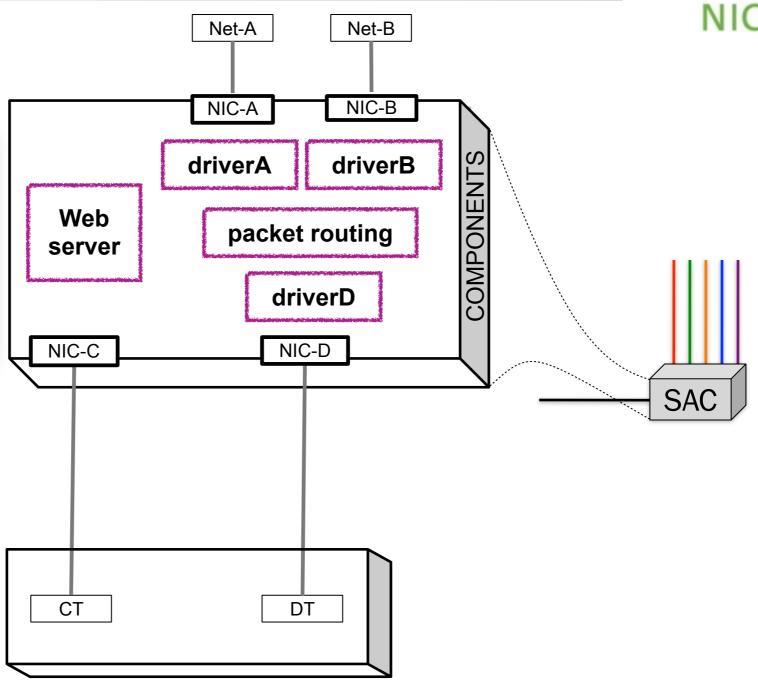

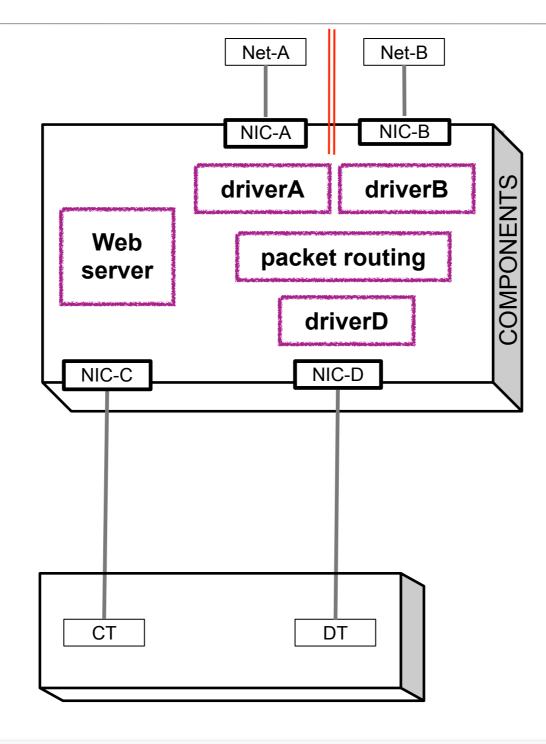

#### Components

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

# NICTA

#### Components

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

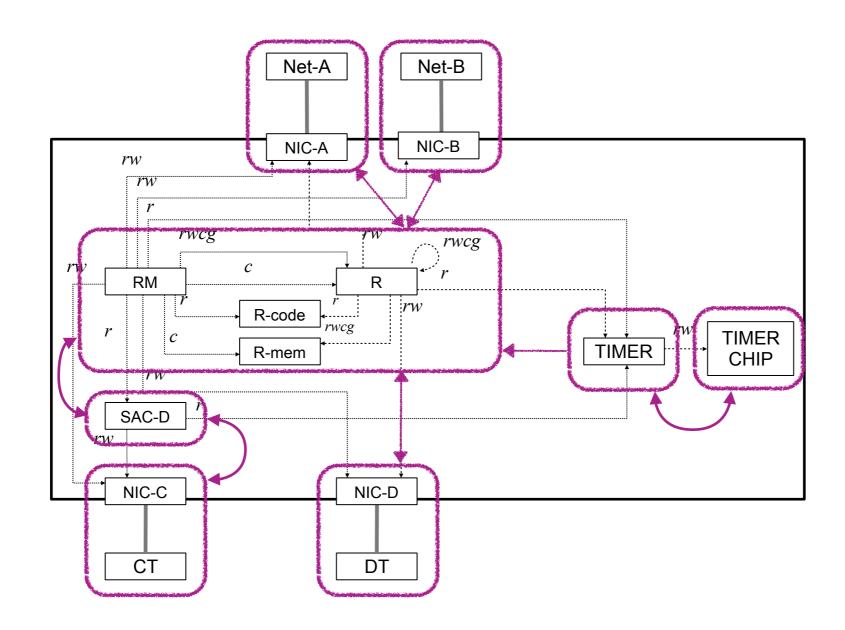

### **Desired Property**

No information flow between providers A and B through SAC even if they collaborate

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

# NICTA

#### **Desired Property**

No information flow between providers A and B through SAC even if they collaborate

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

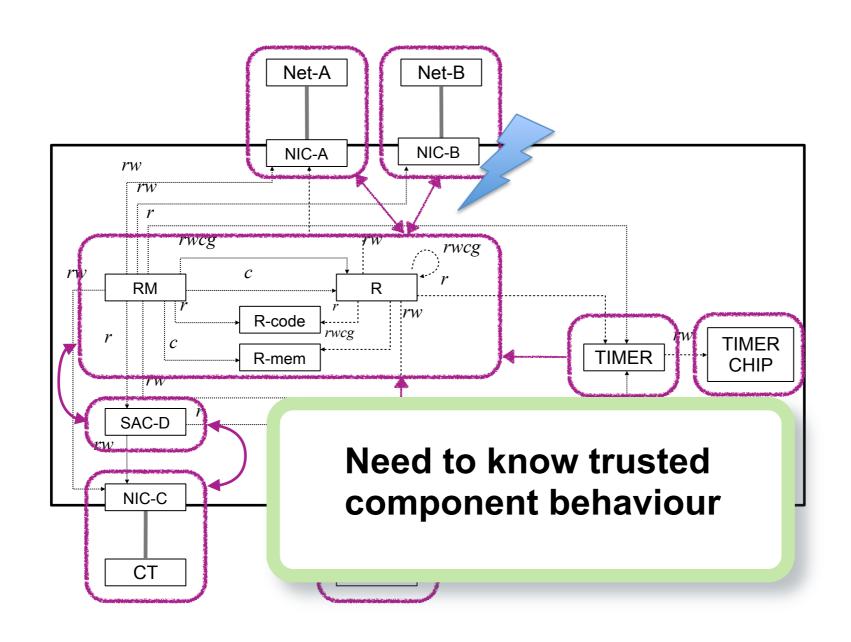

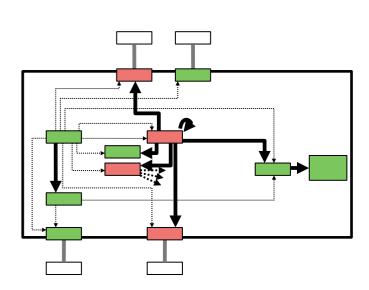

### **Desired Property**

No information flow between providers A and B through SAC even if they collaborate

**Proving all this correct?**

DT

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

CT

### **Desired Property**

No information flow between providers A and B through SAC even if they collaborate

Proving all this correct?

NO! CT DT

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

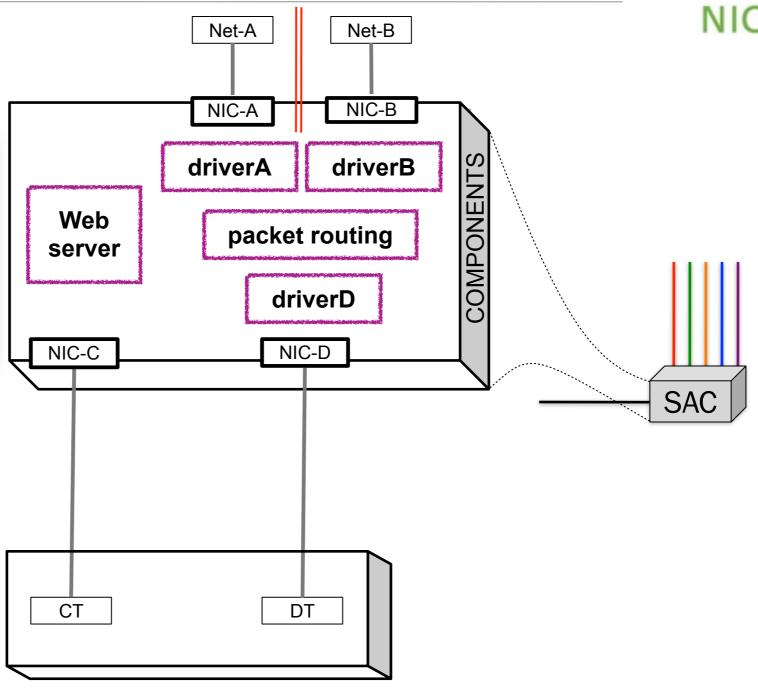

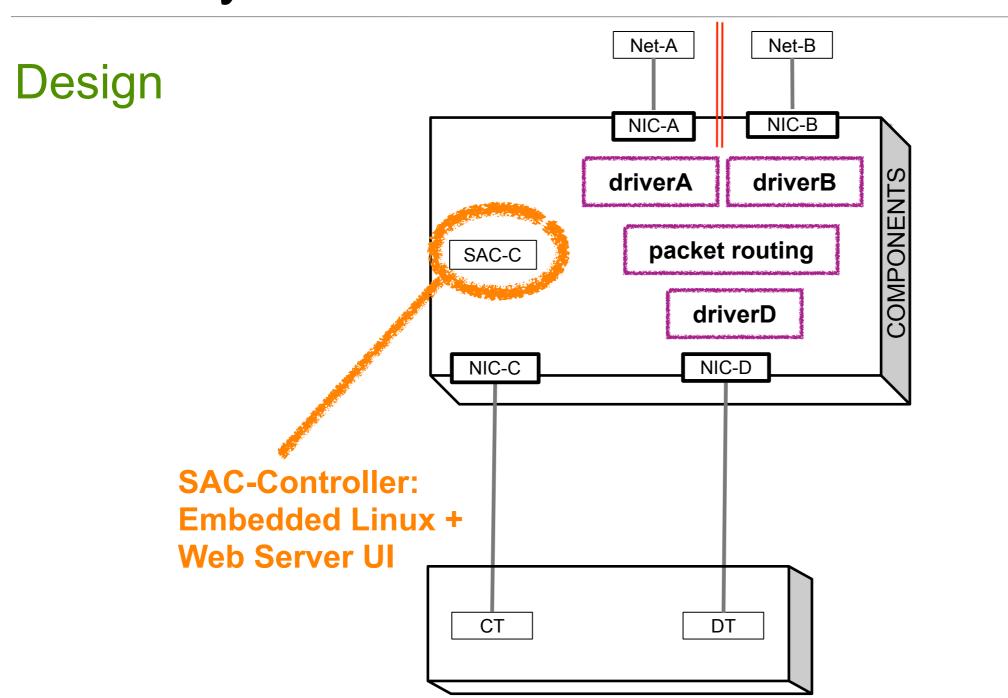

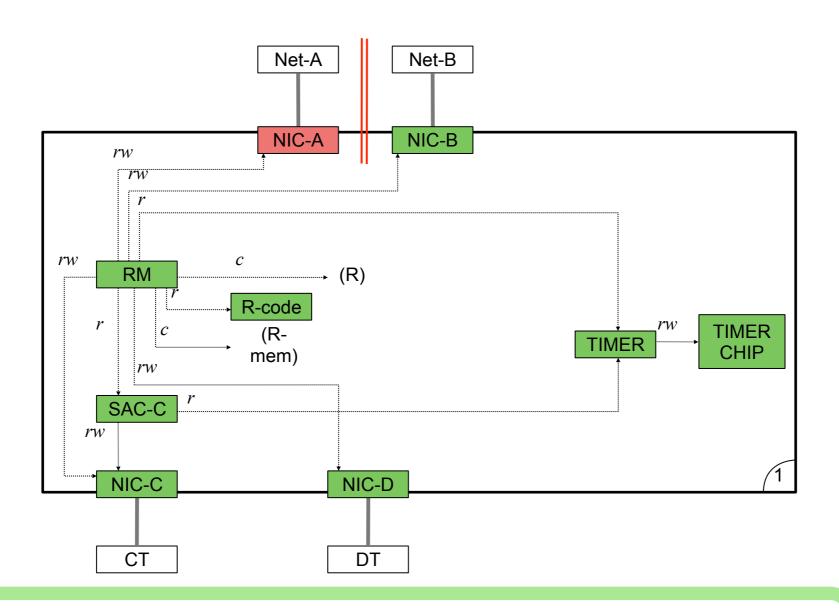

#### Design

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

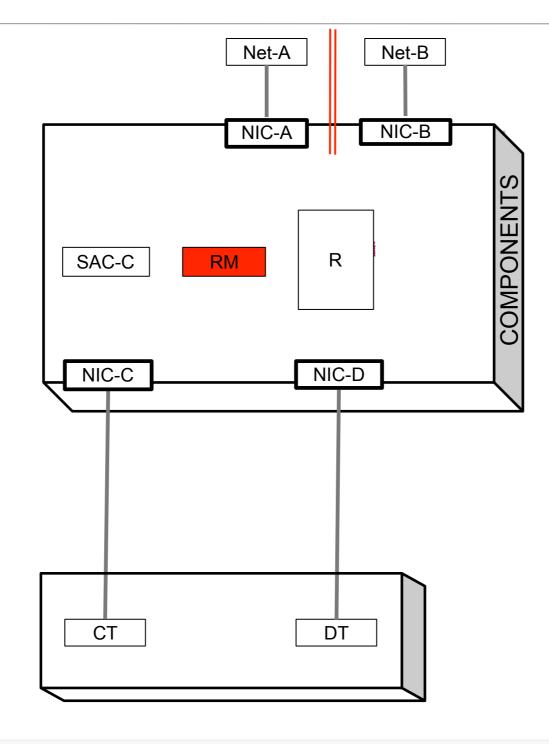

#### Design

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

DT = Data Terminal

R= Router

RM = Router Manager

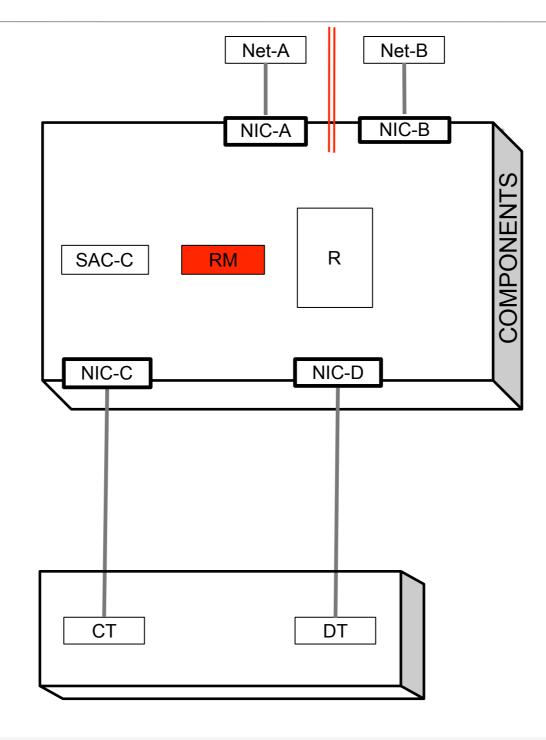

#### Design

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

DT = Data Terminal

R= Router

RM = Router Manager

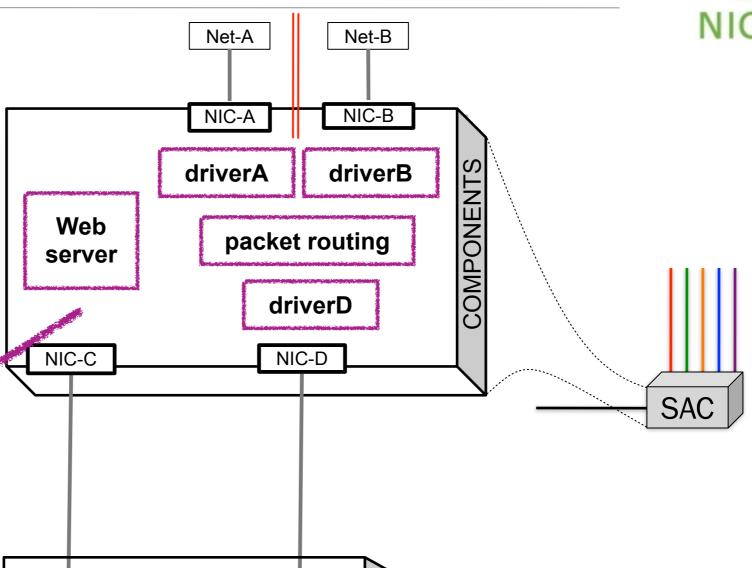

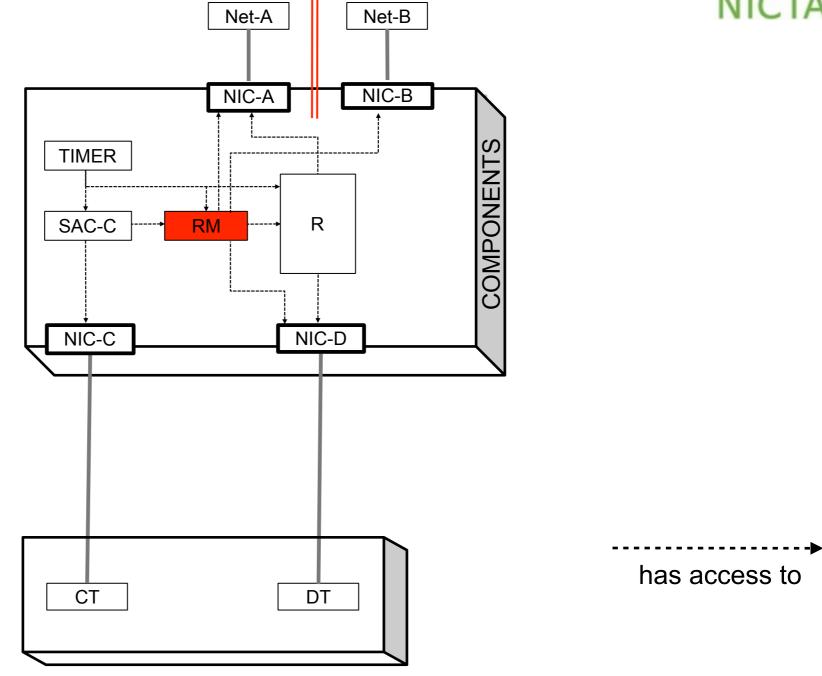

#### Design

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

DT = Data Terminal

R= Router

RM = Router Manager

## Design

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

DT = Data Terminal

R= Router

RM = Router Manager

Net-A = Network A

Net-B = Network B

NIC-A = Network Card for Network A

NIC-B = Network Card for Network B

NIC-C = Control Network Card

NIC-D = Data Network Card

CT = Control Terminal

DT = Data Terminal

R= Router

RM = Router Manager

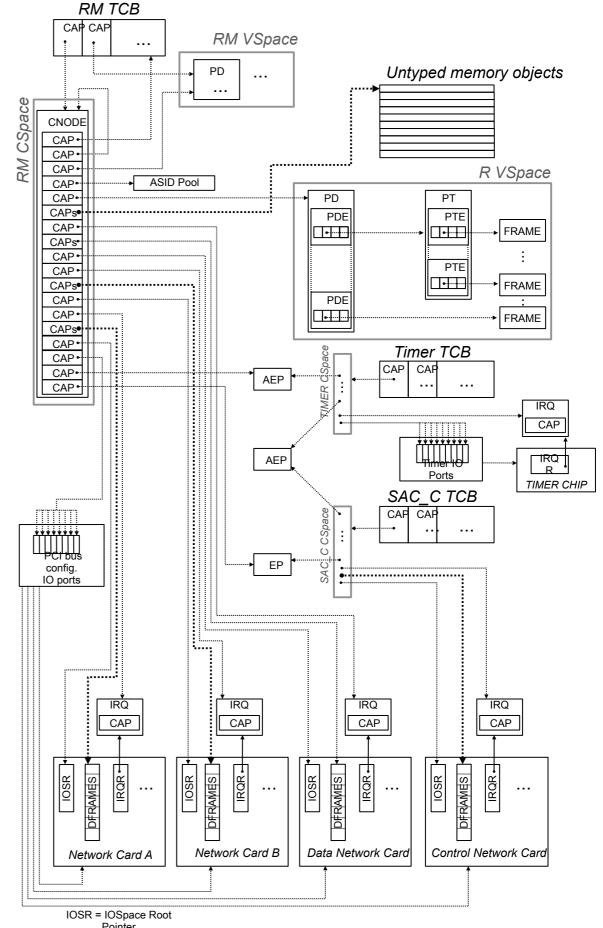

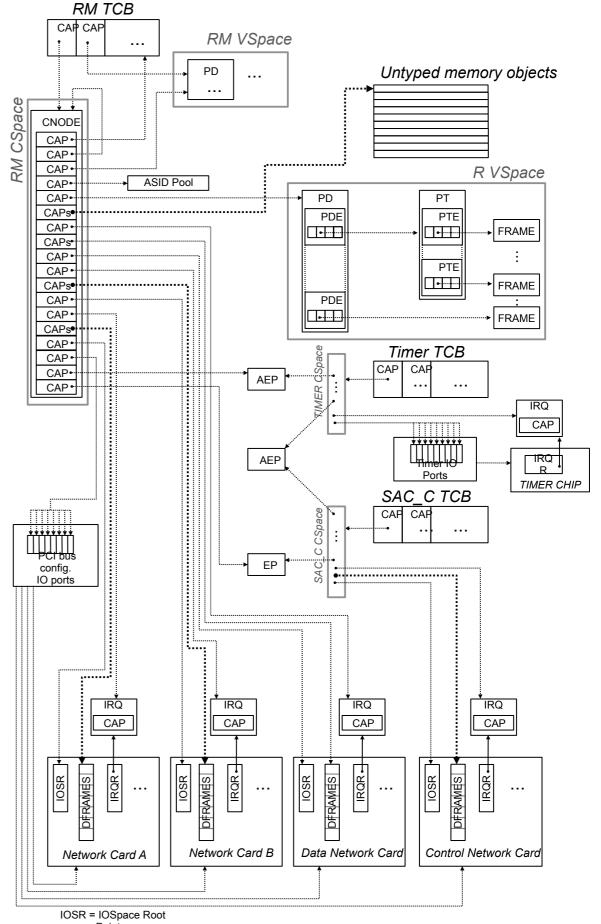

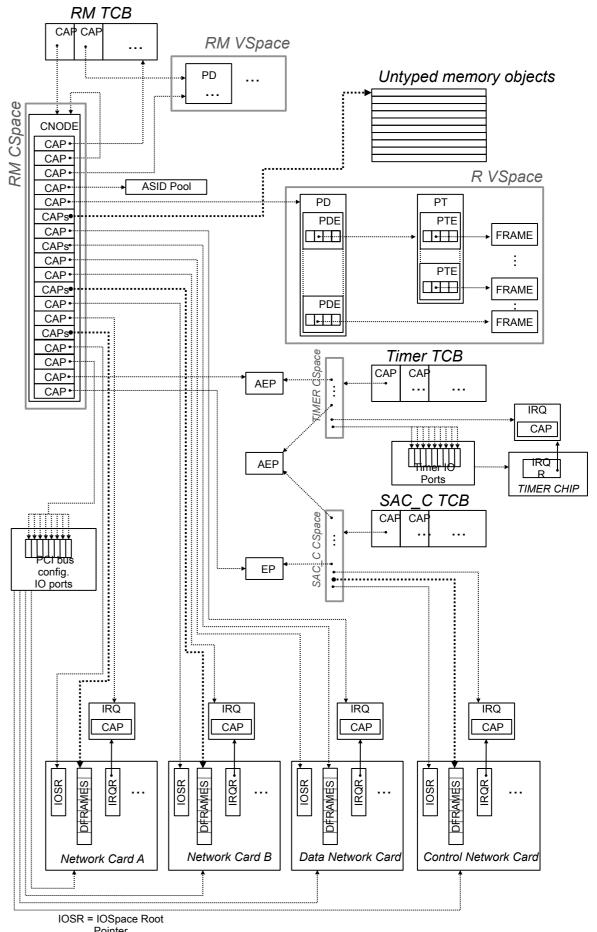

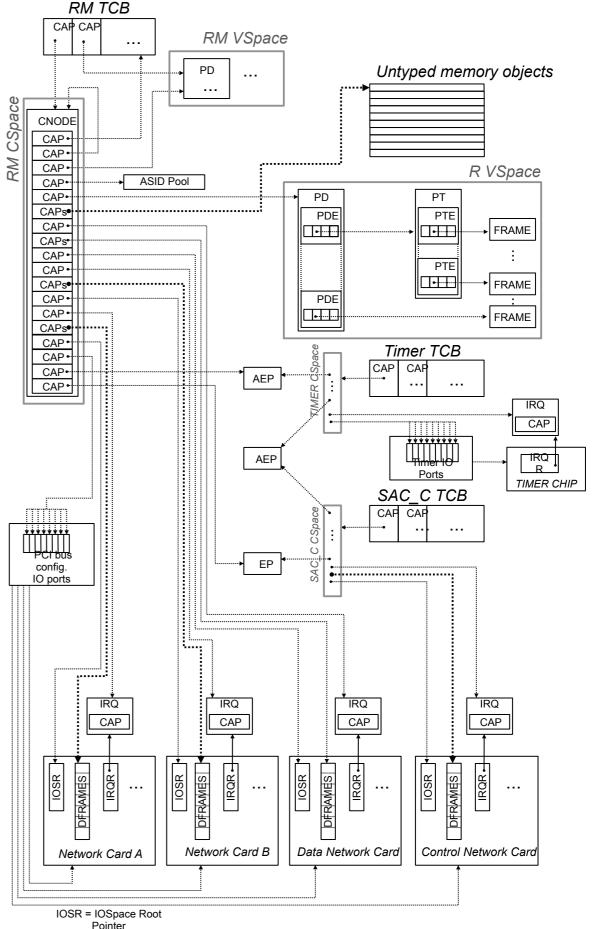

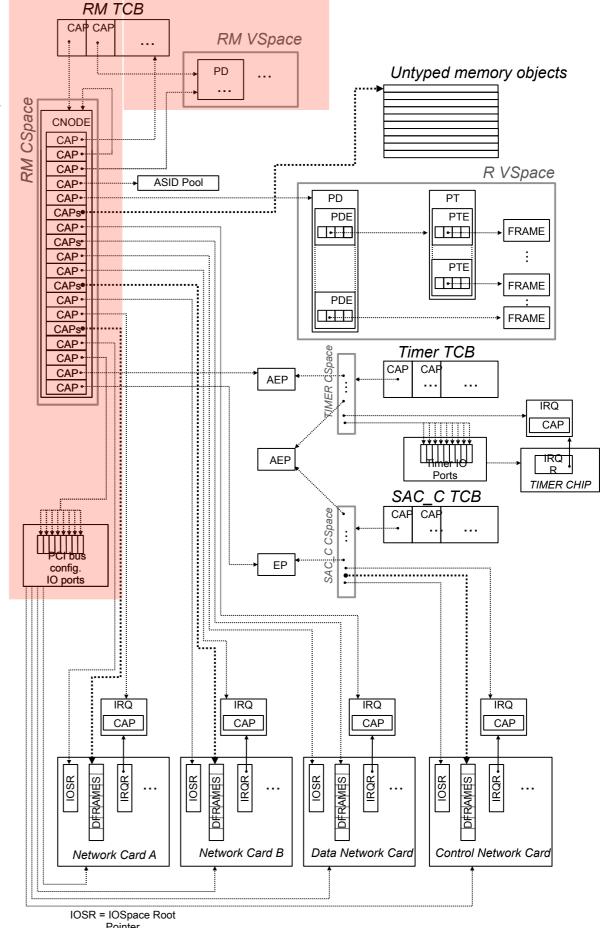

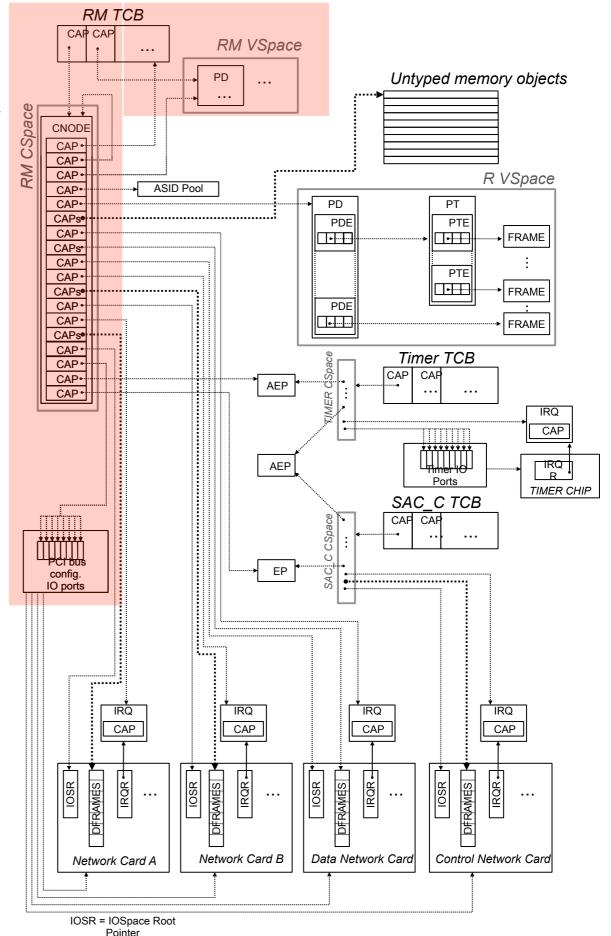

# Low-Level Design

#### Abstraction

Pointer

Pointer

IRQR = IRQ register

Pointer

IRQR = Pointer

IRQR = IRQ register

Pointer

IRQR = Pointer

IRQR = Device Frames

#### Security Goal

Goal: No information flowing between providers A and B Assumption: Info flow through front-end terminal is trusted

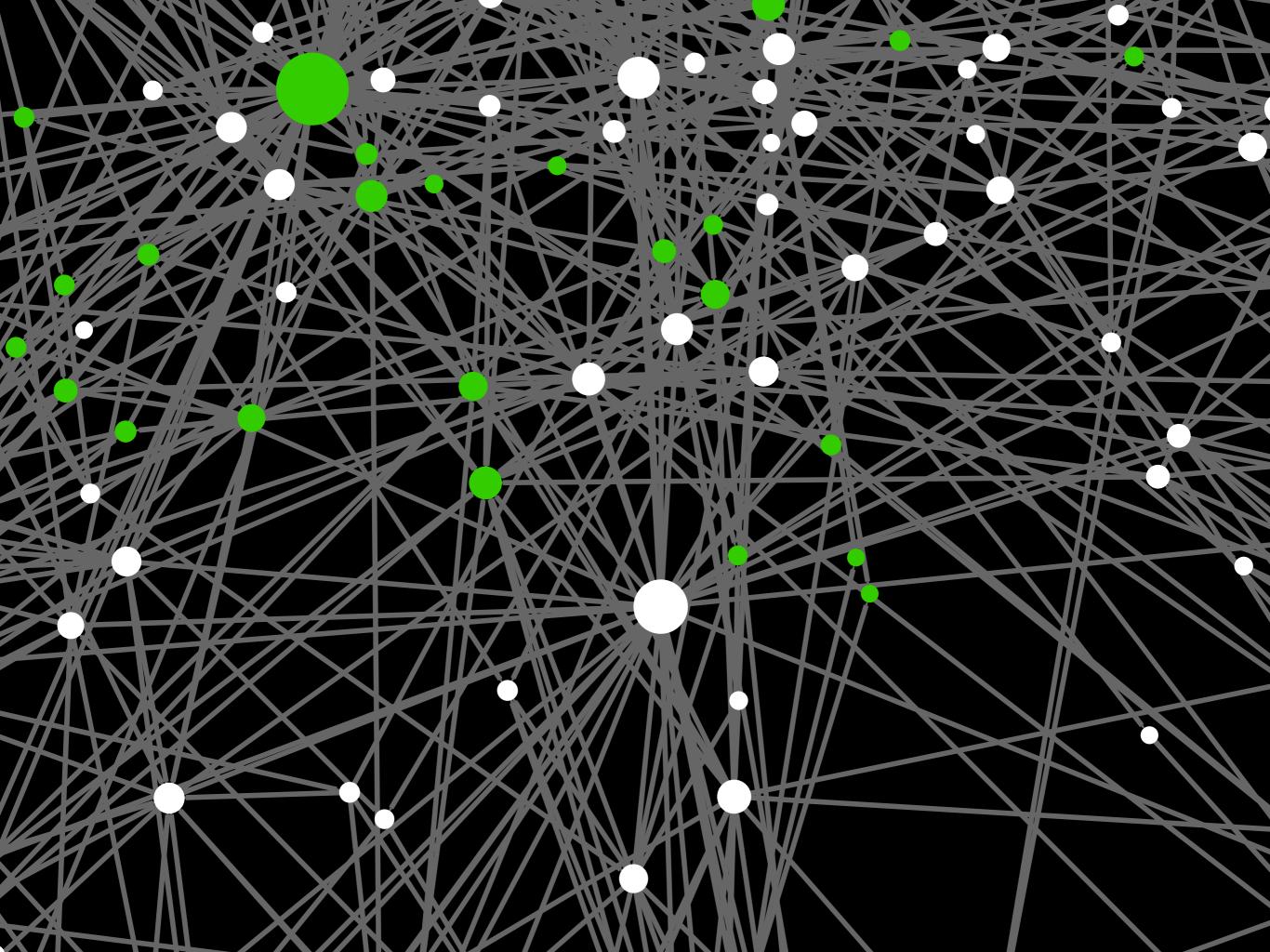

#### Plain Take-Grant Analysis

#### Plain Take-Grant Analysis

#### Plain Take-Grant Analysis

#### Security Goal

#### Approach:

- label-based security

- tag as 'contaminated' if may contain data from Net-A

- NIC-A always contaminated

- Goal: prove NIC-B always 'not contaminated'

# Security Analysis

#### So far

#### So far

- Can build systems with

- -large untrusted components

- -plus few small, trusted components

- –trusted = needs behaviour spec

#### So far

#### Can build systems with

- large untrusted components

- -plus few small, trusted components

- –trusted = needs behaviour spec

#### Use take-grant to model security

- can simulate system

- -modelling already finds bugs

- high-level proof in Isabelle/HOL or SPIN

- -includes behaviour of trusted component

#### **Future**

Pointer

IRQR = IRQ register

reference

DFRAMES = Device Frames

#### **Future**

Need to verify low-level design

IOSR = IOSpace Root

Pointer

IRQR = IRQ register

reference

DFRAMES = Device Frames

#### **Future**

Need to verify low-level design

- Building tool-chain for:

- -describing cap layout

(capDL)

- -generating booter

- -generating booter proof

- –abstraction to take-grant

#### More Future

IOSR = IOSpace Root

Pointer

IRQR = IRQ register

reference

DFRAMES = Device Frames

#### More Future

Verify Trusted Component

IOSR = IOSpace Root

Pointer

IRQR = IRQ register

reference

DFRAMES = Device Frames

#### More Future

VerifyTrusted Component

#### Refine to C:

- -interface with kernel

- use most abstract level possible

- make sure sec property preserved by refinement

# Summary

# Summary

#### Summary

#### Formal proof all the way from spec to C.

- 200kloc handwritten, machine-checked proof

- ~460 bugs (160 in C)

- Verification on code, design, and spec

- Systems with trusted components

- The future: formal proof for large systems down to code

#### Formal Code Verification up to 10kloc:

It works.

It's feasible.

It's fun.

# Thank You

# Thank You