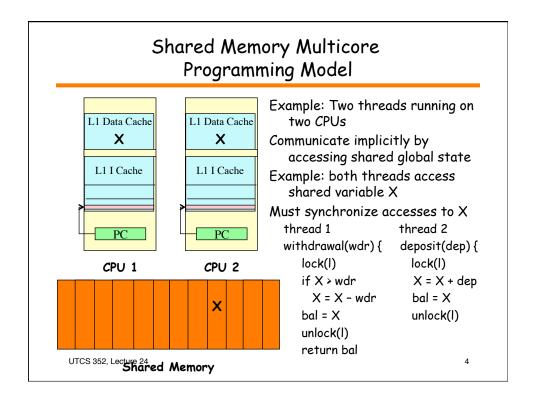

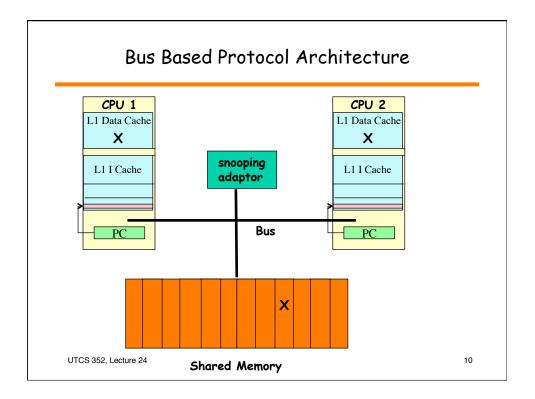

## Shared Memory Cache Coherence Problem

- Two threads share variable X

- Hardware

- Two CPUs, write-through caches

| Time<br>step | Event               | CPU 1's<br>cache | CPU 2's<br>cache | Memory |

|--------------|---------------------|------------------|------------------|--------|

| 0            |                     |                  |                  | 10     |

| 1            | CPU 1 reads X       | 10               |                  | 10     |

| 2            | CPU 2 reads X       | 10               | 10               | 10     |

| 3            | CPU 1 writes 1 to X | 5                | 10               | 5      |

5

UTCS 352, Lecture 24

| Only one cache ever holds a block in M or E state<br>Supports write back at invalidation time |                  |         |         |        |

|-----------------------------------------------------------------------------------------------|------------------|---------|---------|--------|

| CPU activity                                                                                  | Bus activity     | CPU 1's | CPU 2's | Memory |

|                                                                                               |                  | cache   | cache   | 10     |

|                                                                                               |                  |         |         | 10     |

| CPU 1 reads X                                                                                 | Cache miss for X |         |         | 10     |

| CPU 2 reads X                                                                                 | Cache miss for X |         |         | 10     |

| CPU 1 writes 5 to X                                                                           | Invalidate for X |         |         |        |

| CPU 2 read X                                                                                  | Cache miss for X |         |         |        |

|                                                          |                                      | xamp             | U                |          |

|----------------------------------------------------------|--------------------------------------|------------------|------------------|----------|

| Only one cache ever holds the data in either M or E mode |                                      |                  |                  |          |

| Supports writ                                            | e back at inval                      | lidation ti      | me               |          |

|                                                          |                                      |                  |                  |          |

| CPU activity                                             | Bus activity                         | CPU 1's cache    | CPU 2's<br>cache | Memory   |

|                                                          |                                      |                  |                  |          |

|                                                          |                                      |                  |                  | 10       |

| CPU 1 reads X                                            | Cache miss for X                     | 10 (E)           |                  | 10<br>10 |

| CPU 1 reads X<br>CPU 2 reads X                           | Cache miss for X<br>Cache miss for X | 10 (E)<br>10 (I) | 10 (E)           |          |

|                                                          |                                      |                  | 10 (E)<br>10 (I) | 10       |

| MSI Example                   |                                                       |                  |                  |              |  |

|-------------------------------|-------------------------------------------------------|------------------|------------------|--------------|--|

| Only one cache                | es may hold a b<br>e holds a block<br>e back at inval | in M stat        | te               |              |  |

| Supports write                | e buck ut mvul                                        |                  |                  |              |  |

| CPU activity                  | Bus activity                                          | CPU 1's<br>cache | CPU 2's<br>cache | Memory       |  |

|                               |                                                       | CPU 1's          | CPU 2's          | Memory<br>10 |  |

|                               |                                                       | CPU 1's          | CPU 2's          |              |  |

| CPU activity                  | Bus activity                                          | CPU 1's          | CPU 2's          | 10           |  |

| CPU activity<br>CPU 1 reads X | Bus activity<br>Cache miss for X<br>Cache miss for X  | CPU 1's          | CPU 2's          | 10<br>10     |  |

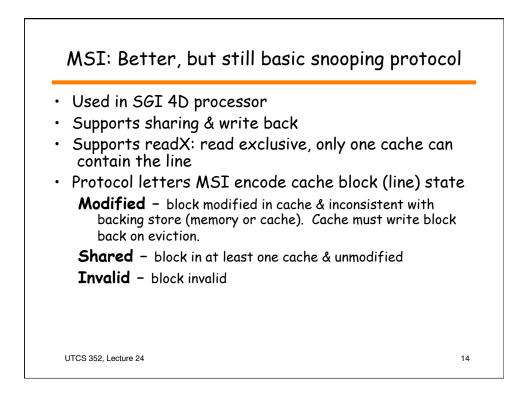

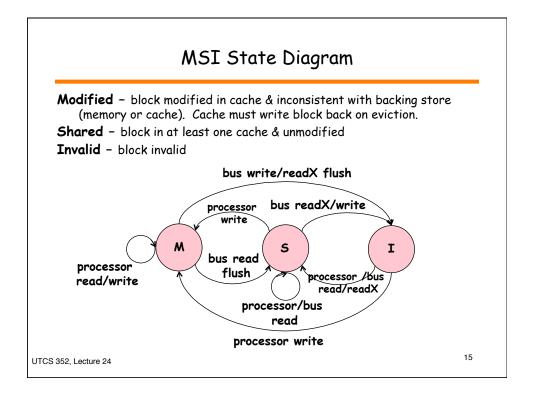

## MSI Example

Multiple caches may hold a block in S state Only one cache holds a block in M state Supports write back at invalidation time

|              | 10                               |

|--------------|----------------------------------|

|              | 1 10                             |

| ) (S)        | 10                               |

| 0 (S) 10 (S) | 10                               |

| (M) 10 (I)   | 10                               |

| 5 (I) 5 (S)  | 5                                |

|              | Image: 0 (S) 10 (S)   (M) 10 (I) |