#

© 2017 Arm Limited

Engineering and Use of Large Formal Specifications

### Alastair Reid Arm Research @alastair d reid

Internet of Things

#### Data

#### Performance

# Machine Learning

### Smart Homes

### Self Driving Cars Social Media

Bugs Crashes Data loss Data corruption Data leaks / theft DDoS attacks Cyber-Physical attacks

### Better Programming Languages

### Better System Design

Hardware Security Enforcement Formal Verification Better Bug Finding

### Regulatory

### Exploit Detection

### Automatic **Test** Generation

### Fuzz Testing Orm

#### **Orm**

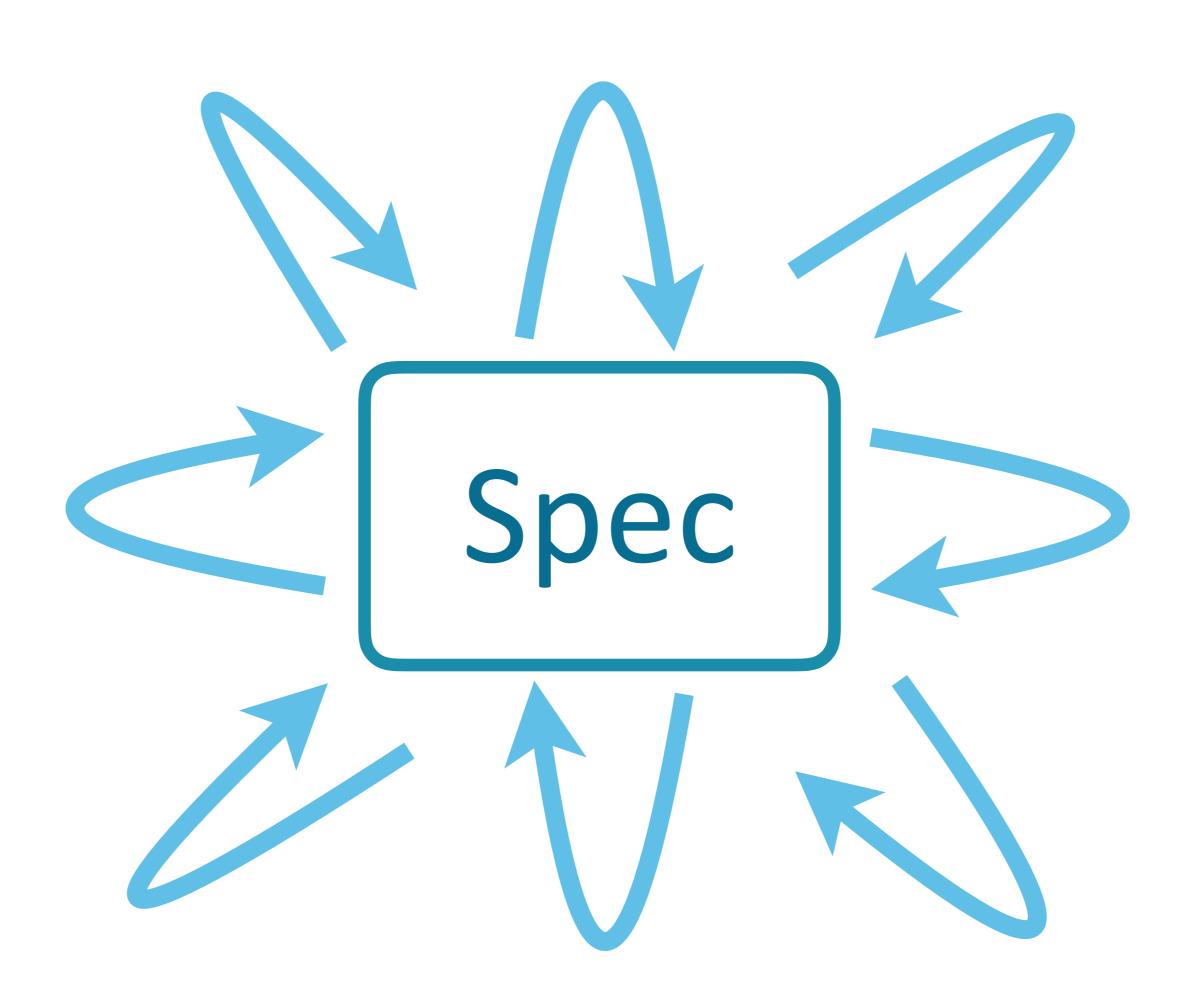

#### Specification

#### Specification

#### Specification

### What (formal) specifications do we need?

Libraries: stdio.h, OpenGL, ... Filesystems: FAT32, NTFS, ext4, ...

- Languages: C, C++, ML, Javascript, Verilog, ...

- Network: TCP/IP, OAuth, DNS, TLS, WiFi, ...

- Hardware: CPU, PCIe, AMBA, NIC, ...

**OSes:** Posix/Linux system call, Linux device driver, KVM, UEFI, ...

### **Critical properties of specifications**

### Scope - Completeness - Not abstracting out critical detail Applicability - Version agnostic - Vendor agnostic Trustworthiness

### **Overcoming the Specification Bottleneck**

Creating formal specifications Testing specifications Getting buy in Using specifications

> "Trustworthy Specifications of the ARM v8-A and v8-M architecture," FMCAD 2016 "End to End Verification of ARM processors with ISA Formal," CAV 2016 "Who guards the guards? Formal Validation of ARM v8-M Specifications," OOPSLA 2017 "ISA Semantics for ARM v8-A, , RISC-V, and CHERI-MIPS," POPL 2019

© 2017 Arm Limited

# Formal validation of specifications Making your specifications public

#### https://alastairreid.github.io/papers/

# Creating formal specifications Testing specifications Getting buy in

© 2017 Arm Limited

"Trustworthy Specifications of the ARM v8-A and v8-M architecture," FMCAD 2016

instruction, behavior is consistent with execution of either:

If one thread of execution changes a conditional branch instruction, such as B or BL, to another conditional instruction and the change affects both the condition field and the branch target, execution of the changed instruction by another thread of execution before the change is synchronized can lead to either: The old condition being associated with the new target address.

#### The ARMv8 architecture limits the set of instructions that can be executed by one thread of execution as they are Concurrent modification and execution of instructions being modified by another thread of execution without requiring explicit synchronization. Concurrent modification and execution of instructions can lead to the resulting instruction performing any behavior that can be achieved by executing any sequence of instructions that can be executed from the same Exception level, except where each of the instruction before modification and the instruction after modification is one of a B, BL, BRK,

For the B, BL, BRK, HVC, ISB, NOP, SMC, and SVC instructions the architecture guarantees that, after modification of the

These possibilities apply regardless of whether the condition, either before or after the change to the branch instruction, is the *always* condition.

#### **R**<sub>JRJC</sub>

HVC, IDD,

For the B, BL, BRK, HVC, ISB, NOP, SML, and instruction, behavior is consistent with execution of enu-

If one thread of execution changes a conditional branch instruction, such as B or BL, to another conditional instruction and the change affects both the condition field and the branch target, execution of the changed instruction by another thread of execution before the change is synchronized can lead to either: The old condition being associated with the new target address. These possibilities apply regardless of whether the condition, either before or after the change to the branch instruction, is the *always* condition.

acution of instructions Exit from lockup is by any of the following: A Cold reset. • A Warm reset. Entry to Debug state. Preemption by a higher priority exception. •

avecuted by one thread of execution as they are

any behavior ception level, of a B, BL, BRK,

ification of the

#### R<sub>JRJC</sub>

HVC, IDD,

٠

٠

| <b>ions</b> $bv$ one three $bv = be^{1}$                                                                  |

|-----------------------------------------------------------------------------------------------------------|

| any of the f<br>any of the f<br>on causes: with the exception to be<br>on causes: pending or active.      |

| on causes:<br>ers associated with the crive.<br>ers associate, pending or active.<br>ption state, pending |

| on cause iated ing or a                                                                                   |

| ers a state, P                                                                                            |

| OXEFFFFFF.<br>OXEFFFFFFVOWN. 1.                                                                           |

| $0 \times EFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF$                                                           |

| CED_to either:                                                                                            |

| w target addresse                                                                                         |

| old target address.                                                                                       |

updated.

alinstruction tion by another

branch

#### R<sub>JRJC</sub>

#### Accesses

Before the barrier

Reads and writes

Writes

Reads

RVGI

| Exit              | From lockup                                                                                                       | tructions<br>is by any of the f<br>able B2-1 Encoding                                       | *101                       | opti |  |  |  |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------|------|--|--|--|--|--|--|--|--|--|

|                   | Shareability domain                                                                                               |                                                                                             |                            |      |  |  |  |  |  |  |  |  |  |

| After the barrier | Full system                                                                                                       | Outer Shareable                                                                             | Inner Shareable            | No   |  |  |  |  |  |  |  |  |  |

| Reads and writes  | SY                                                                                                                | OSH                                                                                         | ISH                        | NSH  |  |  |  |  |  |  |  |  |  |

| Writes            | ST                                                                                                                | OSHST                                                                                       | ISHST                      | NSH  |  |  |  |  |  |  |  |  |  |

| Reads and writes  | LD                                                                                                                | OSHLD                                                                                       | ISHLD                      | NSH  |  |  |  |  |  |  |  |  |  |

|                   | The True<br>The True<br>EPSR.True<br>HERS<br>addition, HERS<br>addition, with<br>addition, with<br>addition, with | <b>R.F.</b> w target address.<br>th the old target address.<br>er the condition, either bef | ore or after the change to | theb |  |  |  |  |  |  |  |  |  |

ys condition.

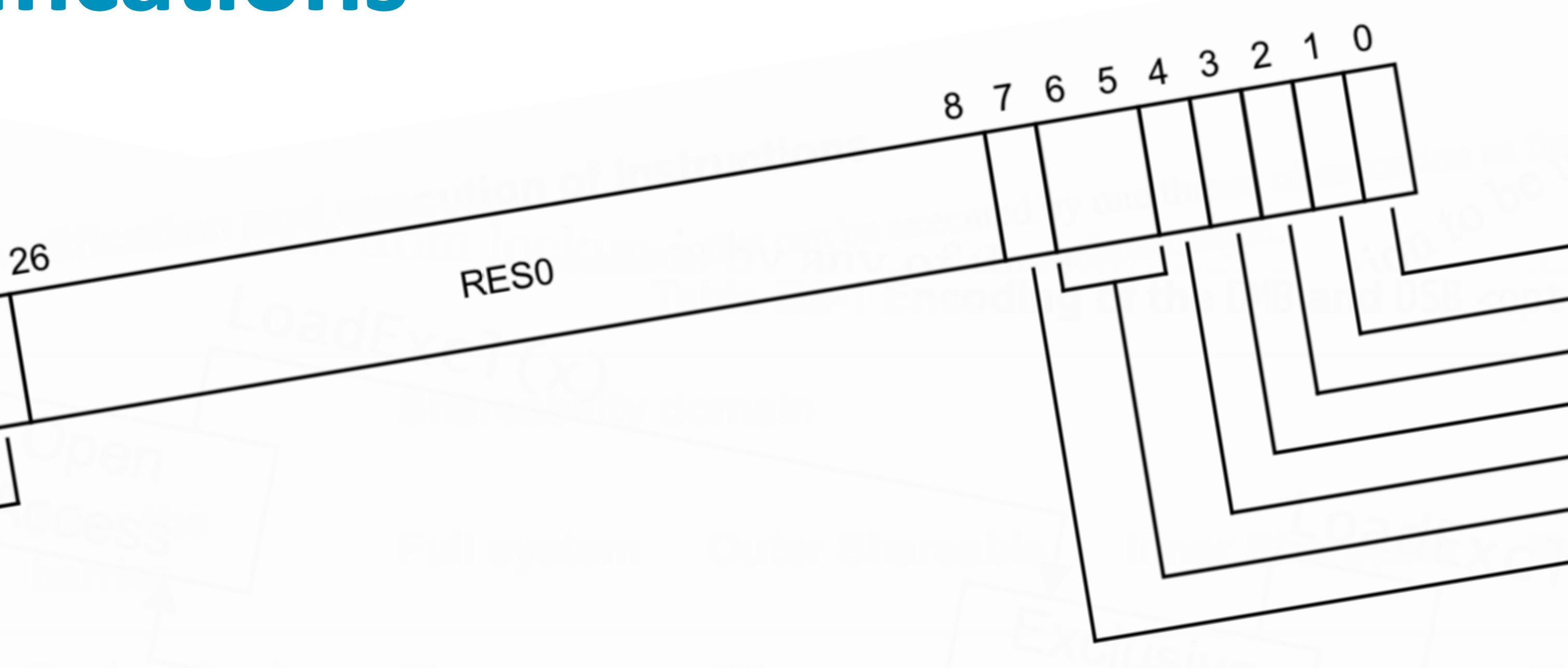

# cion> parameter

updated.

#### on-shareable

HST

HLD

branch

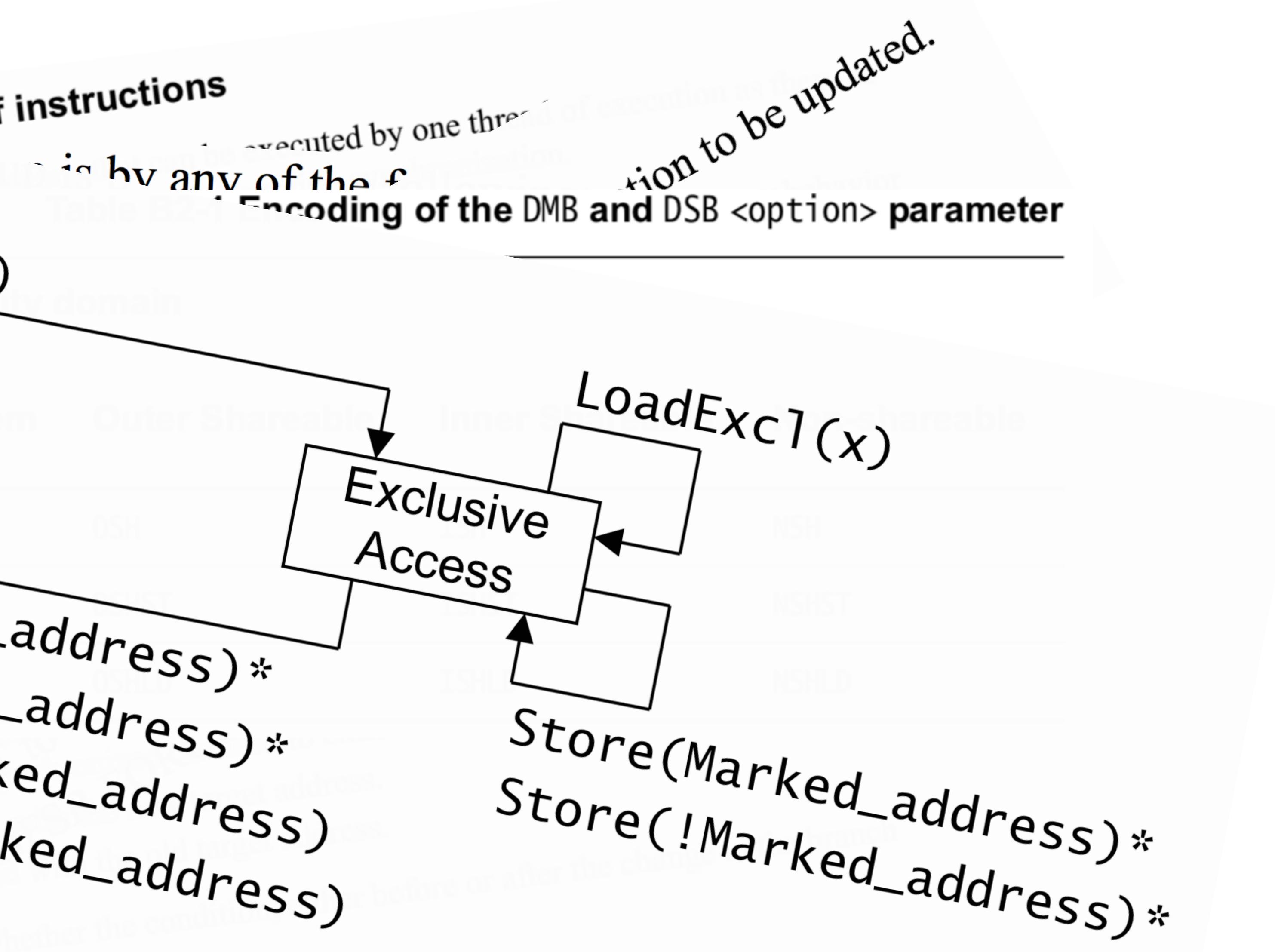

### StoreExcl(x) Store(x)CLREX

© 2017 Arm Limited 10

oution of instructions LoadExc1(x)Open Access Store(Marked\_address)\* Store(!Marked\_address)\* StoreExcl(Marked\_address) StoreExcl(!Marked\_address)

In a less un ys condition.

31 30 29 28 27 26 Ν

N, bit [31]

Z, bit [30]

© 2017 Arm Limited 10

QC

Negative condition flag for AArch32 floating-point comparison operations. A Arch64 floating-point comparisons set the PSTATE.N flag instead. Zero condition flag for AArch32 floating-point comparison operations. AArch64 floating-point comparisons set the PSTATE.Z flag instead.

Typ conunon.

-'Ked\_address)\*

| - 10C  |       |

|--------|-------|

| - DZC  | neter |

| _ OFC  |       |

| UFC    |       |

| IXC    |       |

| - RESO |       |

| IDC    |       |

|        |       |

### **Pseudocode**

$ADC{S}<<> <Rd>, <Rm>, <Rm>{, <shift>}$

| 31 30 29 28 | 27 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13   | 12 | 11 | 10 | 9 | 8  | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|-------|----|----|----|----|----|----|----|----|----|----|----|----|------|----|----|----|---|----|----|---|---|---|---|---|---|---|

| cond        | 0 0   | 0  | 0  | 1  | 0  | 1  | S  |    | Rn |    | Rd |    |    | imm5 |    |    |    |   | ty | pe | 0 |   | R | m |   |   |   |

if Rd -- '1111' && S -- '1' then SEE SUBS PC, LR and related instructions; d = UInt(Rd); n = UInt(Rn); m = UInt(Rm); setflags = (S == '1'); (shift\_t, shift\_n) = DecodeImmShift(type, imm5);

if ConditionPassed() then EncodingSpecificOperations(); shifted = Shift(R[m], shift\_t, shift\_n, APSR.C); (result, carry, overflow) = AddWithCarry(R[n], shifted, APSR.C) if d -- 15 then // Can only occur for ARM encoding ALUWritePC(result); // setflags is always FALSE here else R[d] = result; if setflags then APSR.N - result<31>; APSR.Z = IsZeroBit(result); APSR.C - carry; APSR.V - overflow;

### **ARM Pseudocode**

#### ~40,000 lines

- 32-bit and 64-bit modes

### - All 4 privilege levels (User, Supervisor, Hypervisor, Secure Monitor) - Both Security modes (Secure / NonSecure) - MMU, Exceptions, Interrupts, Privilege checks, Debug, TrustZone, ...

### - All instructions (> 1300 encodings)

- All 4 encodings: Thumb16, Thumb32, ARM32, ARM64

### Status at the start

- No language spec

- Unexecuted, untested

- - Impossible

- Not useful

- - Less readable

- Less correct

# - No tools (parser, type checker) - Incomplete (around 15% missing) - Senior architects believed that an executable spec was

### **Architectural Conformance Suite**

### Processor architectural compliance sign-off

#### Large

### Thorough Tests dark corners of specification

# Hard to run

v8-A 32,000 test programs, billions of instructions v8-M 3,500 test programs, > 250 million instructions

Requires additional testing infrastructure

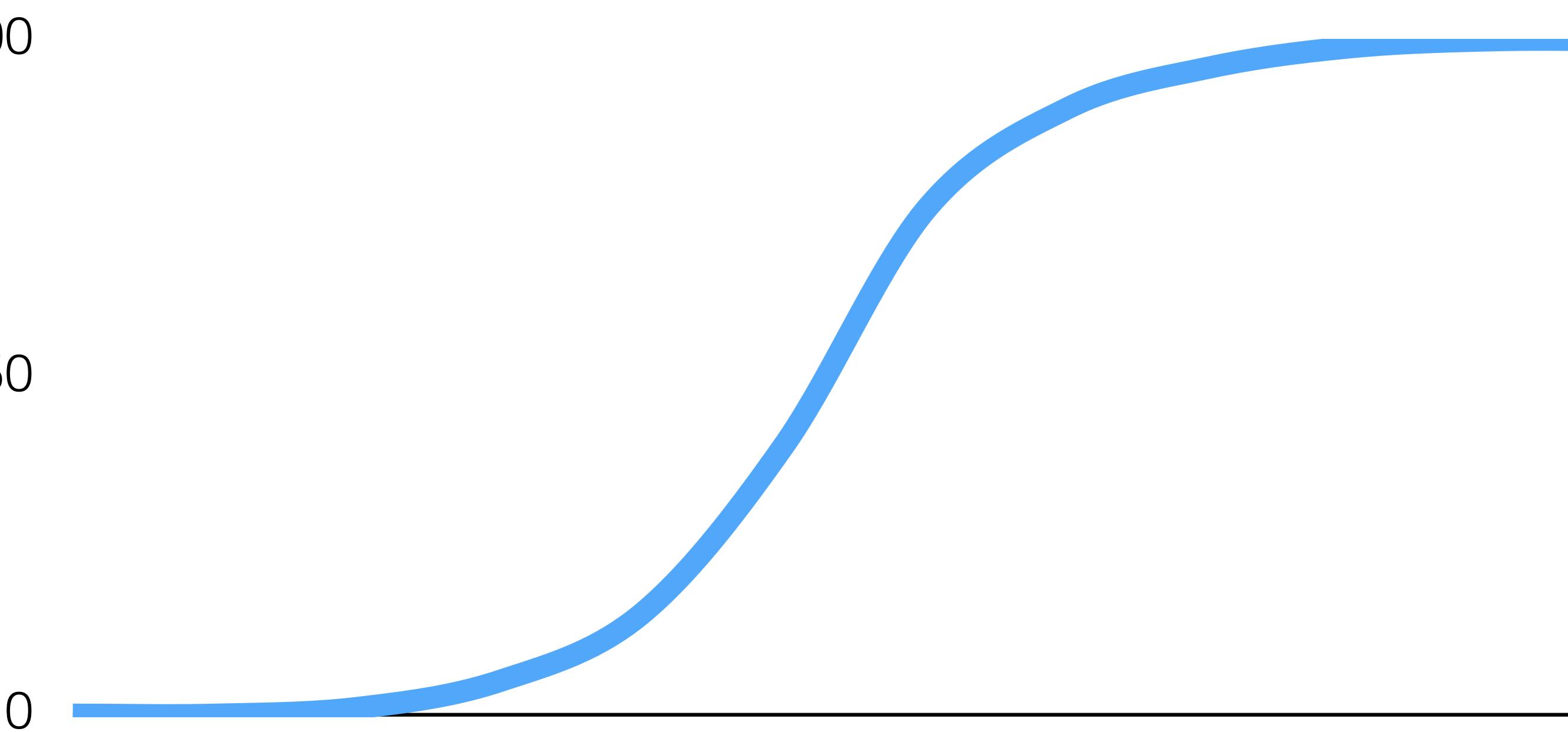

#### 100

50

© 2017 Arm Limited

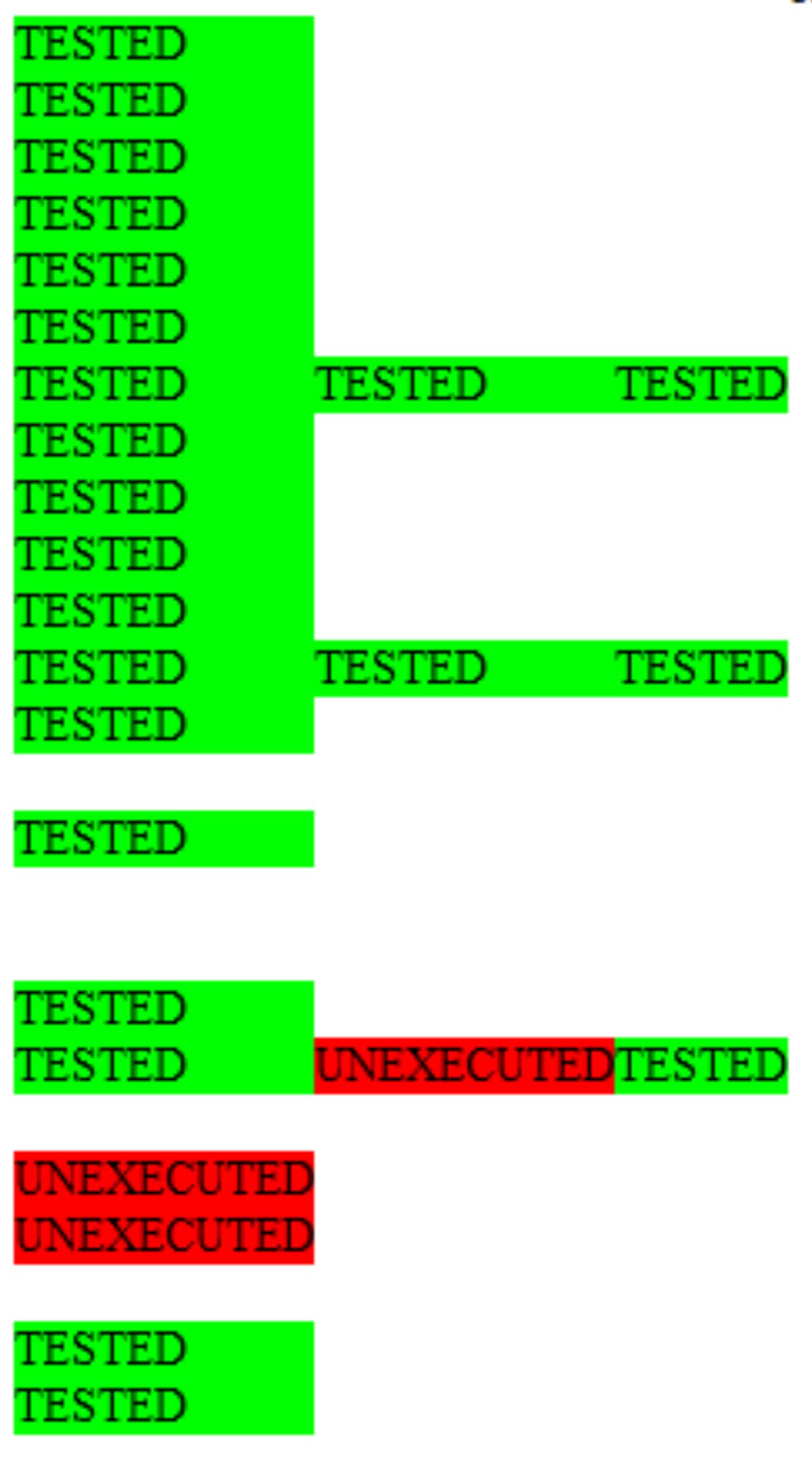

### **Progress in testing Arm specification**

- Does not parse, does not typecheck

- Can't get out of reset

- Can't execute first instruction

- Can't execute first 100 instructions

- Passes 90% of tests Passes 99% of tests

### Measuring architecture coverage of tests

#### Untested: op1\*op2 == -3.0, FPCR.RND=-Inf

© 2017 Arm Limited 16

```

bits(N) FPRSqrtStepFused(bits(N) op1, bits(N) op2)

assert N IN {32, 64};

bits(N) result;

op1 = FPNeg(op1); // per FMSUB/FMLS

(type1,sign1,value1) = FPUnpack(op1, FPCR);

(type2,sign2,value2) = FPUnpack(op2, FPCR);

(done,result) = FPProcessNaNs(type1, type2, op1, op2, FPCR);

if !done then

inf1 = (type1 == FPType Infinity);

inf2 = (type2 == FPType_Infinity);

zero1 = (type1 == FPType Zero);

zero2 = (type2 == FPType Zero);

if (inf1 && zero2) || (zero1 && inf2) then

result = FPOnePointFive('0');

elsif inf1 || inf2 then

result = FPInfinity(sign1 EOR sign2, N);

else

// Fully fused multiply-add and halve

result value = (3.0 + (value1 * value2)) / 2.0;

if result value == 0.0 then

// Sign of exact zero result depends on rounding mode

sign = if FPCRRounding() == FPRounding_NEGINF then '1' else '0';

result = FPZero(sign, N);

else

result = FPRound(result_value, FPCRRounding());

return result;

```

#### © 2017 Arm Limited 17

# Creating a Virtuous Cycle

#### **Orm**

### Lessons learned about engineering a specification

# **Specifications contain bugs** - Creates Virtuous Cycle

- Huge value in being able to run existing test suites

- Need to balance against benefits of non-executable specs

- Find ways to provide direct benefit to other users of spec

- They will do some of the testing/debugging for you

- They will support getting your changes/spec adopted as master spec

Orm

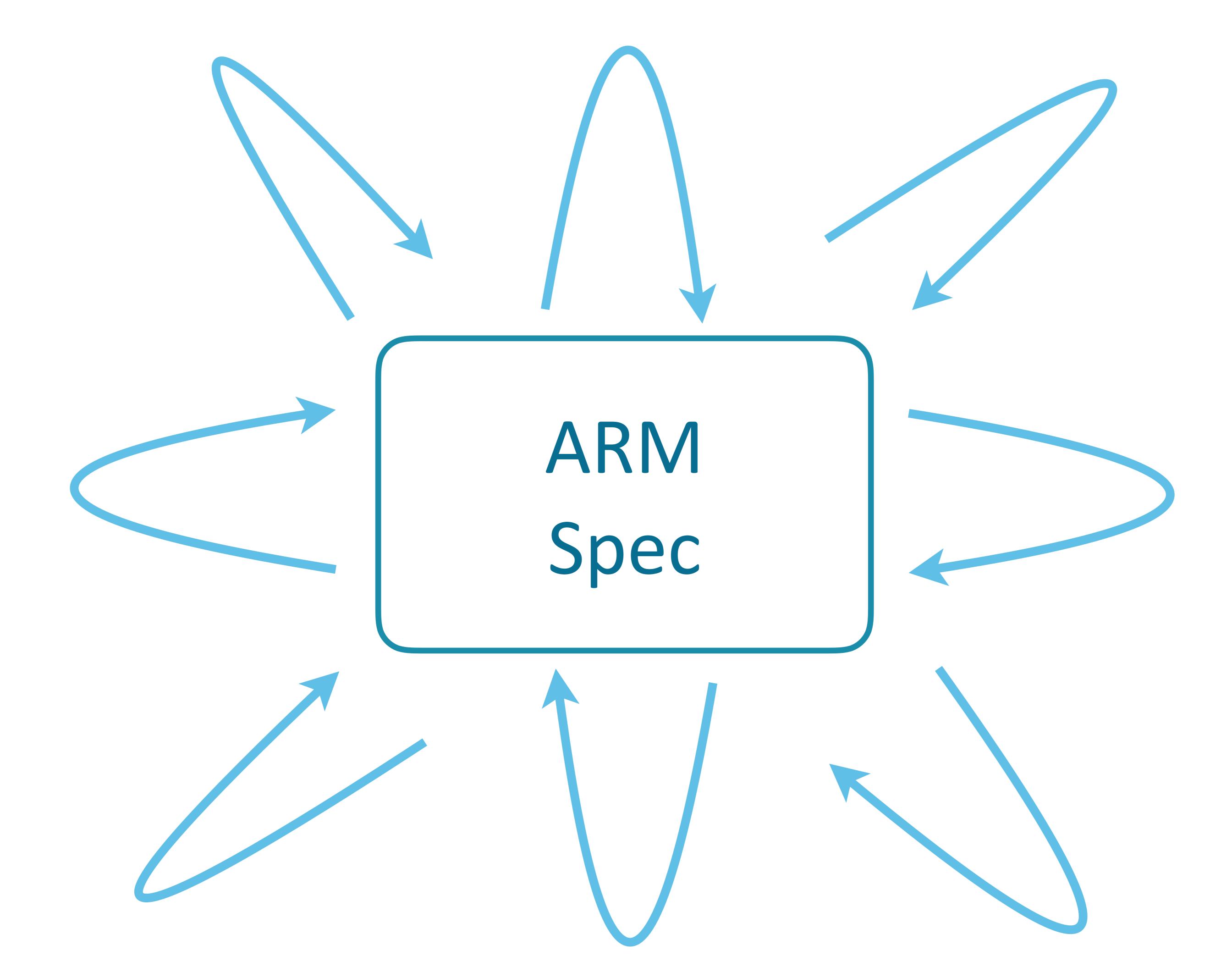

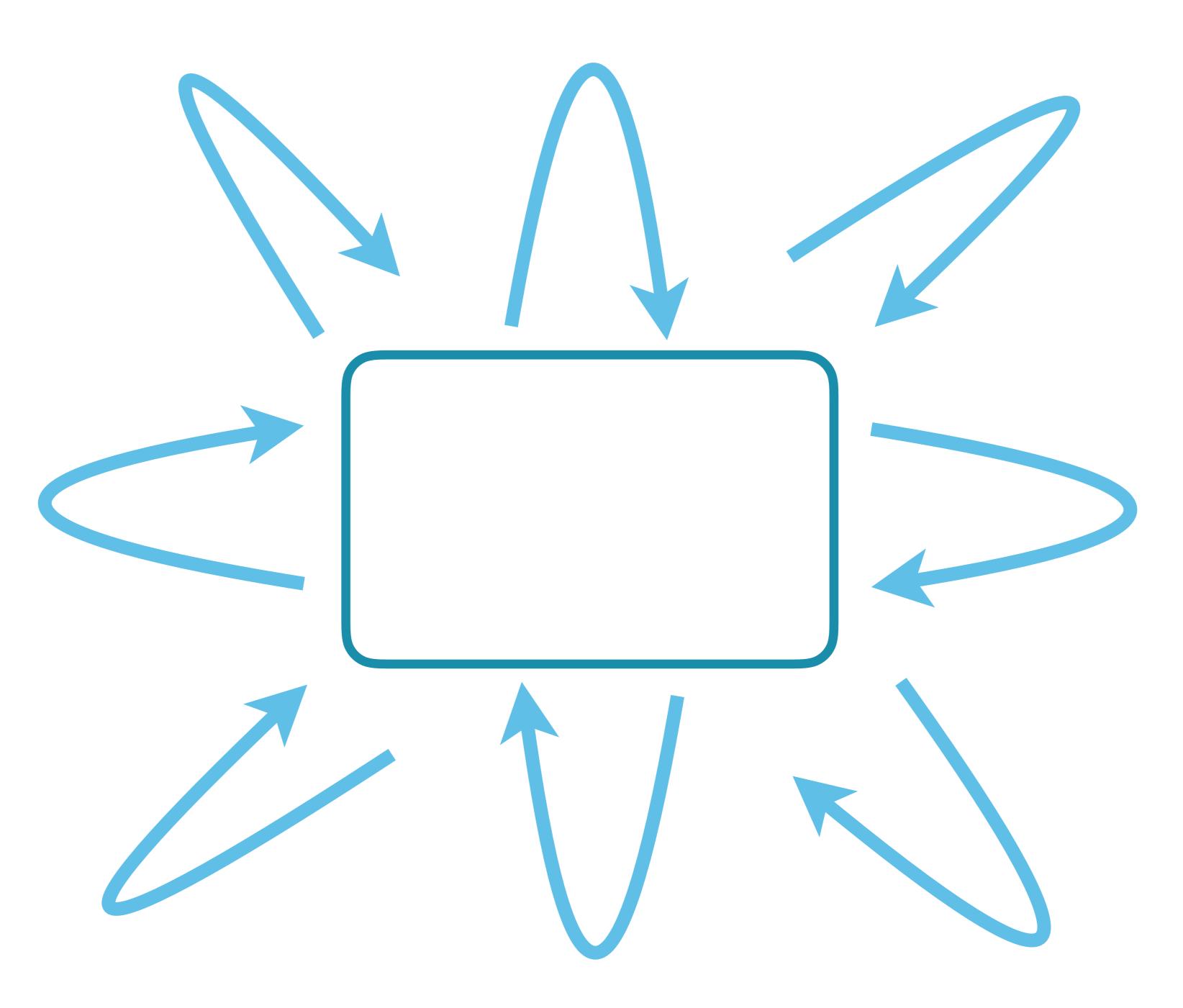

## Using Specifications

© 2017 Arm Limited 19

"End to End Verification of ARM processors with ISA Formal," CAV 2016

Documentation - Generate PDF/HTML - Interactive specifications

#### Verification of Implementations - Bounded Model Checking - Testing (Golden Reference) - Deductive Reasoning

#### **Specification Extension** - Testing / Exploration

#### **Instrumented Execution** - Measure Coverage - Driving Fuzz Testing

#### Generation

- Testsuites (Concolic)

- Simulators

- Peephole Optimisations

- Binary Translators

#### Verification of Clients - Formally verifying OS code / etc. - Verifying Compilers/Linkers

#### Static Analysis

- Abstract interpretation of binaries

- Decompilation of binaries

- Reverse engineering tools

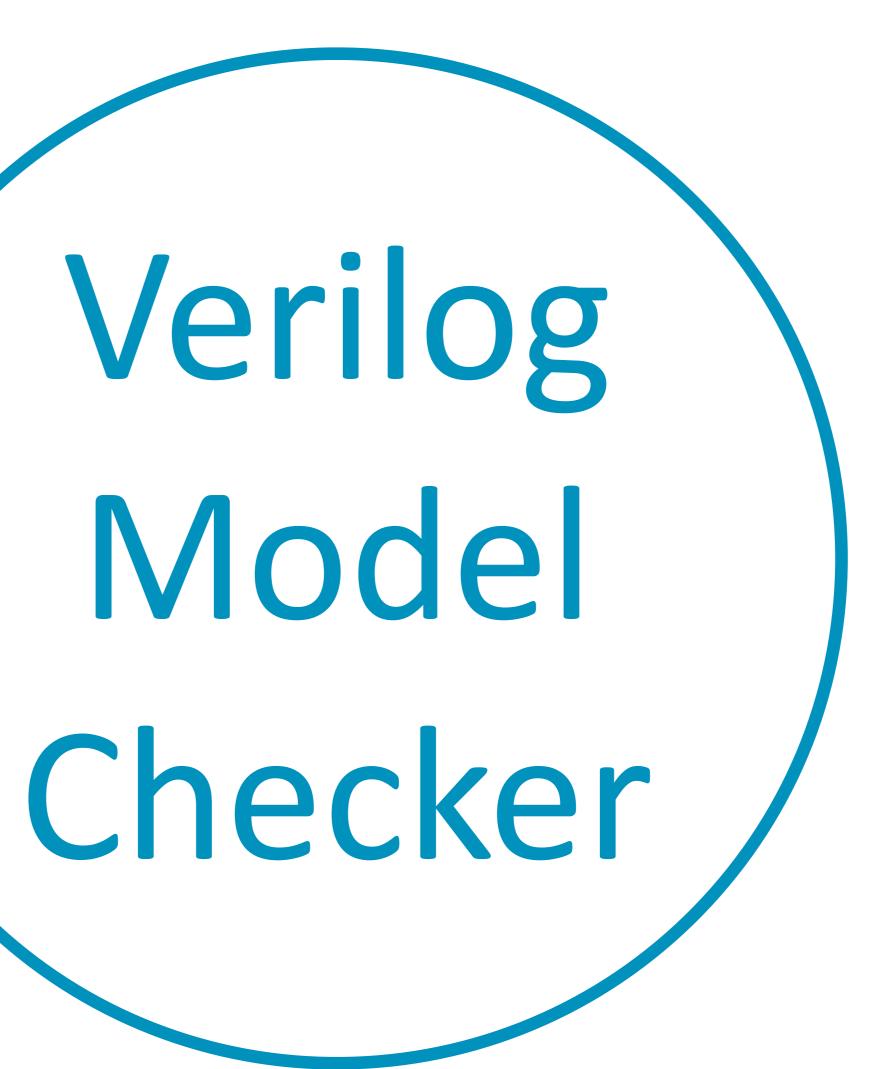

### Formally validating ARM processors - using an existing tool

#### © 2017 Arm Limited 21

### ARM Processor

#### Specification

#### Translate to Verilog

#### 22 © 2017 Arm Limited

# Checking an instruction

Orm

#### © 2017 Arm Limited 22

# Checking an instruction

### Lessons Learned from validating processors

# Very effective way to find bugs in implementations Formally validating implementation is effective at finding bugs in spec Try to find most of the bugs in your spec before you start Huge value in being able to use spec to validate implementations Helps get formal specification adopted as part of official spec

# Formal Validation of Specifications

© 2017 Arm Limited 24

#### **Orm** "Who guards the guards? Formal Validation of ARM v8-M Specifications" OOPSLA 2017

### **One Specification to rule them all?**

#### Compliance Tests

#### Architecture Spec

#### Processors

© 2017 Arm Limited

25

### Rule JRJC Exit from lockup is by any of the following: • A Cold reset. • A Warm reset. • Entry to Debug state. • Preemption by a higher priority processor exception.

Rule R • Event A • Event B State Change C • Event D

26 © 2017 Arm Limited

### Rule R **State Change X** is by any of the following: • Event A • Event B State Change C • Event D

### State Change

#### Event

#### Event

#### State Change

#### Event

© 2017 Arm Limited

### Exit from lockup A Cold reset

#### A Warm reset

### Entry to Debug state

Preemption by a higher priority processor exception

# Fell(LockedUp) Called(TakeColdReset) Called(TakeReset) Rose(Halted) Called(ExceptionEntry)

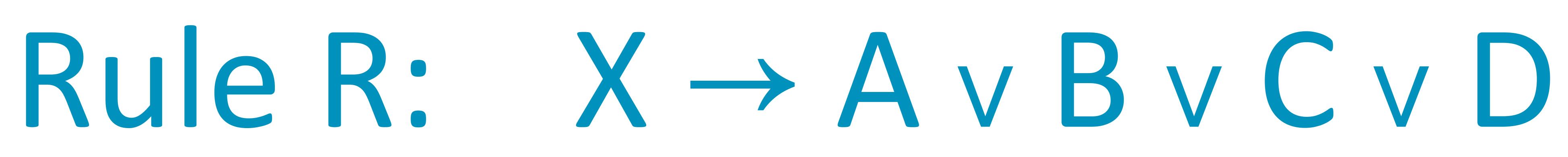

### $Fell(LockedUp) \rightarrow Called(TakeColdReset)$ V Called(TakeReset) V Rose(Halted) V Called(ExceptionEntry)

© 2017 Arm Limited

#### **Rule JRJC**

Exit from lockup is by any of the following:

- A Cold reset.

- A Warm reset.

- Entry to Debug state.

• Preemption by a higher priority processor exception.

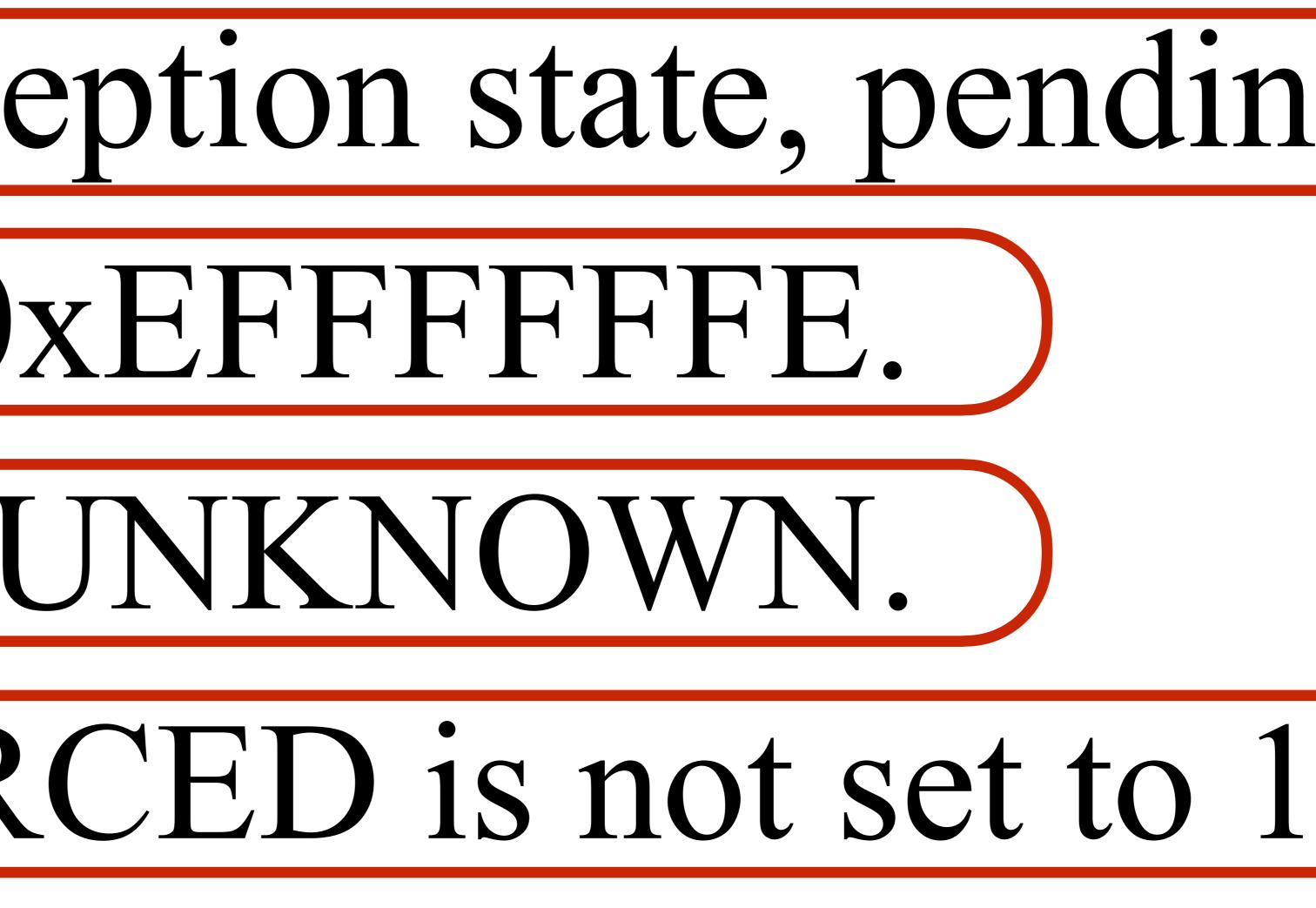

### Rule VGNW Entry to lockup from an exception causes • Any Fault Status Registers associated with the exception to be updated. Out of date • (No update to the exception state, pending or active.) Misleading •(The PC to be set to 0xEFFFFFE.) Untestable • (EPSR.IT to become UNKNOWN.) Ambiguous (In addition, HFSR.FORCED is not set to 1.)

### ~10,000 lines

## Convert

### ~1,000,000 lines

# Lessons Learned from validating specifications

# **Redundancy essential for detecting errors**

- Detected subtle bugs in security, exceptions, debug, ...

- Found bugs in English prose

# Need set of 'orthogonal' properties

- Invariants, Security properties, Reachability properties, etc.

# Eyeball closeness

# Needed to translate specification to another language to let us use other tools

# Making your specification public

# Public release of machine readable Arm specification

Machine readable Releases:

# v8.2 (4/2017) v8.3 (10/2017) v8.4 (6/2018) v8.5 (9/2018)

https://developer.arm.com/products/architecture/a-profile/exploration-tools https://github.com/alastairreid/mra\_tools https://github.com/herd/herdtools7/blob/master/herd/libdir/aarch64.cat

# Enable formal verification of software and tools

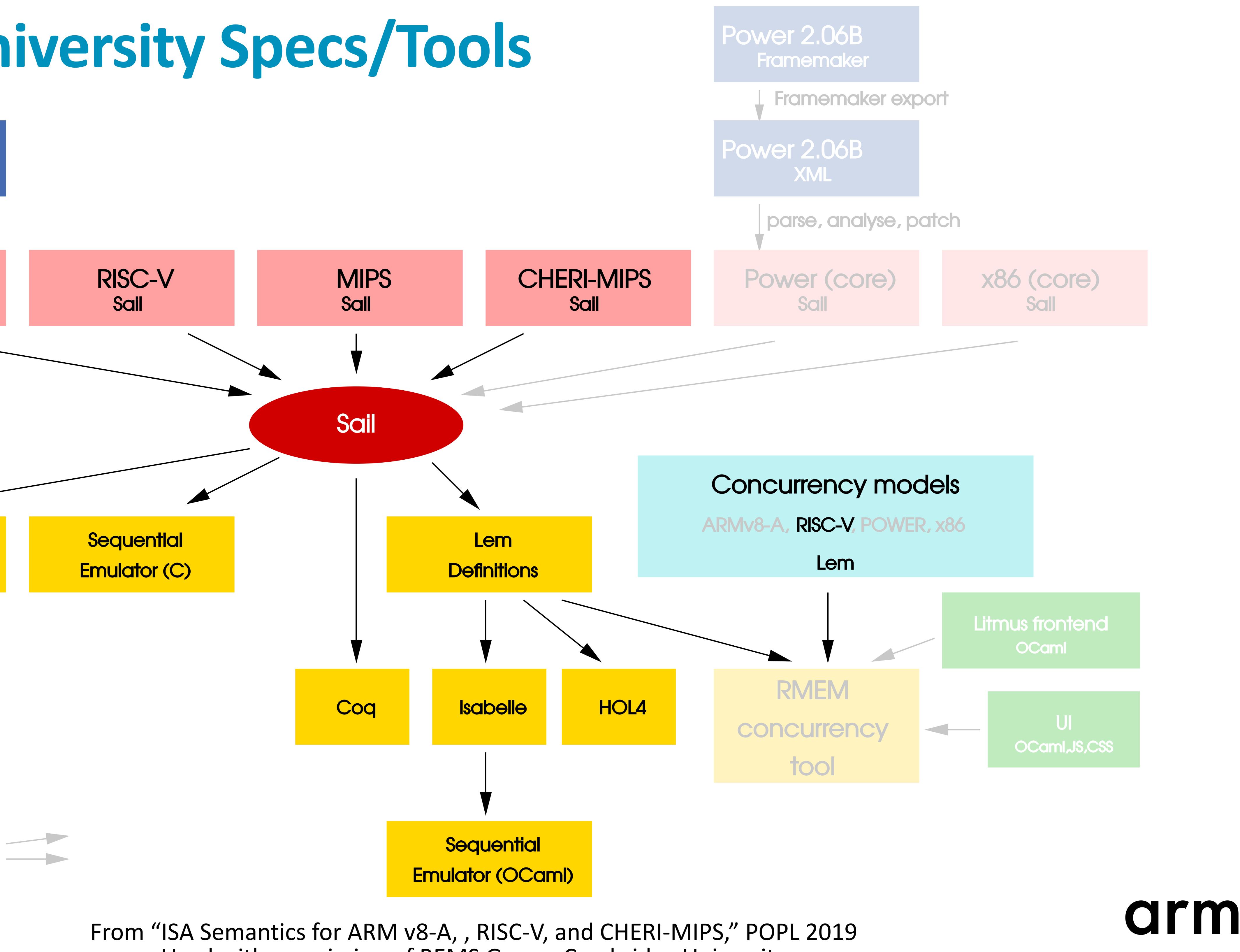

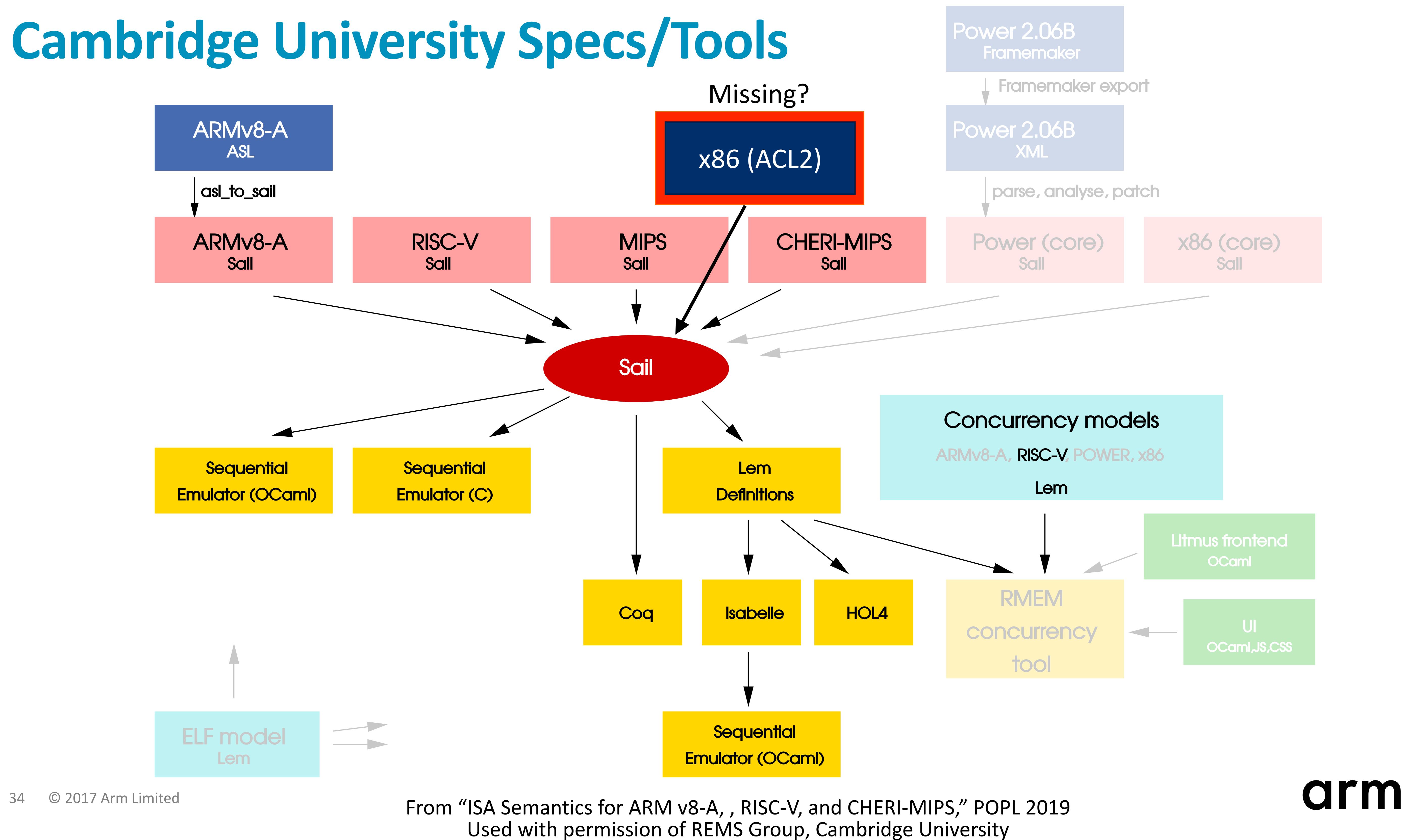

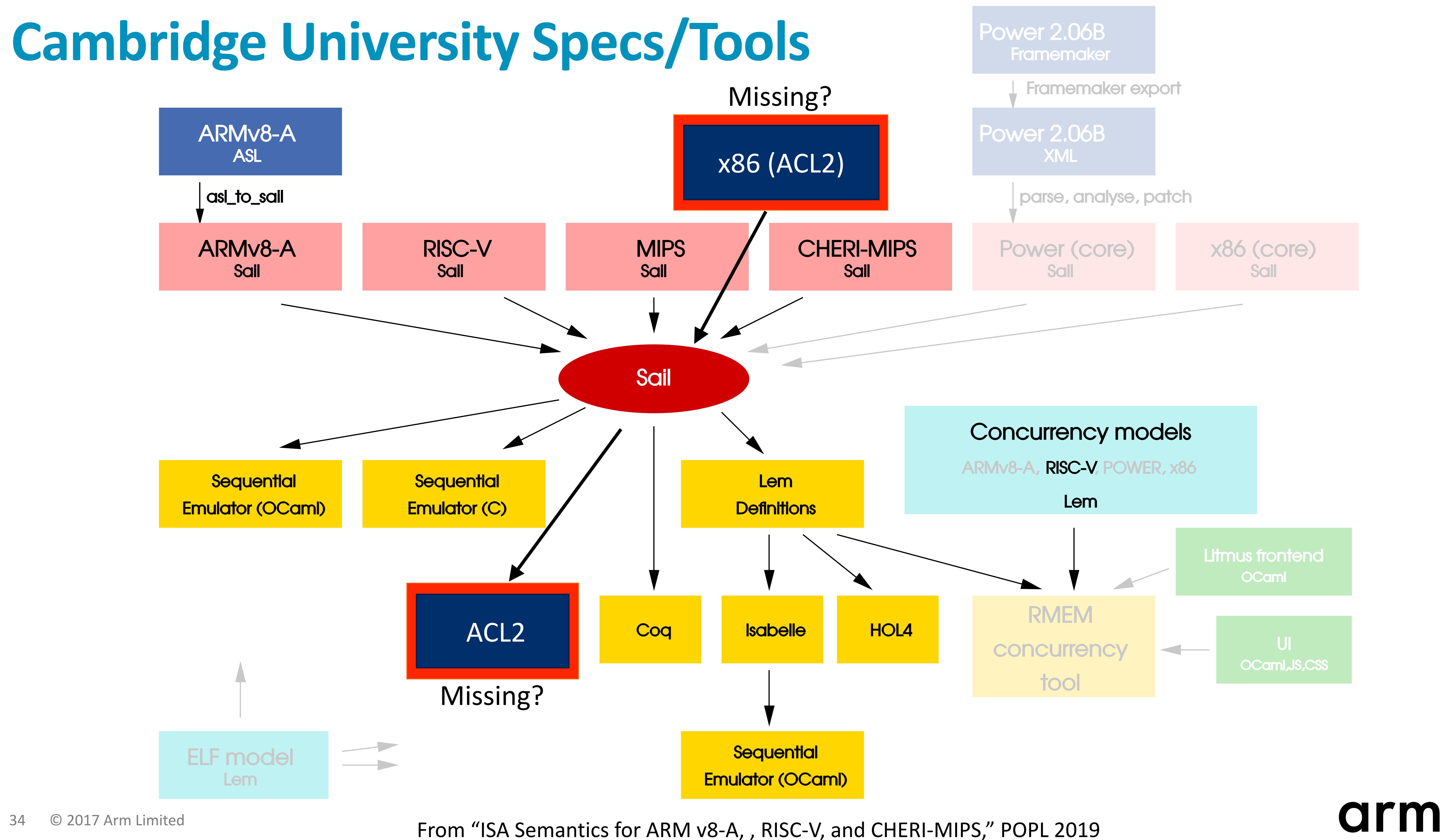

# **Cambridge University Specs/Tools**

ARMv8-A ASL

asl\_to\_sail

ARMv8-A Sall

Sequential **Emulator (OCaml)**

© 2017 Arm Limited 34

Used with permission of REMS Group, Cambridge University

ARMv8-A ASL

asl\_to\_sail

ARMv8-A Sall

Sequential **Emulator (OCaml)**

© 2017 Arm Limited 34

ARMv8-A ASL

asl\_to\_sail

ARMv8-A Sall

Sequential **Emulator (OCaml)**

© 2017 Arm Limited 34

Used with permission of REMS Group, Cambridge University

# Work in Progress: Security of Architecture Specifications

35 © 2017 Arm Limited

## Scope

# Challenges

- Compositional Attacks

# - Hardware-based Security Enforcement (HSE) Mechanisms - Confidentiality, Integrity, Availability

# - Cyclic dependencies between HSEs - Microarchitectural storage/timing channels

# The Specification Bottleneck: Modelling Real World Artifacts

# - Trustworthiness, Scope and Applicability - Significant Engineering Effort - Importance of sharing specifications across many users

Orm

# Thanks

Alasdair Armstrong (Cambridge U.) Alex Chadwick (ARM) Ali Zaidi (ARM) Anastasios Deligiannis (ARM) Anthony Fox (Cambridge U.) Ashan Pathirane (ARM) Belaji Venu (ARM) Bradley Smith (ARM) Brian Foley (ARM) Curtis Dunham (ARM) David Gilday (ARM) David Hoyes (ARM) David Seal (ARM) Daniel Bailey (ARM) Erin Shepherd (ARM) Francois Botman (ARM)

George Hawes (ARM) Graeme Barnes (ARM) Isobel Hooper (ARM) Jack Andrews (ARM) Jacob Eapen (ARM) Jon French (Cambridge U.) Kathy Gray (Cambridge U.) Krassy Gochev (ARM) Lewis Russell (ARM) Matthew Leach (ARM) Meenu Gupta (ARM) Michele Riga (ARM) Milosch Meriac (ARM) Nigel Stephens (ARM) Niyas Sait (ARM) Peng Wang (ARM)

Rick Chen (ARM) Will Keen (ARM) (and others)

```

Peter Sewell (Cambridge U.)

Peter Vrabel (ARM)

Richard Grisenthwaite (ARM)

Simon Bellew (ARM)

Thomas Grocutt (ARM)

Will Deacon (ARM)

Wojciech Meyer (ARM)

```

Thank You! Dankel Merci ありがとう! Gracias! Kitos

# @alastair d reid

"Trustworthy Specifications of the ARM v8-A and v8-M architecture," FMCAD 2016 "End to End Verification of ARM processors with ISA Formal," CAV 2016 "Who guards the guards? Formal Validation of ARM v8-M Specifications," OOPSLA 2017 "ISA Semantics for ARM v8-A, , RISC-V, and CHERI-MIPS," POPL 2019 https://alastairreid.github.io/papers/

#

# Is it better to create specs - Within ACL2? - In a DSL translated to ACL2?

© 2017 Arm Limited 40