Copyright

by

Hrishikesh Sathyavasu Murukkathampoondi

2004

The Dissertation Committee for Hrishikesh Sathyavasu Murukkathampoondi certifies that this is the approved version of the following dissertation:

# Design of Wide-Issue High-Frequency Processors in Wire Delay Dominated Technologies

| Committee:                    |

|-------------------------------|

| Douglas C. Burger, Supervisor |

| Craig M. Chase, Supervisor    |

| Lizy K. John                  |

| Norman P. Jouppi              |

| Stephen W. Keckler            |

| Yale N. Patt                  |

# Design of Wide-Issue High-Frequency Processors in Wire Delay Dominated Technologies

$\mathbf{b}\mathbf{y}$

Hrishikesh Sathyavasu Murukkathampoondi, B.E., M.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\bf August~2004}$

## Acknowledgments

Several people supported and encouraged me over the course of my time in graduate school and this work would not have been possible without their assistance. I would like to thank my advisor, Dr. Doug Burger, who played a prominent role in educating me and training me to be a good researcher. I am grateful to Dr. Craig Chase, my co-advisor, for his support and guidance. I have benefited greatly from my interactions with Dr. Stephen Keckler. I thank him for sharing his time and knowledge. Thanks to Dr. Lizy John for her support and advice during my first years in graduate school.

Raj Desikan wrote the original processor simulation tool that I used for my research. I would like to thank him for answering my numerous questions. I also thank Vikas Agarwal and Heather Hanson for their help in my understanding of technology related issues. My fellow research students at the Computer Architecture and Technology Laboratory have been important to my development. I gratefully acknowledge them for sharing their knowledge and friendship.

Kartik Agaram, Changkyu Kim, Ramadass Nagarajan, Karthikeyan Sankaralingam, Lakshminarasimhan Sethumadhavan, and Premkishore Shivakumar have been my house mates, travel companions, and close friends over the last five years. Graduate school would not have been so much fun without

the company of this interesting bunch.

Finally, I would like to thank my parents for providing me with the education that allowed me to reach this far. This work would not have been possible without their constant encouragement and unwavering support.

Design of Wide-Issue High-Frequency Processors in Wire Delay Dominated Technologies

Publication No.

Hrishikesh Sathyavasu Murukkathampoondi, Ph.D. The University of Texas at Austin, 2004

> Supervisors: Douglas C. Burger Craig M. Chase

Processor designers have increased performance by improving two parameters — clock frequency and the number of instructions processed per cycle (IPC). Increases in processor pipeline depth has been one factor that has contributed to clock frequency improvements. This research shows that improvements to clock frequency from increasing processor pipeline depths are reaching a point of diminishing returns. It may be possible to continue increasing pipeline depths at the cost of significant increases in design effort and complexity. However, such effort would better spent if directed at increasing IPC.

To increase IPC processors will have to issue more instructions every cycle. Also, the capacity and the number of ports of on-chip structures must

vii

be increased to support wider issue widths. However, large multi-ported structures will have long access latencies that will not scale with technology. Such structures cannot be clocked at aggressive frequencies. A natural solution to the problem of increasing circuit complexity is to partition the architecture into clusters. While clustering reduces the complexity of on-chip structures it introduces other bottlenecks and inefficiencies. These bottlenecks reduce the IPC of a clustered machine compared to an un-clustered machine. The goal of this research is to improve the IPC of a clustered processor to be closer to that of the un-clustered machine. For this purpose we propose new architectural techniques that mitigate the effect of the bottlenecks in clustered processors.

This research proposes a new mechanism, called consumer requested forwarding (CRF) that replaces transfer instructions with hardware signals. In the CRF method, consumer instructions that require values from remote clusters explicitly request the value to be forwarded. This technique significantly reduces the transfer instruction bottleneck. We also propose and evaluate three dynamic instruction steering mechanisms—memory instruction steering, critical operand steering and issue-balance steering. Our studies show that the memory instruction steering policy provides significant IPC improvements over the baseline mechanisms that we evaluated.

# **Table of Contents**

| Ackno   | vledgments                                               | $\mathbf{v}$ |

|---------|----------------------------------------------------------|--------------|

| Abstra  | ${f ct}$                                                 | vii          |

| List of | Tables                                                   | xii          |

| List of | Figures                                                  | xviii        |

| Chapt   | er 1. Introduction                                       | 1            |

| 1.1     | Pipeline Scaling Trends                                  | 2            |

| 1.2     | Process Technology Trends                                | 4            |

|         | 1.2.1 Wire Delay Scaling                                 | 5            |

|         | 1.2.2 Implications For Processor Design                  | 6            |

| 1.3     | Clustered Processors                                     | 8            |

| 1.4     | Thesis Statement                                         | 9            |

| 1.5     | Dissertation Contributions                               | 9            |

| 1.6     | Organization                                             | 11           |

| Chapt   | er 2. Processor Pipeline Scaling                         | 13           |

| 2.1     | Estimating Overhead                                      | 14           |

| 2.2     | Pipeline Scaling Methodology                             | 18           |

| 2.3     | Optimal Pipeline Depth                                   | 20           |

|         | 2.3.1 Sensitivity of $\phi_{logic}$ to $\phi_{overhead}$ | 26           |

|         | 2.3.2 Related Work                                       | 27           |

| 2.4     | Effect of Pipelining on IPC                              | 28           |

| 2.5     | A Segmented Instruction Window Design                    | 31           |

|         | 2.5.1 Pipelining Instruction Wakeup                      | 32           |

|         | 2.5.2 Pipelining Instruction Select                      | 35           |

|         | 2.5.3 Related Work                                       | 38           |

| 2.6     | Summary                                                  | 40           |

| Chapte     | er 3.  | Wide Issue Processors                        | 43  |

|------------|--------|----------------------------------------------|-----|

| 3.1        | Instru | action Level Parallelism in Programs         | 44  |

|            | 3.1.1  | Experimental Methodology                     | 44  |

|            | 3.1.2  | Results                                      | 48  |

| 3.2        | Partit | cioned Architectures                         | 50  |

|            | 3.2.1  | Very Long Instruction Word Processors        | 50  |

|            | 3.2.2  | Multithreaded Architectures                  | 51  |

|            | 3.2.3  | Other Partitioned Architectures              | 51  |

|            | 3.2.4  | Clustered Superscalar Processors             | 52  |

|            | 3.2.5  | Discussion                                   | 55  |

| 3.3        | Baseli | ine Clustered Architecture                   | 56  |

| 3.4        | Sumn   | nary                                         | 61  |

| Chapter 4. |        | Bottlenecks in Clustered Architectures       | 63  |

| 4.1        | Quan   | tifying the Effect of Bottlenecks            | 63  |

| 4.2        | Quan   | tifying the Effect of Individual Bottlenecks | 69  |

|            | 4.2.1  | Transfer Instructions                        | 69  |

|            | 4.2.2  | Inter-cluster Communication Delay            | 74  |

|            | 4.2.3  | Cluster Resource Limitations                 | 81  |

| 4.3        | Sumn   | nary                                         | 87  |

| Chapte     | er 5.  | Reducing Transfer Instructions               | 91  |

| 5.1        | Regis  | ter Caching                                  | 91  |

| 5.2        | Inter- | cluster Operand Forwarding                   | 97  |

|            | 5.2.1  | Consumer-requested Forwarding                | 98  |

|            |        | 5.2.1.1 Dual-wakeup                          | 104 |

|            |        | 5.2.1.2 Pro-active Operand Fetch             | 108 |

|            | 5.2.2  | Hot-register Based Forwarding                | 110 |

| 5.3        | Relate | ed Work                                      | 116 |

| 5.4        | Sumn   | nary                                         | 119 |

| Chapte  | er 6. Instruction Steering                                     | 122 |

|---------|----------------------------------------------------------------|-----|

| 6.1     | Memory Instruction Steering                                    | 123 |

|         | 6.1.1 Ideal Memory Instruction Steering                        | 126 |

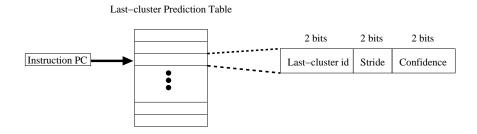

|         | 6.1.2 Memory Instruction Steering with Last-cluster Prediction | 130 |

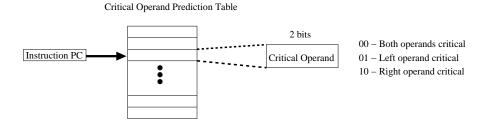

| 6.2     | Critical Operand Steering                                      | 137 |

| 6.3     | Issue-width Balance Steering                                   | 141 |

| 6.4     | Related Work                                                   | 144 |

| 6.5     | Summary                                                        | 149 |

| Chapte  | er 7. Conclusions                                              | 151 |

| 7.1     | Dissertation Summary                                           | 153 |

| 7.2     | Discussion                                                     | 156 |

| Appen   | dices                                                          | 159 |

| Appen   | dix A. Pipeline Scaling Simulation Results                     | 160 |

| Appen   | dix B. Clustered Processor Simulation Results                  | 162 |

| B.1     | The Baseline Clustered Processor                               | 162 |

| B.2     | Register Caching                                               | 178 |

| B.3     | Consumer-requested Forwarding                                  | 180 |

| B.4     | Hot-register Based Forwarding                                  | 188 |

| B.5     | Memory Instruction Steering                                    | 190 |

| B.6     | Critical Operand Steering                                      | 193 |

| B.7     | Issue-width Balance Steering                                   | 194 |

| Bibliog | graphy                                                         | 196 |

| Index   | 2                                                              | 210 |

| Vita    | 2                                                              | 212 |

## List of Tables

| 2.1 | Overheads due to latch, clock skew and jitter                                                                                                                                                                                                                                                          | 18 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | SPEC 2000 benchmarks used in all simulation experiments                                                                                                                                                                                                                                                | 19 |

| 2.3 | Access latencies (clock cycles) of microarchitectural structures at 100nm technology (drawn gate length). The last row shows the latency of on-chip structures on the Alpha 21264 processor (180nm)                                                                                                    | 21 |

| 2.4 | Execution latencies (clock cycles) of integer and floating-point operations at 100nm technology (drawn gate length). The functional units are fully pipelined and new instructions can be assigned to them every cycle. The last row shows the execution latency on the Alpha 21264 processor (180nm). | 22 |

| 3.1 | The number of dynamic instructions (in billions) skipped for the SPEC 2000 benchmarks before simulating 100 million instructions.                                                                                                                                                                      | 45 |

| 4.1 | Average reduction in the IPC of clustered processors compared to monolithic processors with equivalent resources. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation.                                        | 67 |

| 4.2 | Transfer instructions as a fraction of the total number of instructions executed by the baseline clustered processor                                                                                                                                                                                   | 72 |

| 4.3 | Average improvement in the IPC of clustered processors when<br>the transfer instruction overhead is removed. Both the clustered<br>processor and the monolithic machine configurations simulated<br>perfect branch prediction and perfect memory disambiguation.                                       | 74 |

| 4.4 | Remote operand accesses as a fraction of the total number of operands read during execution by the baseline clustered processor.                                                                                                                                                                       | 78 |

| 4.5 | Average improvement in the IPC of clustered processors when inter-cluster communication latency is removed. For these experiments, all configurations simulated perfect branch prediction and perfect memory disambiguation                                                                            | 80 |

| 4.6  | Workload imbalance in a 16-wide, 4-cluster machine using dependence steering                                                                                                                                                                             | 83  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.7  | The number of issue-limited instructions (ILI) and structure capacity stalls (SCS) per 100 instructions. These statistics were collected for configurations with Alpha 21264-like branch prediction and memory dependence prediction                     | 84  |

| 4.8  | Average improvement in the IPC of clustered processors when cluster resource limitations are removed. For these experiments, all configurations simulated perfect branch prediction and perfect memory disambiguation                                    | 86  |

| 4.9  | Average improvement in the IPC of a 16-wide 4-cluster processor when clustering bottlenecks are removed. Both the clustered processor and the monolithic machine configurations used Alpha 21264-like branch prediction and memory dependence prediction | 88  |

| 4.10 | Average improvement in the IPC of a 16-wide 4-cluster processor when clustering bottlenecks are removed. For these experiments, all configurations simulated perfect branch prediction and perfect memory disambiguation.                                | 89  |

| 5.1  | The number of source operands that are re-used as a fraction of the total number of source operands                                                                                                                                                      | 93  |

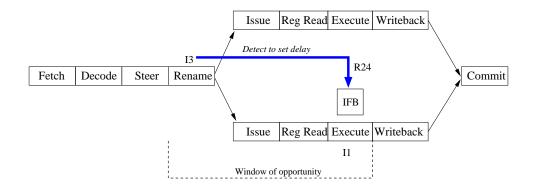

| 5.2  | Average improvement the IPC of clustered processor with IFB tables compared to a baseline machine for increasing values of detect-to-set delay. All configurations were simulated with perfect branch prediction.                                        | 106 |

| 5.3  | Average improvement the IPC of clustered processor with IFB tables compared to a baseline machine for increasing values of detect-to-set delay. All configurations were simulated with perfect branch prediction.                                        | 110 |

| 6.1  | Remote cache accesses as a fraction of the total number of memory instructions executed by the baseline clustered processor.                                                                                                                             | 125 |

| 6.2  | Workload imbalance in a 16-wide, 4-cluster machine using memory steering overlayed on dependence steering.                                                                                                                                               | 129 |

| 6.3  | Remote cache accesses as a fraction of the total number of memory instructions executed by the baseline clustered processor using memory steering (Mem) and with the baseline steering policies (Base)                                                   | 133 |

| A.1  | The IPCs of SPEC 2000 benchmarks at pipeline depths corresponding to $\phi_{logic}$ between 2 and 8 FO4                                                                                                                                                  | 160 |

| A.2  | The IPCs of SPEC 2000 benchmarks at pipeline depths corresponding to $\phi_{logic}$ between 9 and 16 FO4                                                                                                        | 161 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B.1  | The IPCs of a monolithic and a 16-wide 4-cluster processor. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                                         | 162 |

| B.2  | The IPCs of a monolithic and a 16-wide 4-cluster processor. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction                                                  | 163 |

| B.3  | The IPCs of a monolithic and a 8-wide 4-cluster processor. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                                          | 164 |

| B.4  | The IPCs of a monolithic and a 32-wide 4-cluster processor. These configurations simulated perfect branch prediction and perfect memory disambiguation                                                          | 165 |

| B.5  | The IPC of an 16-wide 4-cluster processor with no transfer instructions. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                            | 166 |

| B.6  | The IPC of an 16-wide 4-cluster processor with no transfer instructions. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction                                     | 167 |

| B.7  | The IPC of an 8-wide 4-cluster processor with no transfer instructions. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                             | 168 |

| B.8  | The IPC of an 32-wide 4-cluster processor with no transfer instructions. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                            | 169 |

| B.9  | The IPC of an 16-wide 4-cluster processor without the inter-<br>cluster communication bottleneck. These configurations sim-<br>ulated perfect branch prediction and perfect memory disam-<br>biguation.         | 170 |

| B.10 | The IPC of an 16-wide 4-cluster processor without the inter-<br>cluster communication bottleneck. These configurations simu-<br>lated Alpha 21264-like branch prediction and memory depen-<br>dence prediction. | 171 |

| B.11 | The IPC of an 8-wide 4-cluster processor without the intercluster communication bottleneck. These configurations simulated perfect branch prediction and perfect memory disambiguation.                         | 172 |

| B.12 | The IPC of an 32-wide 4-cluster processor without the inter-<br>cluster communication bottleneck. These configurations sim-<br>ulated perfect branch prediction and perfect memory disam-<br>biguation.                                                                                                       | 173 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B.13 | The IPC of an 16-wide 4-cluster processor without the cluster resource limitation bottleneck. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                                                                                                     | 174 |

| B.14 | The IPC of an 16-wide 4-cluster processor without the cluster resource limitation bottleneck. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction.                                                                                                             | 175 |

| B.15 | The IPC of an 8-wide 4-cluster processor without the cluster resource limitation bottleneck. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                                                                                                      | 176 |

| B.16 | The IPC of an 32-wide 4-cluster processor without the cluster resource limitation bottleneck. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                                                                                                     | 177 |

| B.17 | The IPC of an 16-wide 4-cluster processor with register caching. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                                                                                                                                  | 178 |

| B.18 | The IPC of an 16-wide 4-cluster processor with register caching. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction.                                                                                                                                          | 179 |

| B.19 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding for different detect-to-set latencies. These simulations used the dual-wakeup policy to avoid deadlocks and used mod3 steering. These configurations simulated perfect branch prediction and perfect memory disambiguation       | 180 |

| B.20 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding for different detect-to-set latencies. These simulations used the dual-wakeup policy to avoid deadlocks and used load-slice steering. These configurations simulated perfect branch prediction and perfect memory disambiguation | 181 |

| B.21 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding for different detect-to-set latencies. These simulations used the dual-wakeup policy to avoid deadlocks and used dependence steering. These configurations simulated perfect branch prediction and perfect memory disambiguation | 182 |

| B.22 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding. These simulations used the dual-wakeup policy to avoid deadlocks and assumed a 1-cycle detect-to-set latency. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction                | 183 |

| B.23 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding for different detect-to-set latencies. These simulations used the pro-active operand fetch policy to avoid deadlocks and used mod3 steering. These configurations simulated perfect branch prediction and perfect memory disambiguation        | 184 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B.24 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding for different detect-to-set latencies. These simulations used the pro-active operand fetch policy to avoid deadlocks and used load-slice steering. These configurations simulated perfect branch prediction and perfect memory disambiguation. | 185 |

| B.25 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding for different detect-to-set latencies. These simulations used the pro-active operand fetch policy to avoid deadlocks and used dependence steering. These configurations simulated perfect branch prediction and perfect memory disambiguation. | 186 |

| B.26 | The IPC of an 16-wide 4-cluster processor with consumer requested forwarding. These simulations used pro-active operand fetch to avoid deadlocks and assumed a 1-cycle detect-to-set latency. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction                            | 187 |

| B.27 | The IPC of an 16-wide 4-cluster processor with hot-register based forwarding. These simulations used pro-active operand fetch to avoid deadlocks. These configurations simulated perfect branch prediction and perfect memory disambiguation.                                                                               | 188 |

| B.28 | The IPC of an 16-wide 4-cluster processor with hot-register based forwarding. These simulations used pro-active operand fetch to avoid deadlocks. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction.                                                                       | 189 |

| B.29 | The IPC of an 16-wide 4-cluster processor with <i>ideal</i> memory-steering. These configurations simulated perfect branch prediction and perfect memory disambiguation. Also, the configurations in these experiments used the CRF method to remove transfer instructions.                                                 | 190 |

| B.30 | The IPC of an 16-wide 4-cluster processor with memory-steering using the last-cluster prediction method. These configurations simulated perfect branch prediction and perfect memory disambiguation. Also, the configurations in these experiments used the CRF method to remove transfer instructions.                     | 191 |

| B.31 | The IPC of an 16-wide 4-cluster processor with memory-steering using the last-cluster prediction method. These configurations simulated Alpha 21264-like branch prediction and memory dependence prediction. Also, the configurations in these experiments used the CRF method to remove transfer instructions. | 192 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B.32 | The IPC of an 16-wide 4-cluster processor with critical-operand steering. These configurations used Alpha 21264-like branch prediction and memory dependence prediction. Also, the configurations in these experiments used the CRF method to remove transfer instructions.                                     | 193 |

| B.33 | The IPC of an 16-wide 4-cluster processor with issue-balance steering. These configurations simulated perfect branch prediction and perfect memory disambiguation. Also, the configurations in these experiments used the CRF method to remove transfer instructions.                                           | 194 |

| B.34 | The IPC of an 16-wide 4-cluster processor with issue-balance steering. These configurations used Alpha 21264-like branch prediction and memory dependence prediction. Also, the configurations in these experiments used the CRF method to remove transfer instructions.                                        | 195 |

# List of Figures

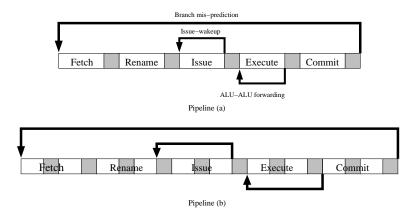

| 1.1  | A simple processor pipeline with critical loops                                                                                                                                                                                                                                                                                                           | 3  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

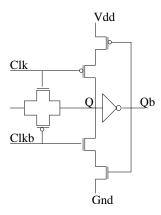

| 2.1  | Circuit diagram of a basic pulse latch.                                                                                                                                                                                                                                                                                                                   | 15 |

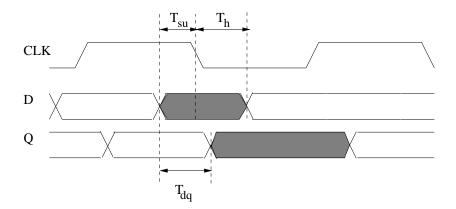

| 2.2  | Timing diagram of a basic pulse latch. The shaded area indicates that the signal is valid                                                                                                                                                                                                                                                                 | 16 |

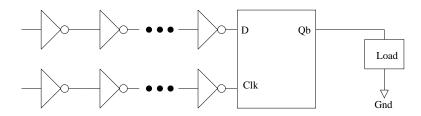

| 2.3  | Simulation setup to find latch overhead. The clock and data signals are buffered by a series of six inverters and the output drives a similar latch with its transmission gate turned on                                                                                                                                                                  | 16 |

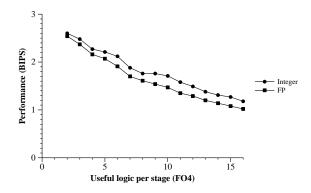

| 2.4  | The harmonic mean of the performance of integer and floating point benchmarks without latch overhead, clock skew and jitter.                                                                                                                                                                                                                              | 23 |

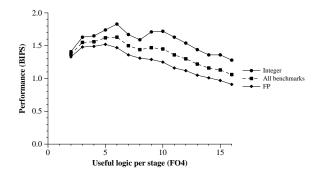

| 2.5  | The harmonic mean of the performance of integer and floating point benchmarks, executing on an out-of-order pipeline, accounting for latch overhead, clock skew and jitter. For integer benchmarks best performance is obtained with 6 FO4 of useful logic per stage $(\phi_{logic})$ . For floating-point benchmarks the optimal $\phi_{logic}$ is 5 FO4 | 24 |

| 2.6  | The harmonic mean of the performance of integer benchmarks, executing on an out-of-order pipeline for various values of $\phi_{overhead}$ .                                                                                                                                                                                                               | 26 |

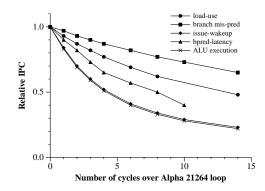

| 2.7  | IPC sensitivity to critical loops in the data path. The x-axis of this graph shows the number of cycles the loop was extended over its length in the Alpha 21264 pipeline. The y-axis shows relative IPC.                                                                                                                                                 | 29 |

| 2.8  | A high-level representation of the instruction window                                                                                                                                                                                                                                                                                                     | 31 |

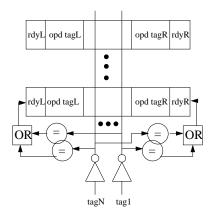

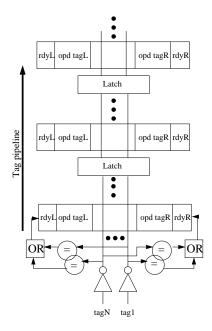

| 2.9  | A segmented instruction window wherein the tags are broadcast to one stage of the instruction window at a time. We also assume that instructions can be selected from the entire window.                                                                                                                                                                  | 33 |

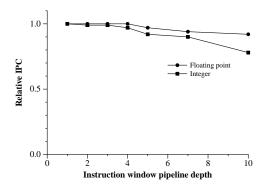

| 2.10 | IPC sensitivity to instruction window pipeline depth, assuming all entries in the window can be considered for selection                                                                                                                                                                                                                                  | 35 |

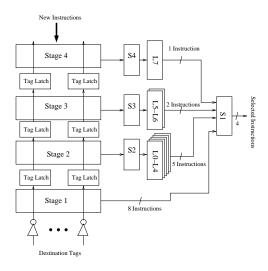

| 2.11 | A 32-entry instruction window partitioned into four stages with a selection logic fan-in of 16 instructions                                                                                                                                                                                                                                               | 37 |

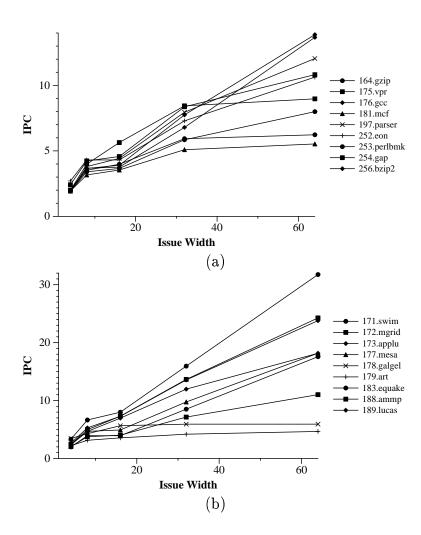

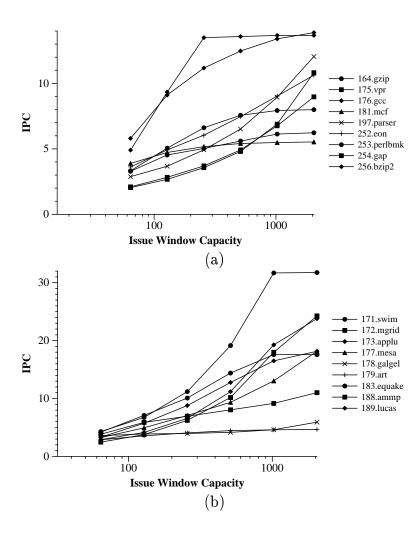

| 3.1  | The IPC of SPEC 2000 benchmarks at different issue widths for a processor with a 2048 entry issue window                                                                                                                                                                                                                                                  | 46 |

| 3.2 | The IPC of SPEC benchmarks at different issue window capacities for a 64-wide processor                                                                                                                                                                                                                                      | 47 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.3 | Pipeline diagram of the baseline processor                                                                                                                                                                                                                                                                                   | 57 |

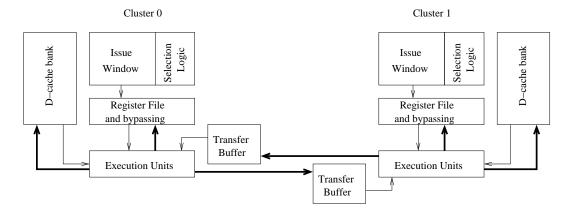

| 3.4 | The issue, register read and execute stages of a clustered super-scalar processor                                                                                                                                                                                                                                            | 60 |

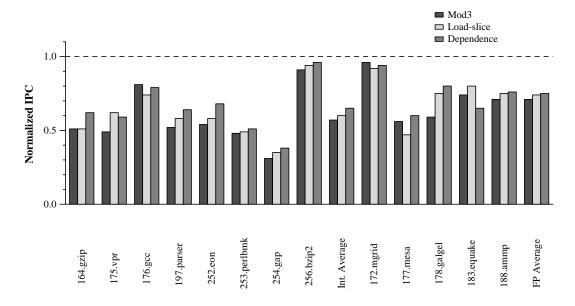

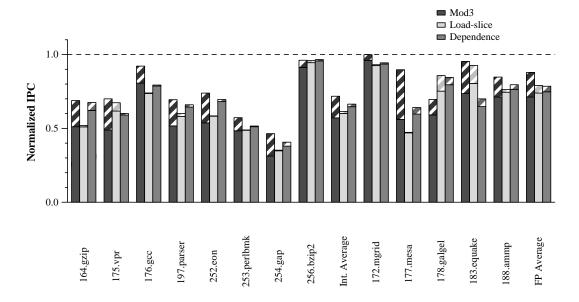

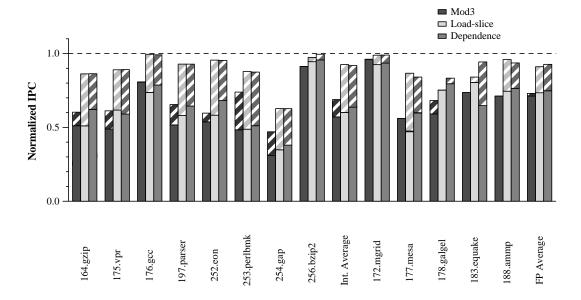

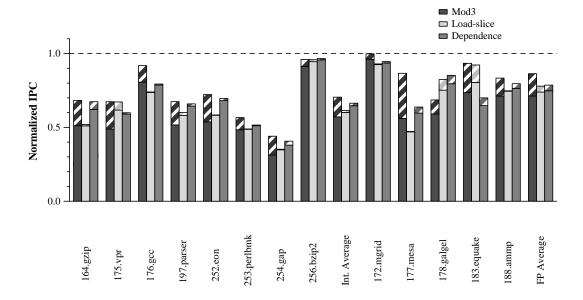

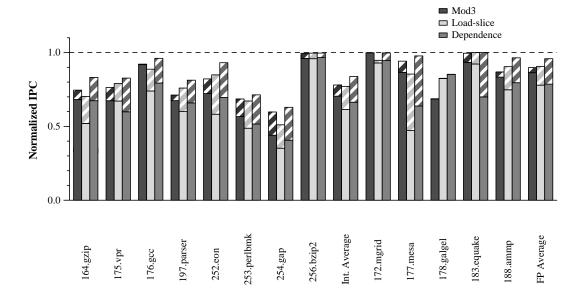

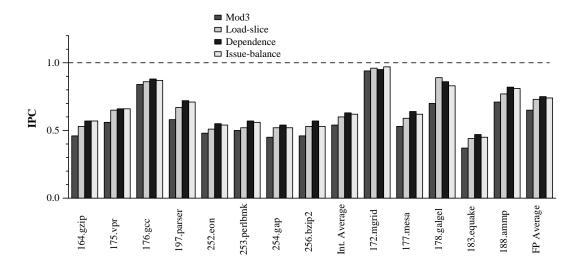

| 4.1 | The IPC of a 16-wide 4-cluster processor normalized by the IPC of a monolithic processor. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation                                                                                       | 65 |

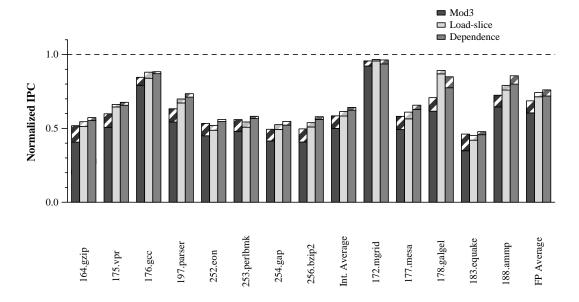

| 4.2 | The IPC of a 16-wide clustered processor configuration, with and without the transfer instruction bottleneck, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation.           | 71 |

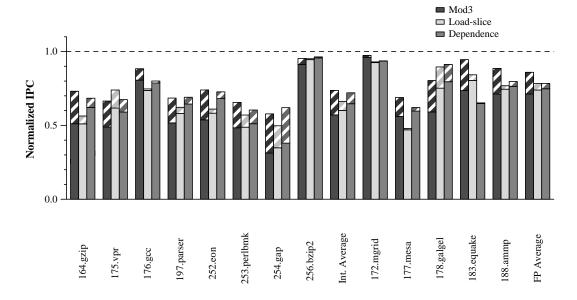

| 4.3 | The IPC of a 16-wide clustered processor configuration, with and without the transfer instruction bottleneck, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations used Alpha 21264-like branch prediction and memory dependence prediction         | 73 |

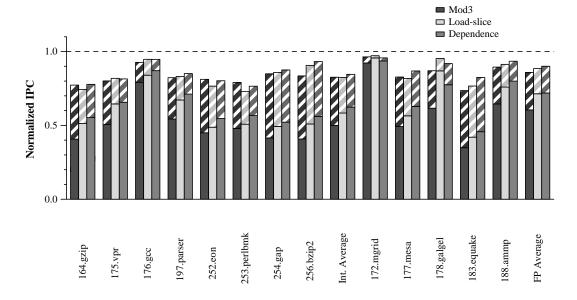

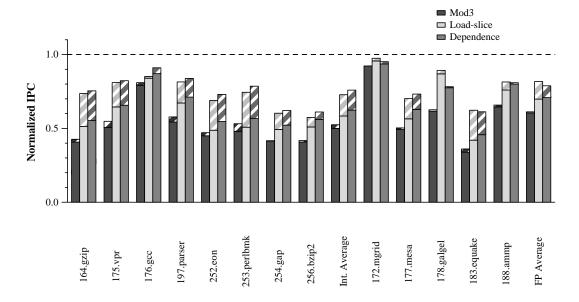

| 4.4 | The IPC of a 16-wide clustered processor configuration, with and without the inter-cluster communication bottleneck, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation.    | 77 |

| 4.5 | The IPC of a 16-wide clustered processor configuration, with and without the inter-cluster communication bottleneck, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations used Alpha 21264-like branch prediction and memory dependence prediction. | 79 |

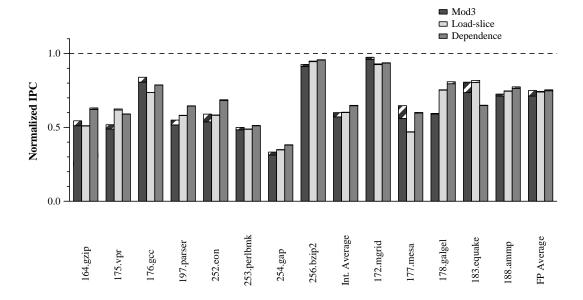

| 4.6 | The IPC of a 16-wide clustered processor configuration, with and without the cluster resource limitation bottleneck, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation.    | 82 |

| 4.7 | The IPC of a 16-wide clustered processor configuration, with and without the cluster resource limitation bottleneck, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations used Alpha 21264-like branch prediction and memory dependence prediction.                                                               | 85  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Example of a stream of instructions with an inter-cluster dependence. Instructions 1 and 2 are assigned to cluster 0 while instructions 3 and 4 are assigned to cluster 1                                                                                                                                                                                                                  | 92  |

| 5.2 | The IPC of a 16-wide 4-cluster processor, with and without register caching, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation.                                                                                                          | 94  |

| 5.3 | The IPC of a 16-wide 4-cluster processor, with and without register caching, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated Alpha 21264-like branch prediction and memory dependence prediction                                                                                                   | 96  |

| 5.4 | Example of a stream of instructions with inter-cluster dependence. Instructions I1 and I2 are assigned to cluster 0. Instruction I3 is assigned to cluster 1 and I4 to cluster 2                                                                                                                                                                                                           | 97  |

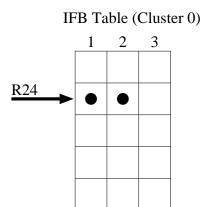

| 5.5 | The inter-cluster forwarding bit table                                                                                                                                                                                                                                                                                                                                                     | 98  |

| 5.6 | Clustered processor pipeline with inter-cluster forwarding bits.                                                                                                                                                                                                                                                                                                                           | 99  |

| 5.7 | Pipeline timing for a clustered processor with consumer requested forwarding                                                                                                                                                                                                                                                                                                               | 101 |

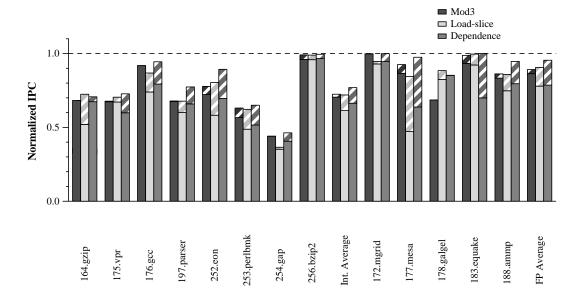

| 5.8 | The IPC of a 16-wide clustered processor configuration, with and without the IFB mechanism, normalized by the IPC of the ideal monolithic machine. The configurations with the IFB mechanism used the dual-wakeup policy to avoid deadlocks. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation. | 104 |

| 5.9 | The IPC of a 16-wide clustered processor configuration, with and without the IFB mechanism, normalized by the IPC of the ideal monolithic machine. The configurations with the IFB mechanism used the dual-wakeup policy to avoid deadlocks. Both the clustered processor and the monolithic machine configurations used Alpha 21264-like branch prediction and memory                     | 105 |

|     | dependence prediction                                                                                                                                                                                                                                                                                                                                                                      | 107 |

| 5.10 | The IPC of a 16-wide clustered processor configuration, with and without the IFB mechanism, normalized by the IPC of the ideal monolithic machine. The configurations with the IFB mechanism used the pro-active operand fetch policy to avoid deadlocks. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation            | 109 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

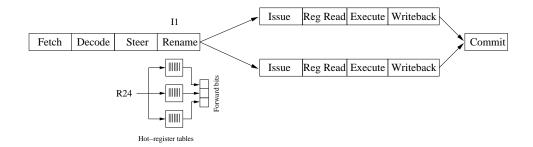

| 5.11 | Clustered processor pipeline with hot-register based forwarding.                                                                                                                                                                                                                                                                                                                                                  | 112 |

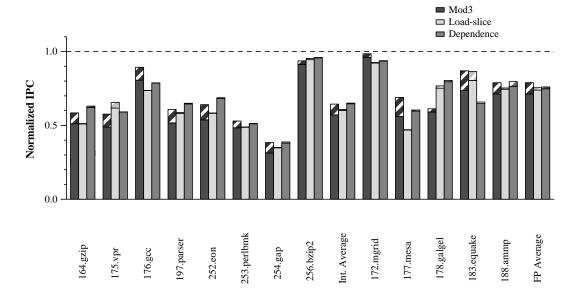

| 5.12 | The IPC of a 16-wide clustered processor configuration, with and without the hot-register mechanism, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation                                                                                                          | 113 |

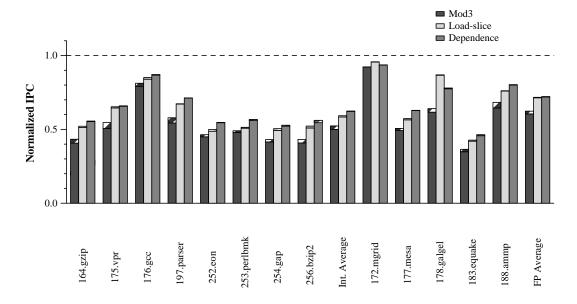

| 5.13 | The IPC of a 16-wide clustered processor configuration, with and without the hot-register mechanism, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations used Alpha 21264-like branch prediction and memory dependence prediction                                                                                                       | 115 |

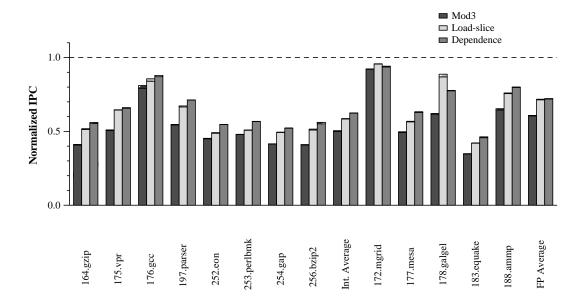

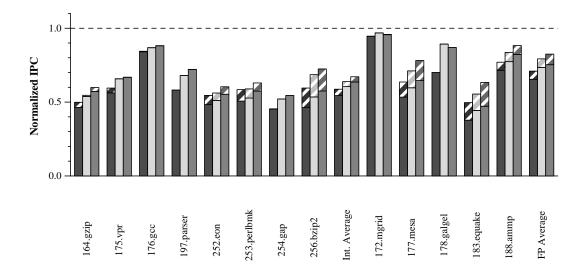

| 6.1  | The IPC of a 16-wide clustered processor configuration, with and without <i>ideal</i> memory steering, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation. Also, the configurations in these experiments used the CRF method to remove transfer instructions.    | 126 |

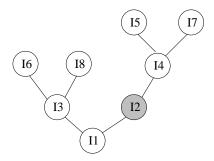

| 6.2  | An example data dependence graph. The nodes represent instructions and the edges represent dependence. The shaded node represents a memory instruction.                                                                                                                                                                                                                                                           | 128 |

| 6.3  | The IPC of a 16-wide clustered processor configuration, with and without last-cluster memory steering, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations simulated perfect branch prediction and perfect memory disambiguation. Also, the configurations in these experiments used the CRF method to remove transfer instructions.    | 131 |

| 6.4  | The IPC of a 16-wide clustered processor configuration, with and without last-cluster memory steering, normalized by the IPC of the ideal monolithic machine. Both the clustered processor and the monolithic machine configurations used Alpha 21264-like branch prediction and memory dependence prediction. Also, the configurations in these experiments used the CRF method to remove transfer instructions. | 134 |

| 6.5 | Memory instruction steering with a cluster-stride predictor                                                                                                                                                                                                               | 136 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.6 | Critical-operand prediction table                                                                                                                                                                                                                                         | 138 |

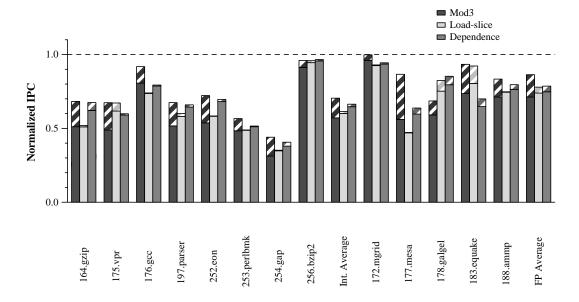

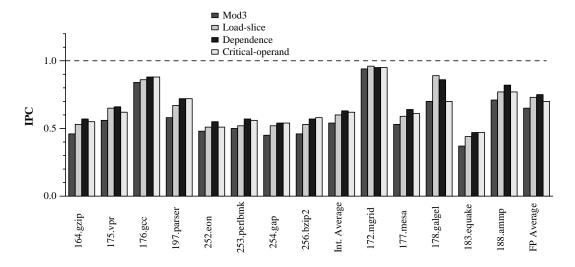

| 6.7 | The IPC of a 16-wide 4-cluster processor using critical-operand steering. All configurations used Alpha 21264-like branch prediction and memory dependence prediction. Also, the configurations in these experiments used the CRF method to remove transfer instructions. | 140 |

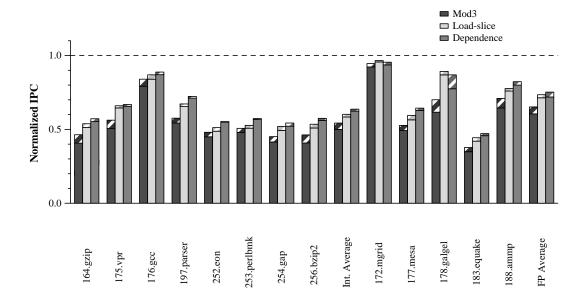

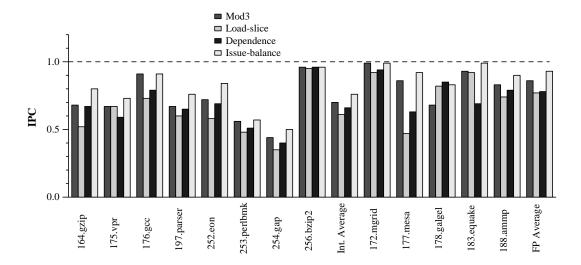

| 6.8 | The IPC of a 16-wide 4-cluster processor using issue-balance steering. All configurations simulated perfect branch prediction and memory disambiguation. Also, the configurations in these experiments used the CRF method to remove transfer instructions                | 142 |

| 6.9 | The IPC of a 16-wide 4-cluster processor using issue-balance steering. All configurations used Alpha 21264-like branch prediction and memory dependence prediction. Also, the configurations in these experiments used the CRF method to remove transfer instructions.    | 143 |

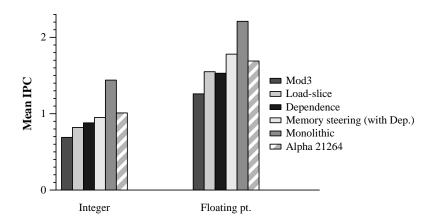

| 7.1 | The IPCs of a 16-wide clustered processor, a 16-wide monolithic processor, and an Alpha 21264-like configuration. All these simulations used a tournament style predictor like in the Alpha-21264.                                                                        | 156 |

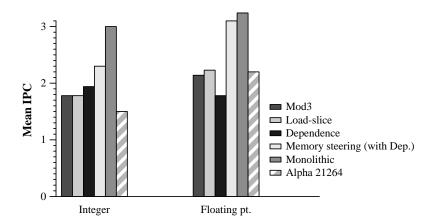

| 7.2 | The IPCs of a 16-wide clustered processor, a 16-wide monolithic processor, and an Alpha 21264-like configuration. All these simulations used a perfect branch prediction                                                                                                  | 158 |

## Chapter 1

## Introduction

Designers have improved microprocessor performance by increasing the number of instructions that are concurrently executed and by increasing clock frequency. Several novel architectural ideas have been developed to improve the instructions per cycle (IPC) that can be processed by the computer. These include branch prediction, data caching, out-of-order issue and execution etc. Improvements in clock frequency have been achieved by developing better semiconductor process technology, faster logic circuits, and aggressively pipelining the architecture. For example, over the past twelve years process technology has been scaled from 1000nm to 130nm. Similarly processor pipeline depths have been increased from 5 stage to 30 stages.

However, recent studies indicate that it will become increasingly difficult to improve processor performance in the future. Both components of performance improvement—clock frequency and IPC—face emerging technology-driven challenges. Recent studies on processor pipeline scaling show that clock frequency improvements from increasing pipeline depths are reaching a point of diminishing return. In the future, designers will have to rely on IPC to a greater extent than before to improve performance.

In order to sustain greater IPC, processors will have to issue more instructions every cycle. Also, microarchitectural structures, such as register files and issue windows, must increase in capacity to be able to uncover greater parallelism in the program. But, technology scaling projections indicate that the latency of large structures with multiple ports will not scale as well as transistor switching speeds. This poor scaling of processor structure latencies will adversely affect IPC. In this dissertation we highlight the challenges facing processor design and propose architectural solutions to address them.

### 1.1 Pipeline Scaling Trends

Increasing processor pipeline depth is one technique that designers use to improve clock frequency and processor performance. Processor pipelines have grown from a single stage (Intel 8086) to 30 stages (Intel Pentium IV). While increasing pipeline depth does increase clock frequency it reduces the IPC that the processor can sustain.

For example, consider the simple pipeline shown in Figure 1.1. The grey boxes in the diagram represent pipelining overhead while the clear boxes represent useful work. The operating frequency of this pipeline can be increased by decreasing the amount of useful work done every stage and increasing pipeline depth. As illustrated in Figure 1.1, by halving the amount of useful logic per stage we can double the depth of this pipeline (pipeline (b)). Note that, because of latch overhead, doubling the pipeline depth does not double clock frequency. In fact, the new pipeline has added additional latches and increased

Figure 1.1: A simple processor pipeline with critical loops.

the end to end latency of the pipeline.

If there were no data or control dependences in the instruction stream both these pipelines can commit one instruction every cycle. However, control and data dependences in the instruction stream expose critical loops in the pipeline that reduce overall IPC. Figure 1.1 illustrates some of the critical loops in the pipeline. These loops include: issue-wakeup loop, ALU to ALU forwarding, data-cache access and the branch mis-prediction loop. Increasing pipeline depth increases the latency of critical loops due to the additional clocking overhead that is added to the loop. For example, in pipeline (a), when a branch instruction is encountered the address of the next instruction is predicted and instructions are fetched down the speculative path. When the branch instruction reaches the commit stage of the pipeline the prediction is verified. If a mis-prediction is detected the pipeline is flushed and the program counter is set to the correct instruction address. After a mis-prediction no

instructions are committed for several cycles. This branch penalty, for many processors, is equal to the total pipeline depth. Increasing pipeline depth, to increase clock frequency, also increases the latency of critical loops. The deeper pipeline (b) takes more cycles to resolve branch prediction and therefore suffers a larger mis-prediction penalty.

Similar to the branch prediction loop, increasing pipeline depth also increases latency of other critical loops. This increase in critical loop latency, in turn, reduces IPC. There is a tradeoff between increasing pipeline depth (and therefore clock frequency) and IPC. To obtain maximum performance processor designers must balance pipeline depth and IPC. We studied this tradeoff between pipeline depth and IPC. Chapter 2 presents our study in detail. We found that there is an optimal depth beyond which increasing pipeline depths any further will reduce overall performance.

## 1.2 Process Technology Trends

Process technology has continually fueled processor performance improvements. Every successive technology generation allows greater number of transistors to be packed on chip. Designers utilize the additional transistors in novel ways to improve the number of instructions per cycle (IPC) by building processor enhancements such as more sophisticated branch predictors, on-chip caches, better instruction scheduling mechanisms, structures to support out-of-order execution etc. Reducing feature sizes increases transistor switching speeds and so reduces gate delays. However, projections by the Semiconduc-

tor Industry Association show that technology scaling will cause an increase in wire delay relative to transistor delays [59]. This implies that in the future, even though designers will have a greater number of transistors, the fraction of the chip that can be accessed in a single cycle will decrease.

#### 1.2.1 Wire Delay Scaling

The delay to propagate signals across a wire is determined by three parameters: wire resistance, capacitance and inductance. An increase in wire resistance or capacitance will result in an increase in signal propagation delay. The resistance of the wire is determined by the equation

$$R = \rho * l/A \tag{1.1}$$

where R is the resistance of the wire,  $\rho$  is the resistivity of the material, l is the length of the wire, and A is its cross sectional area. As process technology shrinks the *thickness* and *width* of wires is reduced thereby reducing its cross sectional area. This change contributes to an increase in the resistance of the wire. On the other hand, smaller process technology also reduces the length of the wire which in turn reduces wire resistance.

The explanation for wire capacitance is more complicated due to the interaction of multiple conductors close to the wire (i.e. neighboring wires). The overall capacitance of a wire is usually modeled by four parallel-plate capacitors for the top, bottom, and either sides of the wire. The capacitance

of a parallel plate capacitor is determined by the equation

$$C = \epsilon * A/d \tag{1.2}$$

where C is capacitance,  $\epsilon$  is the permittivity of the material, A is the cross sectional area of the plates, and d is the distance between the plates. As process technology shrinks the wire surface area shrinks (i.e. the area of the plates) contributing to a reduction in the overall capacitance of the wire. However, smaller process technologies also reduce the the spacing between adjacent wires (i.e. distance between the plates) and this change contributes to an increase in overall wire capacitance.

As discussed above, reducing feature sizes results in multiple effects, some that reduce wire resistance and capacitance and some that increase it. The discussion of wire delay presented in this section is a simple, first-order explanation of the factors that contribute to wire resistance and capacitance. Ho et al. present a more detailed discussion of wire delay scaling with technology [34]. Their study shows that on-chip wires that scale in length (i.e. shorten as technology scales) have delays that track gate delays. However, the delays of wires that do not scale in length (i.e. global wires) scale poorly relative to transistors.

#### 1.2.2 Implications For Processor Design

Agarwal et al. studied the effect of increasing wire delays on on-chip structure latencies and processor performance [2, 3]. They show that because

of increasing wire delays, the latency of memory-oriented microarchitectural structures such as caches and register files increases as technology shrinks. To access such structures in single cycle will require either the capacity of the structures to be decreased or for clock frequencies to be scaled less aggressively.

They quantified the performance effect of scaling a superscalar processor from a 250nm technology to a 35nm technology. In this study they determined the access latencies of on-chip structures at different technology points using a modified version of CACTI [39]. Using a processor simulator, they evaluated the performance of an Alpha 21264-like superscalar processor at different technologies. Their study shows that as technology shrinks the IPC of the processor reduces due to increased structure latencies. Even though overall processor performance improves when it is scaled from 250nm to 35nm this improvement is lower than the increase in clock frequency over the same period. This result implies that even with the increased transistor budget the performance of a monolithic superscalar processor will scale at a rate lower than the clock frequency.

This study shows that the performance of large monolithic processor cores will not scale with technology. Furthermore, future designs that seek to exploit greater instruction level parallelism by issuing more instructions every cycle will require larger on-chip structures with more ports. Such structures cannot operate at high frequencies if designed as monolithic units. Future microarchitectures must be partitioned in order to reduce the access latency of critical structures. Such partitioning will result in a design wherein part of

a structure can be accessed in a single cycle while other parts will require multiple cycles. Though partitioning will enable structures to be clocked at high frequencies it introduces new bottlenecks that still restrict IPC. This dissertation proposes techniques to reduce the bottlenecks in clustered processors.

#### 1.3 Clustered Processors

In clustered superscalar processors on-chip structures such as the instruction issue window, the register file, the data-cache etc are physically partitioned. These partitions, along with functional units, are organized into groups called clusters. Several papers have previously suggested partitioning superscalar processors into clusters [5, 14, 22, 50]. Partitioning a monolithic design into clusters introduces new bottlenecks in the design that degrade the IPC of the clustered processor compared to the monolithic machine. Three factors degrade the IPC of clustered processors compared to a monolithic design. First is the communication delay to access remote operand values and remote memory values. The second factor is poor utilization of processor resources. In clustered processors on-chip resources such as physical registers, functional units, and issue windows are partitioned among clusters and this partitioning reduces overall efficiency. For example, instruction scheduling methods may steer many instructions to one cluster (and fewer instructions to other clusters) resulting in under-utilization of processor resources. The third factor that degrades the IPC of clustered machines is the extra transfer instructions used for inter-cluster communication. These instructions are dynamically generated by

the hardware to transfer operand values between clusters. These instructions do not perform useful computation but they still consume processor resources.

#### 1.4 Thesis Statement

Bottlenecks in clustered processors reduce its IPC compared to that of a monolithic machine. This dissertation proposes techniques to reduce the effects of these bottlenecks and enable a clustered processor to approach the IPC of a monolithic machine.

#### 1.5 Dissertation Contributions

In this dissertation we first explore the scalability of superscalar processor pipelines and show that increasing pipeline depth beyond a point will degrade performance. This performance degradation is because of the increase in latency of certain sections in the pipeline termed *critical loops*. We propose a method to pipeline the issue-wakeup critical loop that will allow the loop to operate in multiple cycles and yet not cause a significant degradation in IPC. This technique, along with methods that address other critical loops, may allow us to increase pipeline depths a little further. But in the longer term designers need to exploit more parallelism in programs to obtain greater performance. Processors will have to issue more instructions every cycle to achieve this goal. Such processors will have to be designed as clusters to reduce the design complexity of individual structures and to enable a high clock frequency.

We examine the bottlenecks in clustered superscalar processors and propose techniques to reduce their effect. We propose two techniques to remove the transfer instruction bottleneck, each of which replace transfer instructions with hardware signals. In the first method, called consumer requested forwarding (CRF), inter-cluster dependences are detected when consumer instructions reach the steer stage of the pipeline. Such consumer instructions set a bit in the producer instruction's cluster to forward the value to the consumer. The second method used to perform inter-cluster communication is called hot-register based forwarding. This mechanism tracks the registers that are used by each cluster and uses this information to predict where instruction outputs should be forwarded. We found that these techniques of orchestrating inter-cluster communication can almost eliminate all transfer instructions.

We also propose three dynamic instruction steering policies—issue-balance steering, memory steering, and critical-operand steering—to reduce the effect of the inter-cluster communication and cluster resource utilization bottlenecks. The issue-balance steering policy attempts to steer dependent instructions to the same cluster to reduce inter-cluster communication. However, if such an assignment will result in a cluster having more ready instructions than it can issue, instructions are re-assigned to another cluster to avoid stalls due to limited cluster issue-bandwidth. Thus, it attempts to find a balance between inter-cluster communication and processor resource utilization. The critical-operand steering policy attempts to reduce the effect of the intercluster communication latency. This policy identifies which of the two source

operands for an instruction is more critical and steers the instruction to the cluster that has fast access to that source operand. Memory-steering works in conjunction with the baseline policies and attempts to reduce the latency of load and store instructions by steering them to clusters with fast access to the data address being accessed. The issue-balance and critical-operand steering policies perform better than two of the three baseline steering mechanisms that we consider. The memory-steering mechanism shows an improvement over all three baseline steering policies.

### 1.6 Organization

In this chapter we provided a overview of this dissertation work. Chapter 2 examines processor pipeline scaling and shows that performance improvements from pipeline scaling are approaching diminishing returns. The results of this study imply that future processor designs must rely on extracting greater parallelism from the program to increase performance. To improve IPC processor issue widths must increase. Chapter 3 evaluates the SPEC 2000 benchmarks to show that they have considerable instruction level parallelism (ILP) and to determine the on-chip resources required to obtain this ILP. This section also describes our baseline clustered processor in detail. Chapter 4 evaluates the performance of the baseline processor and quantifies the improvement over the baseline if each bottleneck were individually removed. This study shows us the maximum benefit that can be achieved by removing the clustering bottlenecks. In Chapter 5 we propose and evaluate architectural

techniques to remove the transfer instruction bottleneck. The techniques that we propose eliminate almost all transfer instructions. We propose dynamic instruction steering mechanisms in Chapter 6. These steering policies attempt to reduce inter-cluster communication latency and the bottlenecks from poor processor resource utilization. Finally, Chapter 7 presents our concluding remarks.

## Chapter 2

## **Processor Pipeline Scaling**

Improvements in microprocessor performance have been sustained by increases in both instruction per cycle (IPC) and clock frequency. Increases in clock frequency have come from technology scaling, improvements in circuit design, and deeper pipelining of designs. In this chapter, we examine how much further reducing the amount of logic per pipeline stage can improve performance.

Reducing the logic per stage, and as a consequence increasing pipeline depth, is a technique to increase clock frequency and therefore overall performance. However, there are certain critical sections in a superscalar processor pipeline that must evaluate in the fewest possible cycles to achieve good performance. These sections are termed *critical loops* [15] and they include—issue wake-up loop, ALU to ALU forwarding, data-cache access and the branch mis-prediction loop. Increasing pipeline depth increases the latency of critical loops due to the additional clocking overhead that is added to the loop. This increase in critical loop latency, in turn, reduces IPC.

There is a tradeoff between increasing pipeline depth (and therefore clock frequency) and IPC. To obtain maximum performance processor de-

signers must balance pipeline depth and IPC. In this chapter we explore this tradeoff by scaling the pipeline depth of an Alpha 21264 processor. The remainder of this chapter is organized in the following manner. To determine the ideal clock frequency we first quantify latch overhead and present a detailed description of this methodology in Section 2.1. Section 2.2 describes the methodology to find the ideal clock frequency, which entails experiments with varied pipeline depths. We present the results of this study in Section 2.3 and discuss its implications. We examine individual critical loops in the pipeline in Section 2.4 and propose a new instruction window design in Section 2.5.

### 2.1 Estimating Overhead

The clock period of the processor is approximated by the following equation

$$\phi = \phi_{logic} + \phi_{latch} + \phi_{skew} + \phi_{jitter} \tag{2.1}$$

where  $\phi$  is the clock period,  $\phi_{logic}$  is useful work performed by logic circuits,  $\phi_{latch}$  is latch overhead,  $\phi_{skew}$  is clock skew overhead and  $\phi_{jitter}$  is clock jitter overhead. In this section, we describe our methodology for estimating the overhead components, and the resulting values.

A pipelined machine requires data and control signals at each stage to be saved at the end of every cycle. In the subsequent clock cycle this stored information is used by the following stage. Therefore, a portion of each clock period, called *latch overhead*, is required by latches to sample and hold values. Latches may be either edge triggered or level sensitive. Edge-triggered

Figure 2.1: Circuit diagram of a basic pulse latch.

latches reduce the possibility of race through, enabling simple pipeline designs, but typically incur higher latch overheads. Conversely, level-sensitive latches allow for design optimizations such as "slack-passing" and "time borrowing" [15], techniques that allow a slow stage in the pipeline to meet cycle time requirements by borrowing unused time from a neighboring, faster stage. In this paper we model a level-sensitive pulse latch, since it has low overhead and power consumption [32]. We use SPICE circuit simulations to quantify the latch overhead.

Figure 2.1 shows the circuit for a pulse latch consisting of a transmission gate followed by an inverter and a feed-back path. Data values are sampled and held by the latch as follows. During the period that the clock pulse is high, the transmission gate of the latch is on, and the output of the latch (Q) takes the same value as the input (D). When the clock signal changes to low, the transmission gate is turned off. However, the transistors along one of the

Figure 2.2: Timing diagram of a basic pulse latch. The shaded area indicates that the signal is valid.

Figure 2.3: Simulation setup to find latch overhead. The clock and data signals are buffered by a series of six inverters and the output drives a similar latch with its transmission gate turned on.

two feedback paths turn on, completing the feedback loop. The inverter and the feedback loop retain the sampled data value until the following clock cycle.

The operation of a latch is governed by three parameters—setup time  $(T_{su})$ , hold time  $(T_h)$ , and propagation delay  $(T_{dq})$ , as shown in Figure 2.2. To determine latch overhead, we measured its parameters using the test circuit shown in Figure 2.3. The test circuit consists of a pulse latch with its output driving another similar pulse latch whose transmission gate is turned on. On-

chip data and clock signals may travel through a number of gates before they terminate at a latch. To simulate the same effect, we buffer the clock and data inputs to the latch by a series of six inverters. The clock signal has a 50% duty cycle while the data signal is a simple step function. We simulated transistors at 100nm technology and performed experiments similar to those by Stojanović et al. [67], using the same P-transistor to N-transistor ratios. In our experiments, we moved the data signal progressively closer to the falling edge of the clock signal. Eventually when D changes very close to the falling edge of the Clk signal the latch fails to hold the correct value of D. Latch overhead is the smallest of the D-Q delays before this point of failure [67]. We estimated latch overhead to be 36ps (1 FO4) at 100nm technology. Since this delay is determined by the switching speed of transistors, which is expected to scale linearly with technology, its value in FO4 will remain constant at all technologies. Note that the transistor feature sizes we refer to are the drawn gate length as opposed to the effective gate length.

In addition to latch overhead, clock skew and jitter also add to the total overhead of a clock period. A recent study by Kurd *et al.* [43] showed that, by partitioning the chip into multiple clock domains, clock skew can be reduced to less than 20ps and jitter to 35ps. They performed their studies at 180nm, which translates into 0.3 FO4 due to skew and 0.5 FO4 due to jitter. Many components of clock skew and jitter are dependent on the speed of the components, and those that are dependent on the transistor components should scale with technology. However, other terms, such as delay due to

| Symbol            | Definition      | Overhead |  |

|-------------------|-----------------|----------|--|

| $\phi_{latch}$    | Latch Overhead  | 1.0 FO4  |  |

| $\phi_{skew}$     | Skew Overhead   | 0.3  FO4 |  |

| $\phi_{jitter}$   | Jitter Overhead | 0.5  FO4 |  |

| $\phi_{overhead}$ | Total           | 1.8 FO4  |  |

Table 2.1: Overheads due to latch, clock skew and jitter.

process variation, may scale differently, hence affecting the overall scalability. For simplicity we assume that clock skew and jitter will scale linearly with technology and therefore their values in FO4 will remain constant. Table 2.1 shows the values of the different overheads that we use to determine the overall clock period. The total overhead ( $\phi_{overhead}$ ), the sum of latch, clock skew and jitter overhead is equal to 1.8 FO4.

# 2.2 Pipeline Scaling Methodology

To study the effect of deeper pipelining on performance, we varied the pipeline depth of a modern superscalar architecture similar to the Alpha 21264. This section describes our simulation framework and the methodology we used to perform this study.

We used a simulator developed by Desikan *et al.* that models both the low-level features of the Alpha 21264 processor [20] and the execution core in detail. This simulator has been validated to be within an accuracy of 21% of a Compaq DS-10L workstation. For our experiments, the base latency and capacities of on-chip structures matched those of the Alpha 21264, and

| Integer              | Floating Point        |  |  |

|----------------------|-----------------------|--|--|

| 164.gzip             | $171.\mathrm{swim}$   |  |  |

| $175.\mathrm{vpr}$   | $172.\mathrm{mgrid}$  |  |  |

| $176.\mathrm{gcc}$   | 173.applu             |  |  |

| 181.mcf              | 177.mesa              |  |  |

| 197.parser           | $178.\mathrm{galgel}$ |  |  |

| $252.\mathrm{eon}$   | $179.\mathrm{art}$    |  |  |

| 253.perlbmk          | 183.equake            |  |  |

| $256.\mathrm{bzip}2$ | $188.\mathrm{ammp}$   |  |  |

|                      | $189. { m lucas}$     |  |  |

Table 2.2: SPEC 2000 benchmarks used in all simulation experiments.

the level-2 cache was configured to be 2MB. The capacities of the integer and floating-point register files were increased to 512 each, so that the performance of deep pipelines was not unduly constrained due to unavailability of registers. We modified the execution core of the simulator to permit the addition of more stages to different parts of the pipeline. The modifications allowed us to vary the pipeline depth of different parts of the processor pipeline, including the execution stage, the register read stage, the issue stage, and the commit stage.

Table 2.2 lists the benchmarks that we simulated for our experiments, which include integer and floating-point benchmarks taken from the SPEC 2000 suite. All experiments skip the first 500 million instructions of each benchmark and simulate the next 500 million instructions.

We use Cacti to model on-chip microarchitectural structures and to estimate their access times [39]. All major microarchitectural structures—data cache, register file, branch predictor, register rename table and instruction

issue window—were modeled at 100nm technology and their capacities and configurations were chosen to match the corresponding structures in the Alpha 21264. We use the latencies of the structures obtained from Cacti to compute their access penalties (in cycles) at different clock frequencies.

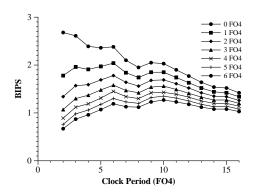

## 2.3 Optimal Pipeline Depth

We find the clock frequency that will provide maximum performance by simulating processor pipelines clocked at different frequencies. The clock period of the processor is determined by the following equation:  $\phi = \phi_{logic} + \phi_{overhead}$ . The overhead term is held constant at 1.8 FO4, as discussed in Section 2.1. We vary the clock frequency  $(1/\phi)$  by varying  $\phi_{logic}$  from 2 FO4 to 16 FO4. The number of pipeline stages (clock cycles) required to access an on-chip structure, at each clock frequency, is determined by dividing the access time of the structure by the corresponding  $\phi_{logic}$ . For example, if the access time of the level-1 cache at 100nm technology is 0.28ns (8 FO4), for a pipeline where  $\phi_{logic}$  equals 2 FO4 (0.07ns), the cache can be accessed in 4 cycles.

Though we use a 100nm technology in this study, the access latencies at other technologies in terms of the FO4 metric will remain largely unchanged at each corresponding clock frequency, since delays measured in this metric are technology independent. Table 2.3 shows the access latencies of structures at each  $\phi_{logic}$ . These access latencies were determined by dividing the structure latencies (in pico seconds) obtained from the cacti model by the corresponding

|                      |     | Branch                     | Rename                 | Issue  | Register              |

|----------------------|-----|----------------------------|------------------------|--------|-----------------------|

| $\phi_{logic}$ (FO4) | DL1 | $\operatorname{Predictor}$ | $\operatorname{Table}$ | Window | $\operatorname{File}$ |

| 2                    | 16  | 10                         | 9                      | 9      | 6                     |

| 3                    | 11  | 7                          | 6                      | 6      | 4                     |

| 4                    | 9   | 5                          | 5                      | 5      | 3                     |

| 5                    | 7   | 4                          | 4                      | 4      | 3                     |