Copyright

by

Renee Marie St Amant

2014

The Dissertation Committee for Renee Marie St Amant certifies that this is the approved version of the following dissertation:

**Enabling High-Performance, Mixed-Signal Approximate Computing**

Committee:

---

Calvin Lin, Supervisor

---

Doug Burger, Co-Supervisor

---

Daniel A. Jiménez

---

Lizy K. John

---

Donald Fussell

**Enabling High-Performance, Mixed-Signal Approximate

Computing**

**by**

**Renee Marie St Amant, B.S.E.E.; M.S.C.S.**

**DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN

May 2014

To my godchild, Cameron.

## Acknowledgments

I would like to thank and acknowledge technical collaborators Doug Burger, Daniel A. Jiménez, Hadi Esmaeilzadeh, Amir Yazdanbakhsh, and Arjang Hassibi who have contributed to the body of work presented in this document. I wish to thank Doug Burger for his sustained support and invaluable guidance. I feel extremely privileged to have had access to his deep technical knowledge, experience, and vision of computing. I also wish to thank Calvin Lin for his support and always-enthusiastic willingness to be of service. Thank you to my committee members, conference reviewers, fellow students, and friends for your valuable feedback and suggestions for improving this work. Specifically, thank you to Lizy K. John who suggested that I revisit the history of analog computing. That investigation served as the foundation and driving inspiration for the composition of this document.

To my parents – thank you for consistently supporting me in receiving the best education possible. And to my father – thank you for the countless hours spent with me in perfecting every sentence of my high-school writing assignments. I’m sure that you will find your writing style present throughout this document.

I wish to thank Travis M. Grigsby for his years of support and encouragement. His copious enthusiasm and belief in the abilities of others has been

a gift to me and to the world. I wish to thank Elizabeth Frances Wellman for all of her time, her uncompromising support, and her commitment to being a good friend, which has served as a valuable example to me. She is truly skilled in her work, and I have been blessed to benefit from it so often. Also, I wish to thank Hadi Esmaeilzadeh for his ‘get it done’ support during critical moments of this journey. Thank you to those that I now consider family. Your nourishing love and support have helped me to complete this process.

# Enabling High-Performance, Mixed-Signal Approximate Computing

Renee Marie St Amant, Ph.D.

The University of Texas at Austin, 2014

Supervisors: Calvin Lin

Doug Burger

For decades, the semiconductor industry enjoyed exponential improvements in microprocessor power and performance with the device scaling of successive technology generations. Scaling limitations at sub-micron technologies, however, have ceased to provide these historical performance improvements within a limited power budget. While device scaling provides a larger number of transistors per chip, for the same chip area, a growing percentage of the chip will have to be powered off at any given time due to power constraints. As such, the architecture community has focused on energy-efficient designs and is looking to specialized hardware to provide gains in performance.

A focus on energy efficiency, along with increasingly less reliable transistors due to device scaling, has led to research in the area of *approximate computing*, where *accuracy* is traded for *energy efficiency* when precise computation is not required. There is a growing body of approximation-tolerant

applications that, for example, compute on noisy or incomplete data, such as real-world sensor inputs, or make approximations to decrease the computation load in the analysis of cumbersome data sets. These approximation-tolerant applications span application domains, such as machine learning, image processing, robotics, and financial analysis, among others.

Since the advent of the modern processor, computing models have largely presumed the attribute of accuracy. A willingness to relax accuracy requirements, however, with goal of gaining energy efficiency, warrants the re-investigation of the potential of analog computing. Analog hardware offers the opportunity for fast and low-power computation; however, it presents challenges in the form of accuracy. Where analog compute blocks have been applied to solve fixed-function problems, general-purpose computing has relied on digital hardware implementations that provide generality and programmability. The work presented in this thesis aims to answer the following questions:

*Can analog circuits be successfully integrated into general-purpose computing to provide performance and energy savings? And, what is required to address the historical analog challenges of inaccuracy, programmability, and a lack of generality to enable such an approach?*

This thesis work suggests a *neural* approach as a means to address the historical analog challenges in accuracy, programmability, and generality and to enable the use of analog circuits in high-performance, general-purpose computing. The first piece of this thesis work investigates the use of analog circuits at the microarchitecture level in the form of an analog neural branch

predictor. The task of branch prediction can tolerate imprecision, as roll-back mechanisms correct for branch mispredictions, and application-level accuracy remains unaffected. We show that analog circuits enable the implementation of a highly-accurate, neural-prediction algorithm that is infeasible to implement in the digital domain. The second piece of this thesis work presents a neural accelerator that targets approximation-tolerant code. Analog neural acceleration provides application speedup of 3.3x and energy savings of 12.1x with a quality loss less than 10% for all except one approximation-tolerant benchmark. These results show that, through a neural approach, analog circuits can be applied to provide performance and energy efficiency in high-performance, general-purpose computing.

# Table of Contents

|                                                                          |             |

|--------------------------------------------------------------------------|-------------|

| <b>Acknowledgments</b>                                                   | <b>v</b>    |

| <b>Abstract</b>                                                          | <b>vii</b>  |

| <b>List of Tables</b>                                                    | <b>xiii</b> |

| <b>List of Figures</b>                                                   | <b>xiv</b>  |

| <b>Chapter 1. Introduction</b>                                           | <b>1</b>    |

| 1.1 Problem . . . . .                                                    | 1           |

| 1.2 Opportunity . . . . .                                                | 3           |

| 1.3 Solutions and Contributions . . . . .                                | 4           |

| <b>Chapter 2. Context</b>                                                | <b>9</b>    |

| 2.1 A Brief History of Analog Computing . . . . .                        | 9           |

| 2.2 Neural Networks for Computing . . . . .                              | 12          |

| 2.3 Approximate Computing . . . . .                                      | 14          |

| <b>Chapter 3. Challenges of an Analog Approach to Neural Computation</b> | <b>16</b>   |

| 3.1 Review of Neural Network Computation . . . . .                       | 16          |

| 3.2 Challenges of an Analog Approach . . . . .                           | 18          |

| 3.2.1 Design-Time Signal-Range Restrictions . . . . .                    | 18          |

| 3.2.2 Manufacture-Time Non-Idealities . . . . .                          | 22          |

| 3.2.3 Run-Time Noise . . . . .                                           | 22          |

| 3.2.4 Analog-Digital Boundaries . . . . .                                | 23          |

| 3.3 Analog Challenges in Classification and Regression . . . . .         | 24          |

|                                                                |           |

|----------------------------------------------------------------|-----------|

| <b>Chapter 4. Analog Neural Prediction</b>                     | <b>27</b> |

| 4.1 Background on Neural Predictors . . . . .                  | 28        |

| 4.1.1 The Perceptron Predictor . . . . .                       | 29        |

| 4.1.2 Improvements to the Perceptron Predictor . . . . .       | 30        |

| 4.2 Analog-Enabled Neural Prediction Algorithm . . . . .       | 30        |

| 4.3 Scaled Neural Analog Predictor . . . . .                   | 35        |

| 4.4 Addressing Analog Challenges . . . . .                     | 41        |

| 4.5 Evaluation . . . . .                                       | 43        |

| 4.5.1 Methodology . . . . .                                    | 43        |

| 4.5.2 Analog Power, Speed, and Accuracy . . . . .              | 45        |

| 4.5.3 Analog vs. Digital Comparison . . . . .                  | 48        |

| 4.5.4 State-of-the-Art Predictors . . . . .                    | 50        |

| 4.6 Conclusions and Implications . . . . .                     | 52        |

| 4.6.1 Contributions . . . . .                                  | 53        |

| <b>Chapter 5. Analog Neural Acceleration</b>                   | <b>55</b> |

| 5.1 Background and Overview . . . . .                          | 58        |

| 5.1.1 Programming . . . . .                                    | 59        |

| 5.1.2 Design . . . . .                                         | 60        |

| 5.1.3 Compilation . . . . .                                    | 61        |

| 5.1.4 Execution . . . . .                                      | 63        |

| 5.2 Mixed-Signal, Neural Accelerator (A-NPU) Design . . . . .  | 63        |

| 5.2.1 Analog Neural Unit (ANU) Circuit Design . . . . .        | 64        |

| 5.2.2 Reconfigurable A-NPU . . . . .                           | 75        |

| 5.3 Compilation to Address Analog-Imposed Challenges . . . . . | 78        |

| 5.3.1 Addressing Topology Restrictions . . . . .               | 79        |

| 5.3.2 Addressing Activation-Function Restrictions: RPROP . .   | 81        |

| 5.3.3 Addressing Limited Bit Widths: CDLM . . . . .            | 88        |

| 5.4 Performance and Energy Evaluation . . . . .                | 99        |

| 5.4.1 Methodology . . . . .                                    | 99        |

| 5.4.2 Analog-Digital NPU Comparison . . . . .                  | 103       |

| 5.5 Future Considerations for Addressing Analog Challenges . . | 106       |

|                     |                                                            |            |

|---------------------|------------------------------------------------------------|------------|

| 5.5.1               | Addressing Manufacture-Time Variability . . . . .          | 107        |

| 5.5.2               | Addressing Run-Time Variability . . . . .                  | 108        |

| 5.6                 | Conclusions . . . . .                                      | 110        |

| <b>Chapter 6.</b>   | <b>Related Work</b>                                        | <b>113</b> |

| 6.1                 | Approximate Computing . . . . .                            | 113        |

| 6.2                 | Analog and Digital Hardware for Neural Networks . . . . .  | 116        |

| 6.3                 | Learning Techniques for Hardware Neural Networks . . . . . | 122        |

| <b>Chapter 7.</b>   | <b>Conclusions</b>                                         | <b>128</b> |

| <b>Bibliography</b> |                                                            | <b>135</b> |

## List of Tables

|     |                                                                                                                               |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Excerpts from the list of DAC transistor widths [121] . . . . .                                                               | 38  |

| 5.1 | Area estimates for the analog neuron (ANU) [4]. . . . .                                                                       | 100 |

| 5.2 | The evaluated benchmarks, characterization of each offloaded function, training data, and the trained neural network [4]. . . | 102 |

| 5.3 | Error with a floating point D-NPU, A-NPU with ideal sigmoid, and A-NPU with non-ideal sigmoid [4]. . . . .                    | 105 |

# List of Figures

|     |                                                                                                                                                                                                                                                             |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Desirable attributes of computation devices. . . . .                                                                                                                                                                                                        | 2  |

| 1.2 | Neural prediction: addressing analog shortcomings. . . . .                                                                                                                                                                                                  | 6  |

| 1.3 | Neural acceleration: addressing analog shortcomings. . . . .                                                                                                                                                                                                | 7  |

| 2.1 | Neural network design space. As computing tools, neural-network designs trade off the desirable attributes of a computing device (shown in Figure 1.1): performance, energy efficiency, result quality (accuracy), programmability, and generality. . . . . | 12 |

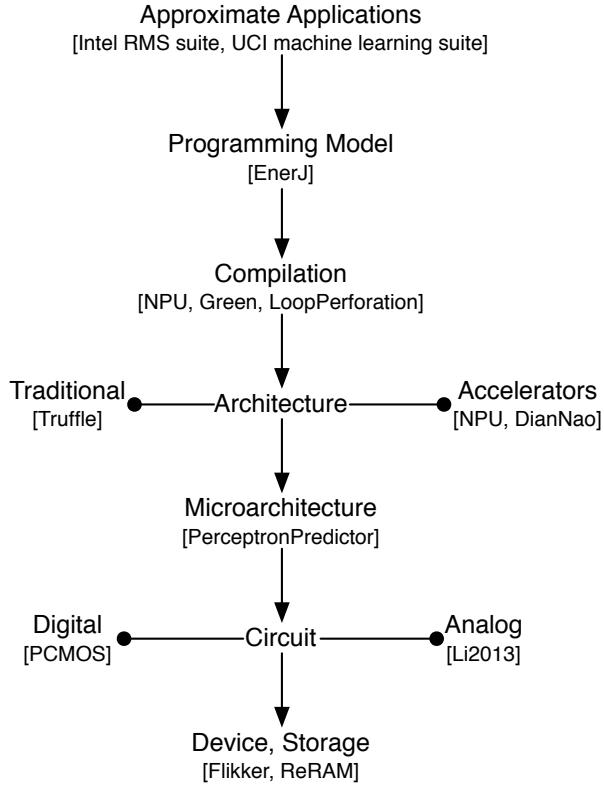

| 2.2 | Research areas in approximate computing. . . . .                                                                                                                                                                                                            | 14 |

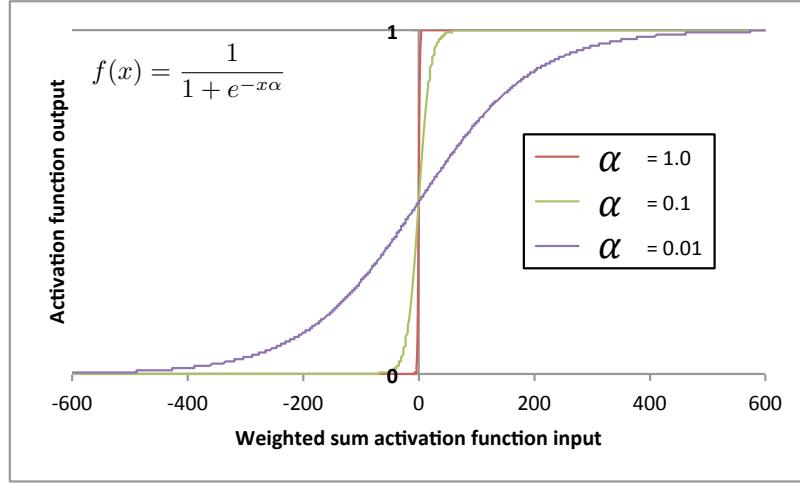

| 3.1 | Sigmoid function with varying activation steepness ( $\alpha$ ). Activation steepness determines the numerical range of input values that translate to output values between 0 and 1. . . . .                                                               | 20 |

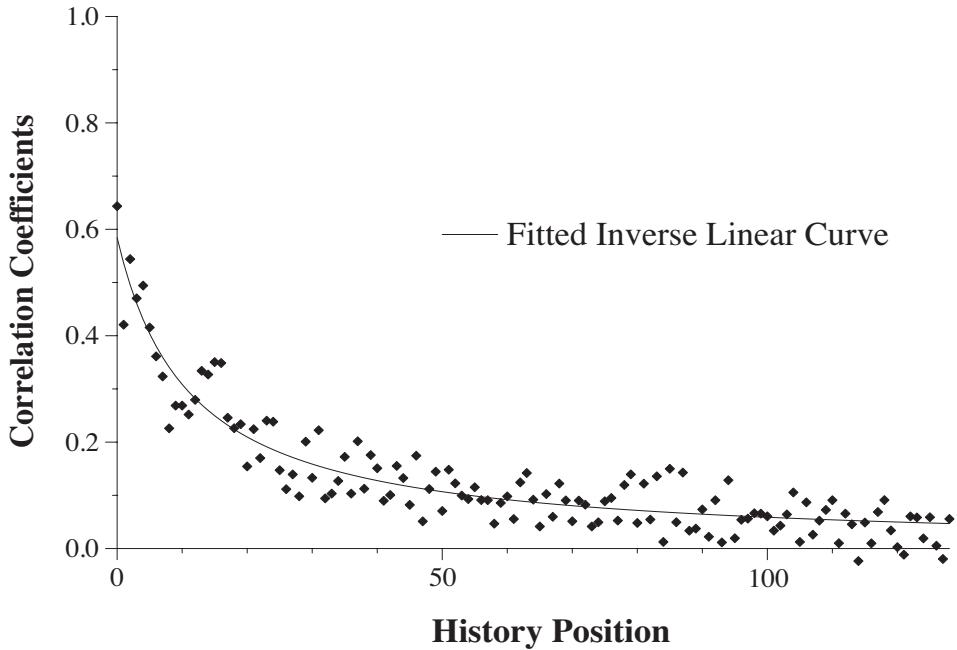

| 4.1 | Weight position and branch outcome correlation [121] . . . . .                                                                                                                                                                                              | 31 |

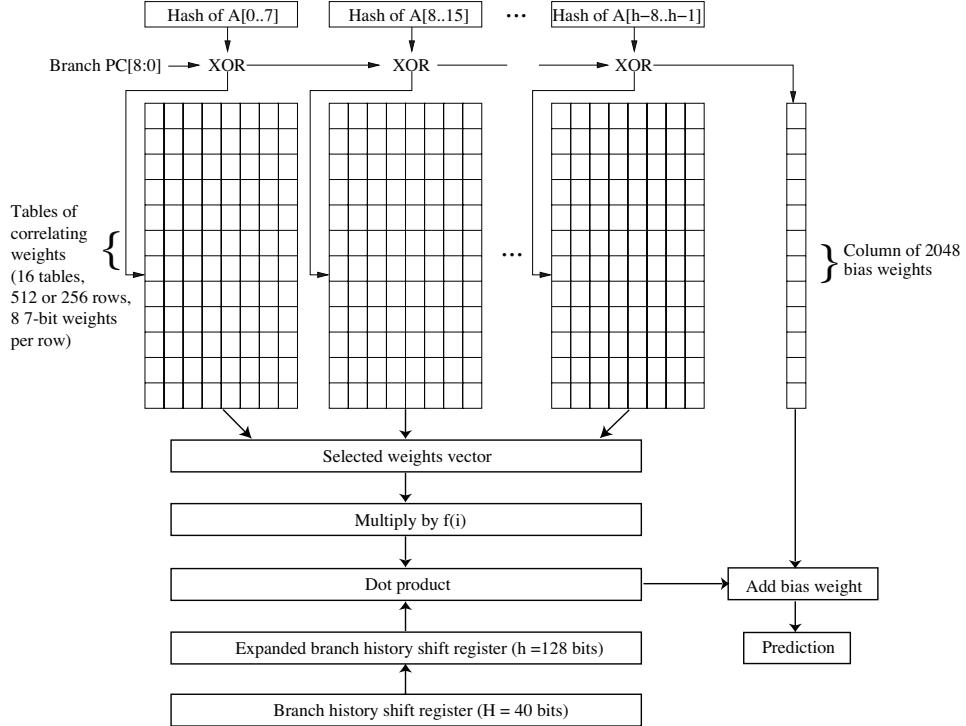

| 4.2 | Prediction data path [121] . . . . .                                                                                                                                                                                                                        | 33 |

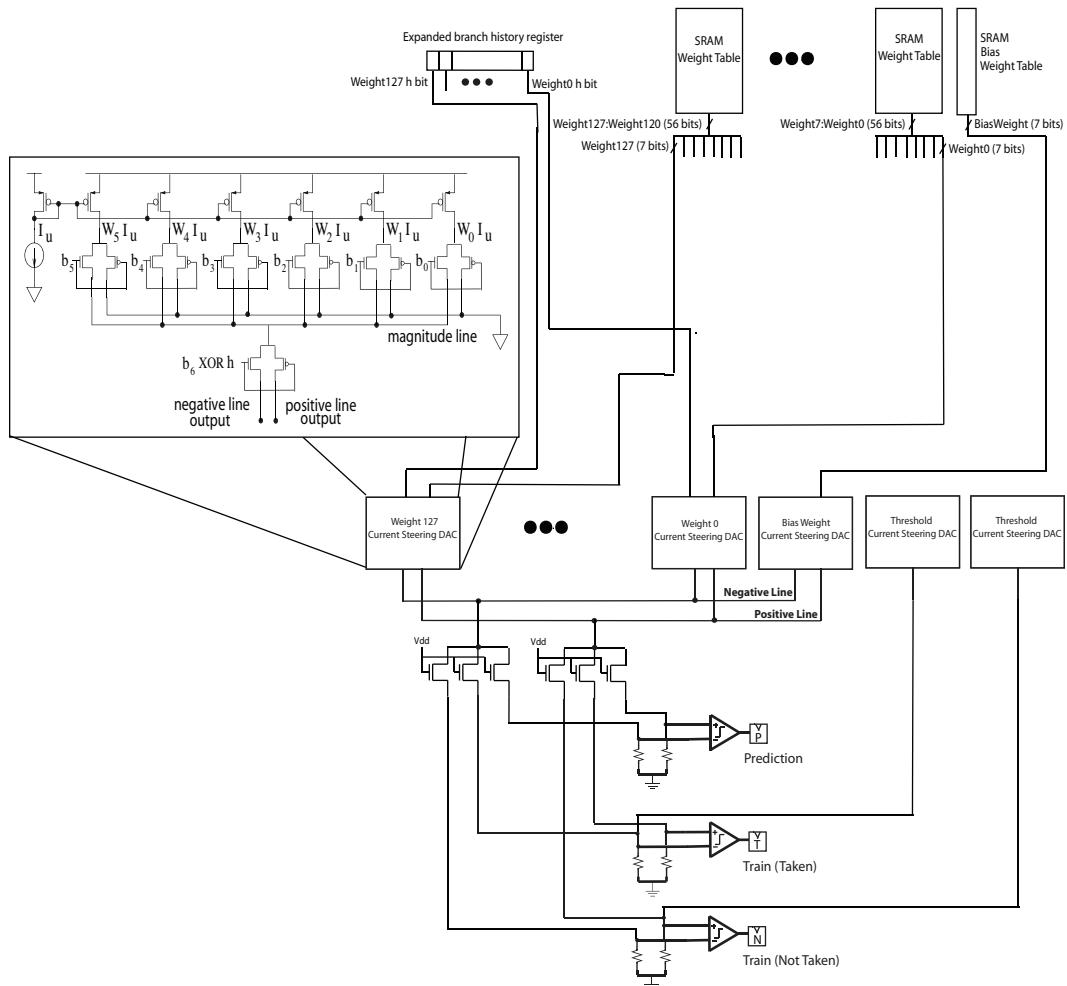

| 4.3 | Top-level diagram of a Scaled Neural Analog Predictor . . . .                                                                                                                                                                                               | 36 |

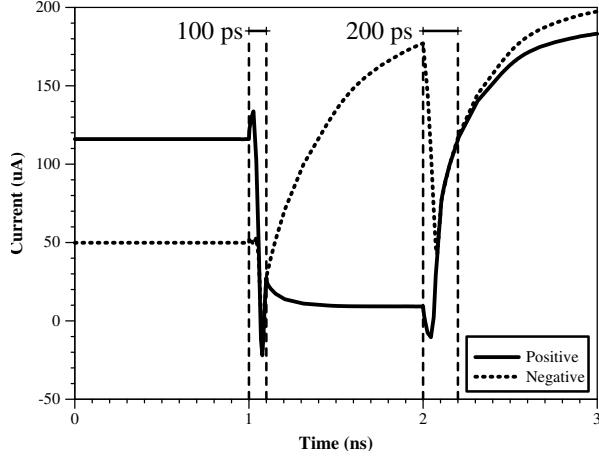

| 4.4 | Time required for current differentiation . . . . .                                                                                                                                                                                                         | 45 |

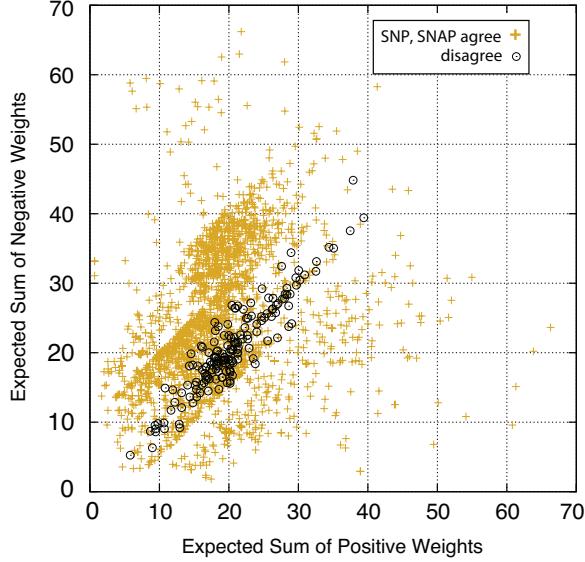

| 4.5 | Prediction errors for sum combinations . . . . .                                                                                                                                                                                                            | 46 |

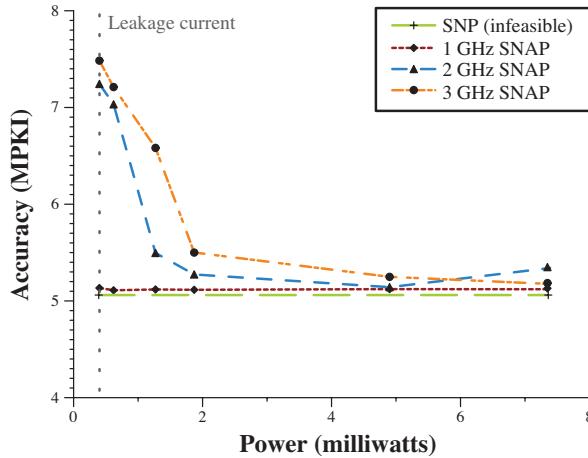

| 4.6 | Tradeoff between power, speed, and accuracy . . . . .                                                                                                                                                                                                       | 47 |

| 4.7 | Accuracy of digital vs. analog implementations of the Scaled Neural Predictor . . . . .                                                                                                                                                                     | 48 |

| 5.1 | Framework for using analog computation to accelerate code written in conventional languages [4]. . . . .                                                                                                                                                    | 58 |

| 5.2 | One neuron and its conceptual analog circuit [4]. . . . .                                                                                                                                                                                                   | 64 |

| 5.3 | Circuit design of a single analog neuron (ANU). . . . .                                                                                                                                                                                                     | 66 |

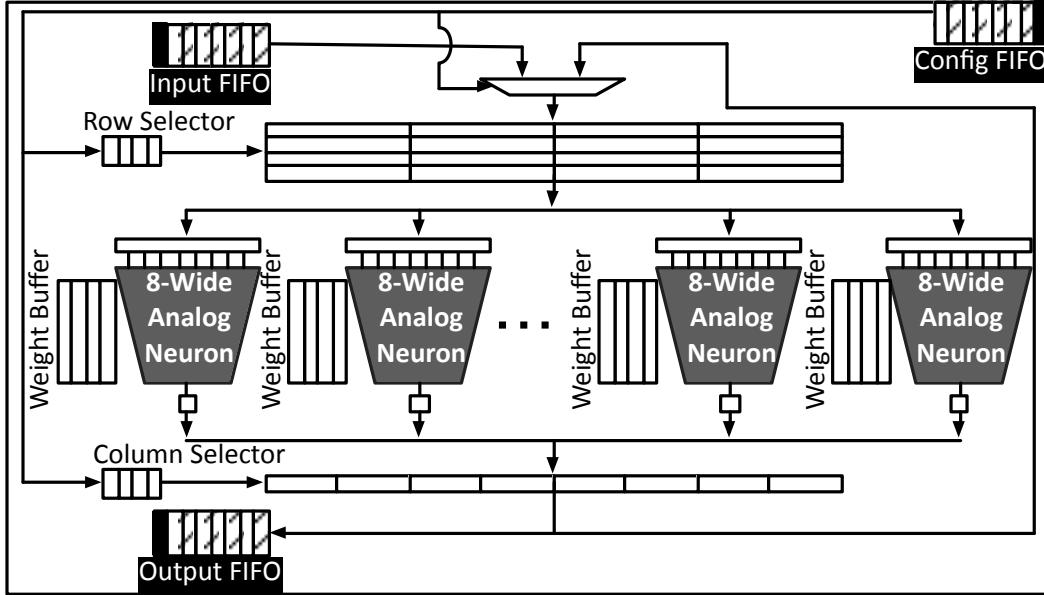

| 5.4 | Mixed-signal, neural accelerator (A-NPU). Only four ANUs are shown. Each ANU processes eight inputs [4]. . . . .                                                                                                                                            | 75 |

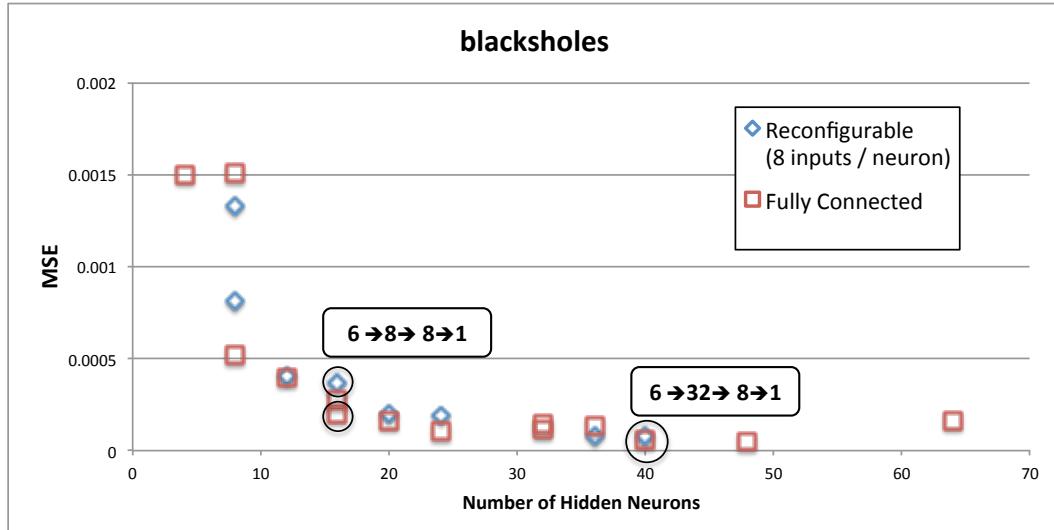

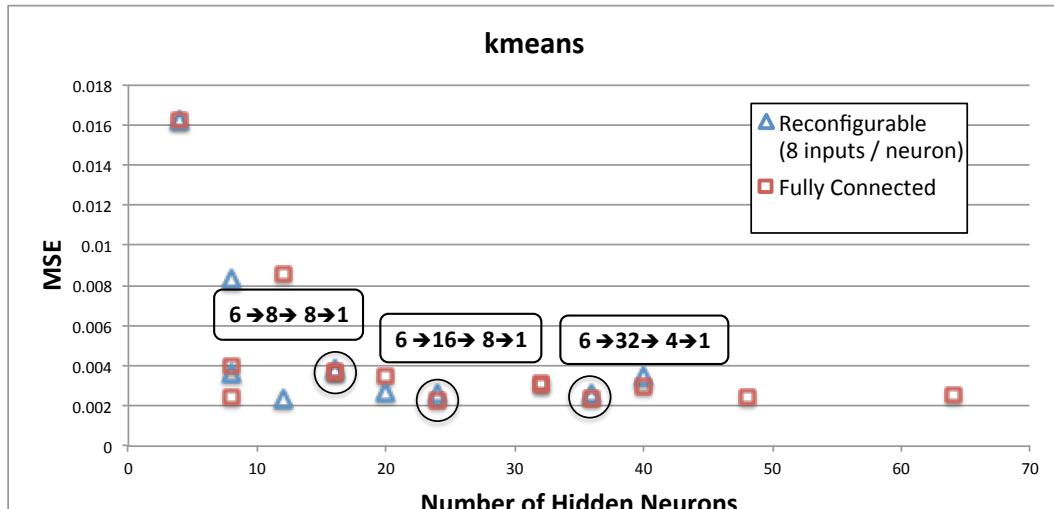

| 5.5 | Network accuracies for limited (eight inputs per neuron), but reconfigurable, network topologies and fully connected topologies. . . . .                                                                                                                    | 82 |

|      |                                                                                                                                                                                                                                                                                                                                          |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

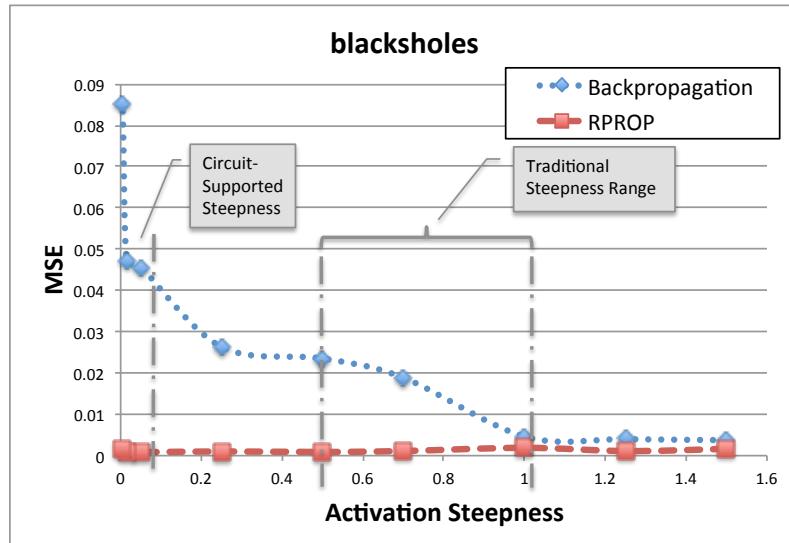

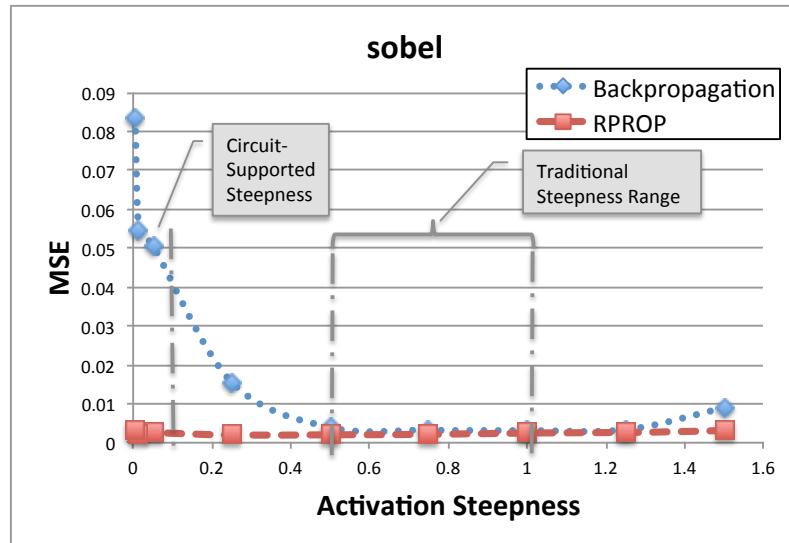

| 5.6  | Backpropagation and resilient propagation (RPROP) sensitivity to activation-function steepness. . . . .                                                                                                                                                                                                                                  | 86  |

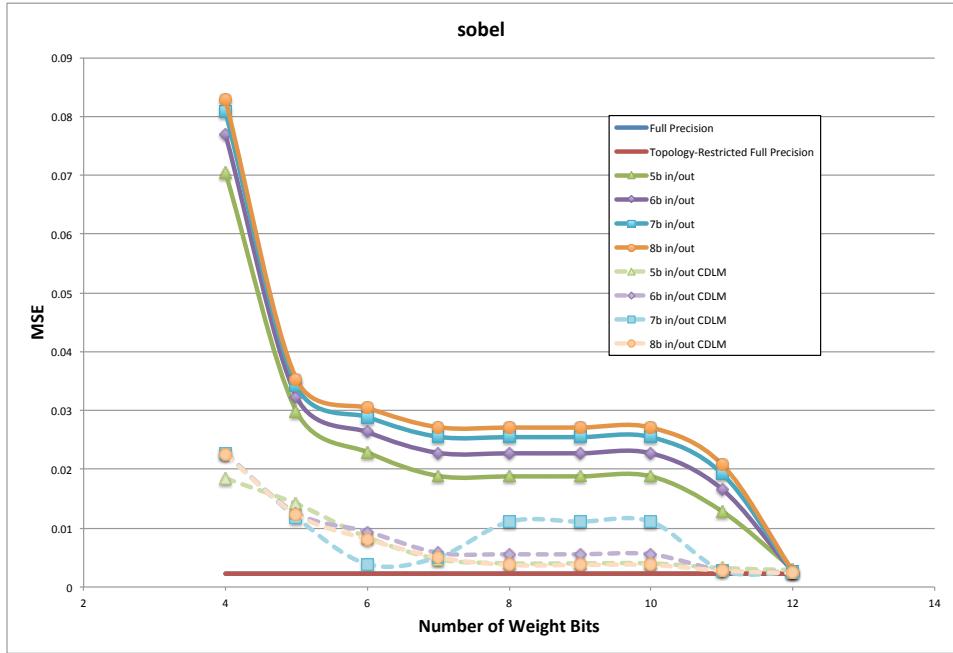

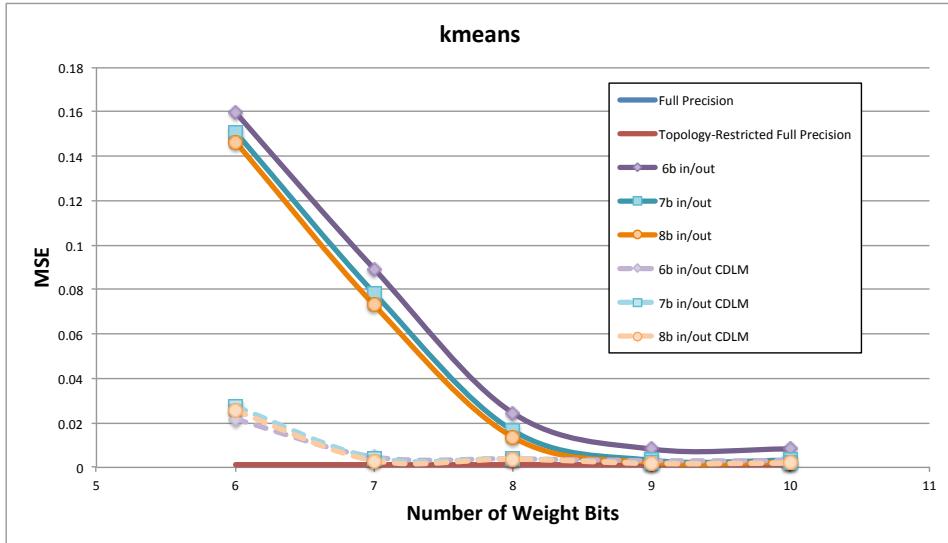

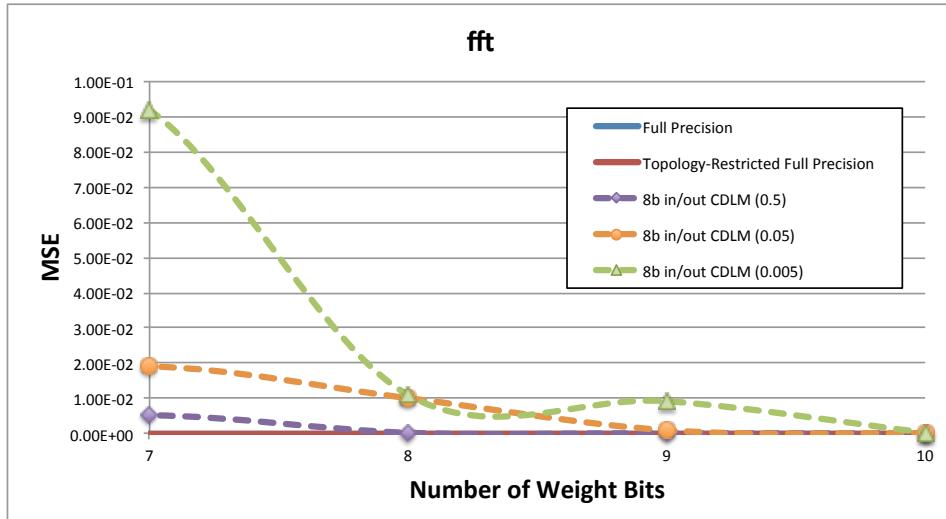

| 5.7  | Continuous-discrete learning method (CDLM) compensates for limited bit widths. Results show accuracy for three-layer networks with 8 hidden neurons and a traditional activation steepness of 0.5. The number of network inputs for <code>sobel</code> and <code>jpeg</code> exceed the analog-imposed connectivity restriction. . . . . | 91  |

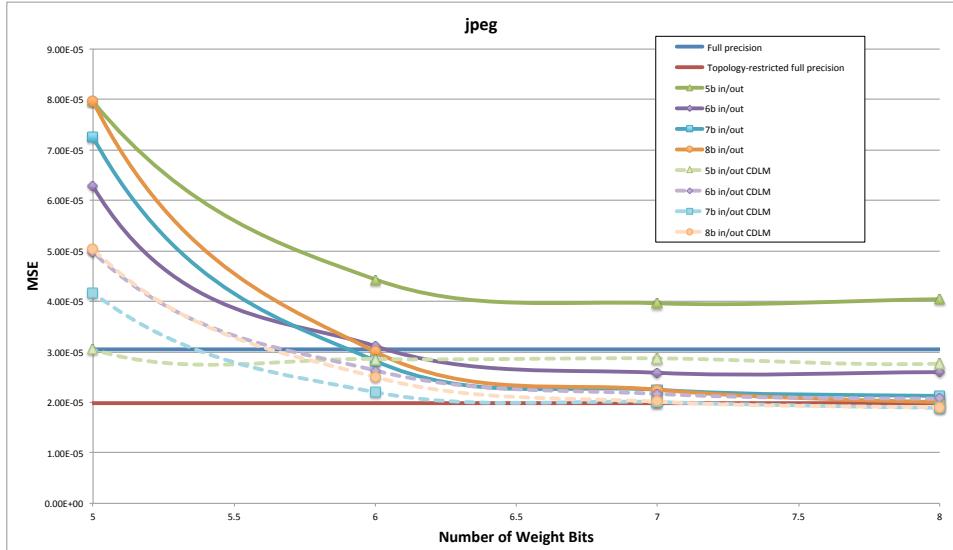

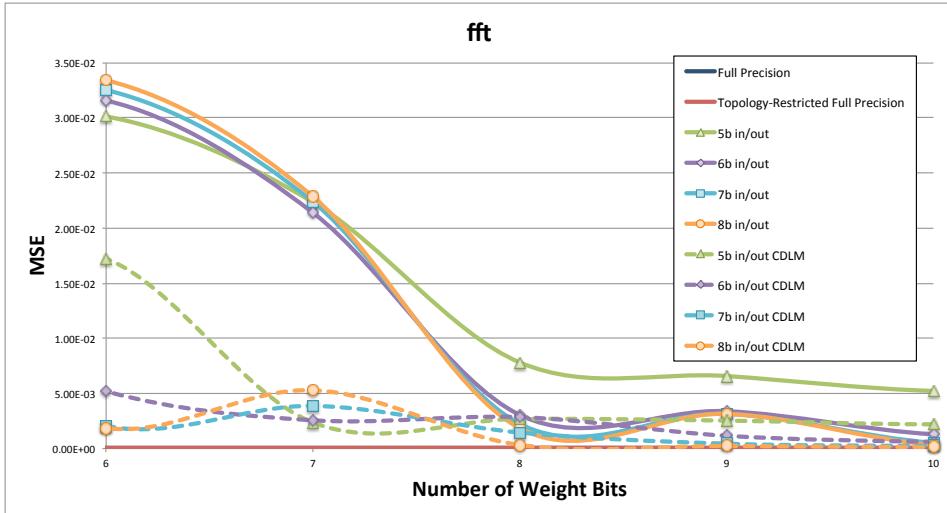

| 5.8  | Continuous-discrete learning method (CDLM) compensates for limited bit widths. Results show accuracy for a three-layer network with 8 hidden neurons and a traditional activation steepness of 0.5. . . . .                                                                                                                              | 92  |

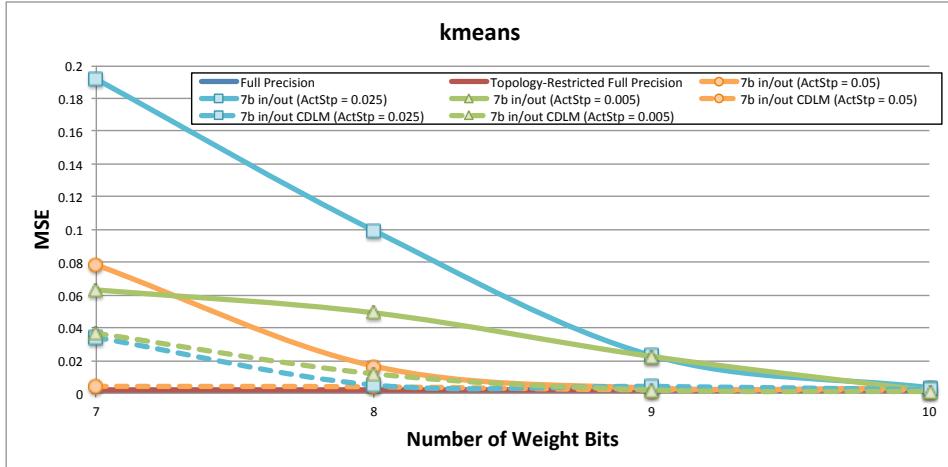

| 5.9  | CDLM and bit-width sensitivity to activation steepness for <code>kmeans</code> (three-layer network with 8 hidden neurons). The full-precision baselines correspond to a traditional activation steepness of 0.5. . . . .                                                                                                                | 94  |

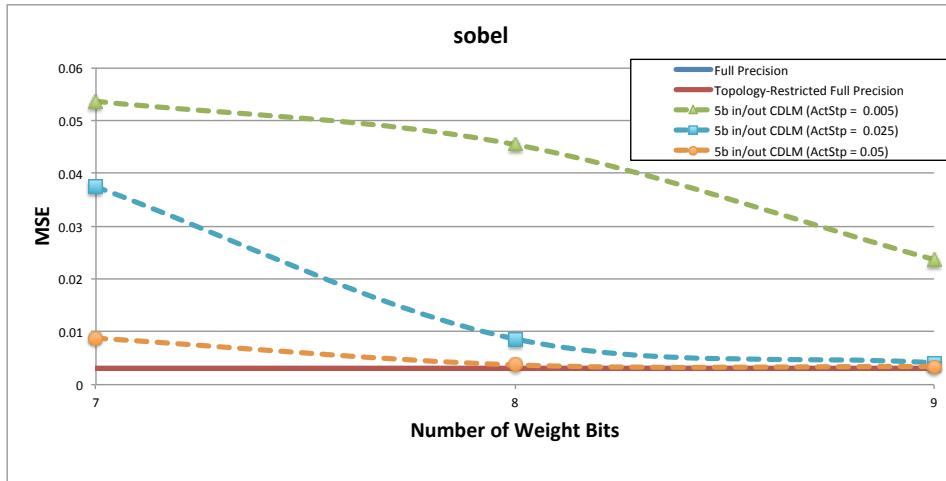

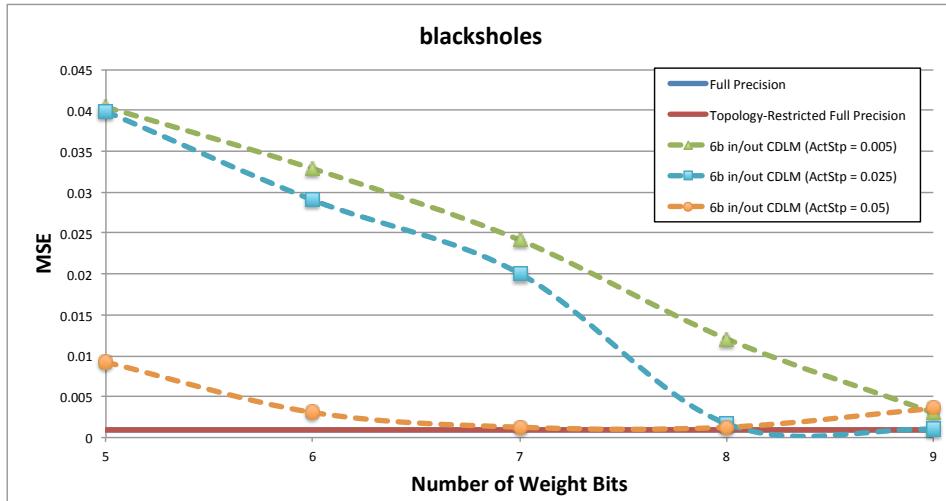

| 5.10 | Bit width sensitivity to activation steepness. The full-precision baselines correspond to a traditional activation steepness of 0.5. . . . .                                                                                                                                                                                             | 96  |

| 5.11 | Bit width sensitivity to activation steepness. The full-precision baselines correspond to a traditional activation steepness of 0.5. . . . .                                                                                                                                                                                             | 97  |

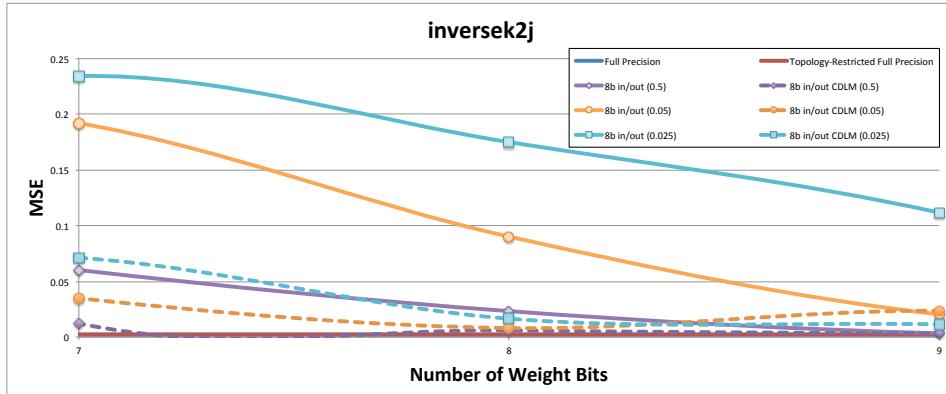

| 5.12 | CDLM accuracy for <code>jpeg</code> (three-layer network with 8 hidden neurons, 64 inputs, and 64 outputs) for varying activation steepness values. The full-precision baselines correspond to a traditional activation steepness of 0.5. . . . .                                                                                        | 98  |

| 5.13 | A-NPU with 8 ANUs vs. D-NPU with 8 PEs [4]. . . . .                                                                                                                                                                                                                                                                                      | 103 |

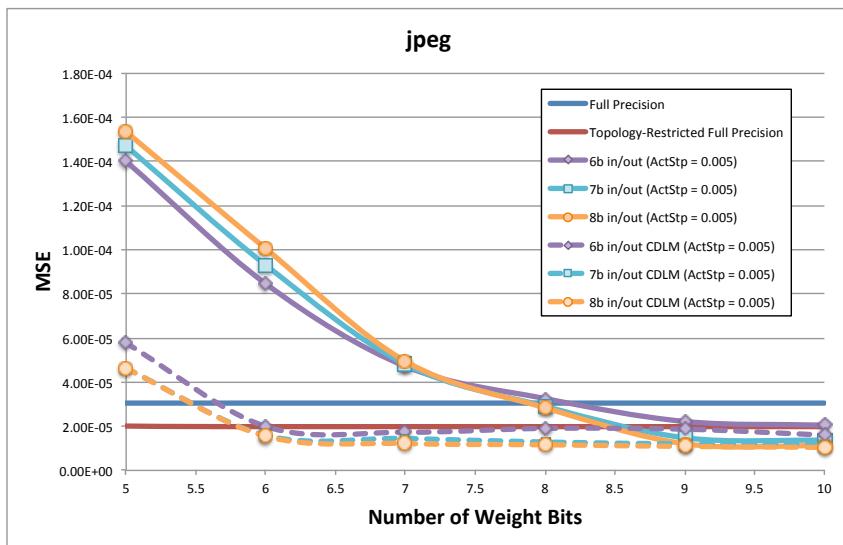

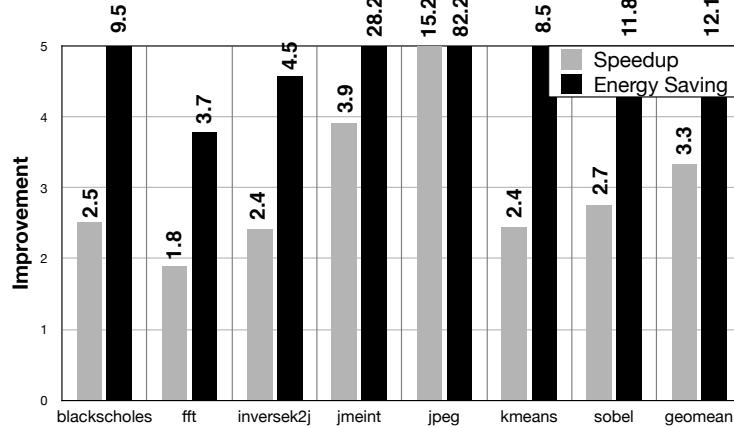

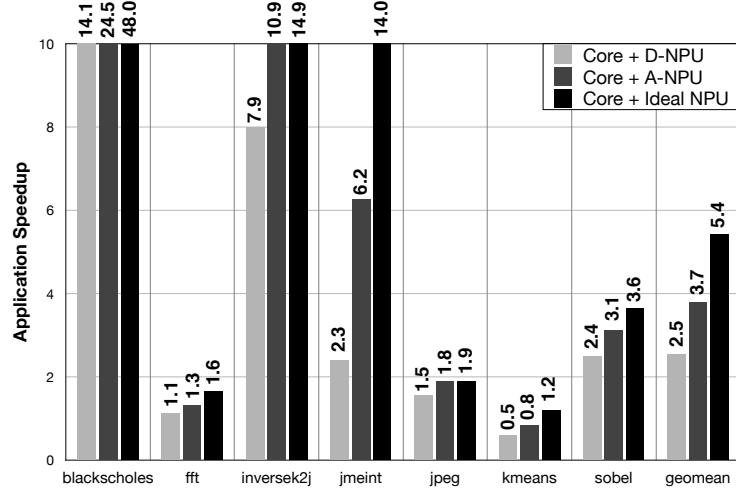

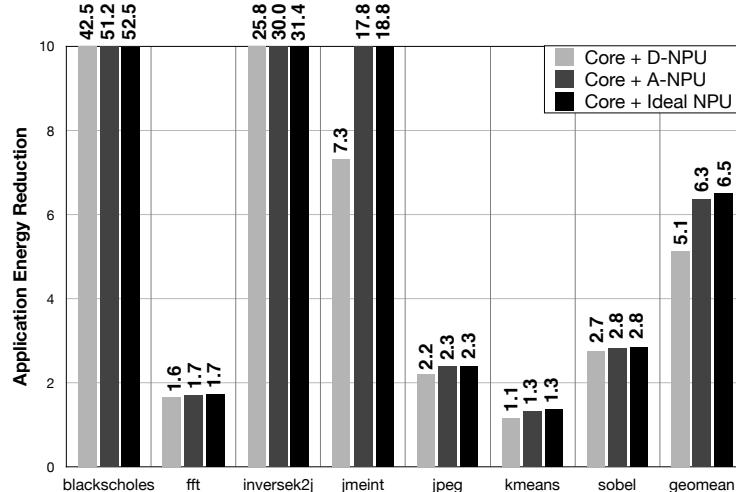

| 5.14 | Whole application speedup and energy saving with D-NPU, A-NPU, and an ideal NPU that consumes zero energy and takes zero cycles for neural computation [4]. . . . .                                                                                                                                                                      | 104 |

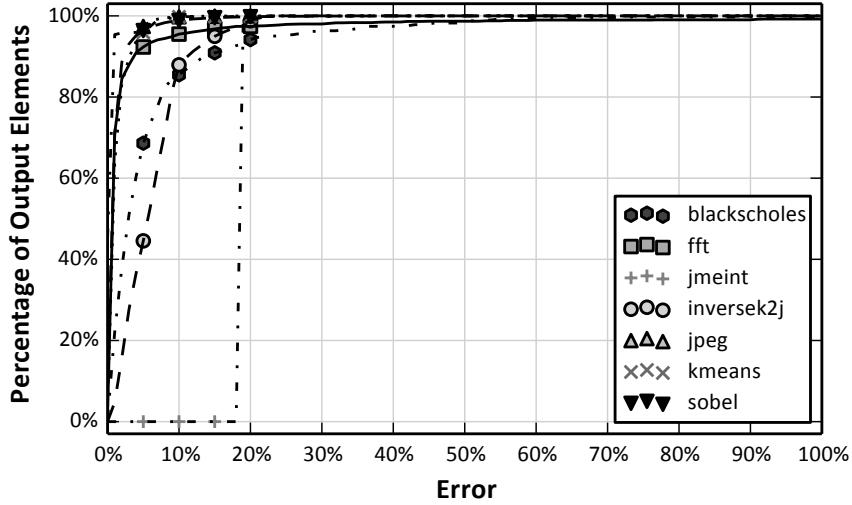

| 5.15 | CDF plot of application output error. A point $(x,y)$ indicates that $y\%$ of the output elements see error $\leq x\%$ [4]. . . . .                                                                                                                                                                                                      | 106 |

# Chapter 1

## Introduction

### 1.1 Problem

For decades, the semiconductor industry enjoyed exponential improvements in microprocessor power and performance with the device scaling of successive technology generations. This phenomenon was enabled by Dennard's scaling principles, proposed in 1974 [27], which state that decreasing circuit dimensions and voltages by a constant factor,  $k$ , and increasing substrate doping by  $k$  results in decreased delay by  $k$  and a decrease in power consumption by  $k^2$ . Consequently, since area is also decreased by  $k^2$ , transistors could be scaled to provide improved performance without significantly worsening power density. However, the Dennard scaling approach broke down with sub-micron technologies, as decreasing threshold voltages and oxide thickness resulted in large leakage currents and power dissipation.

With the end of Dennard scaling, the architecture community shifted focus to multicore designs (leveraging application parallelism) with a combination of less complex or lower-frequency cores to provide performance improvements within a limited power budget. As shown [34], however, even with high levels of parallelism, the multicore approach can not scale to provide the

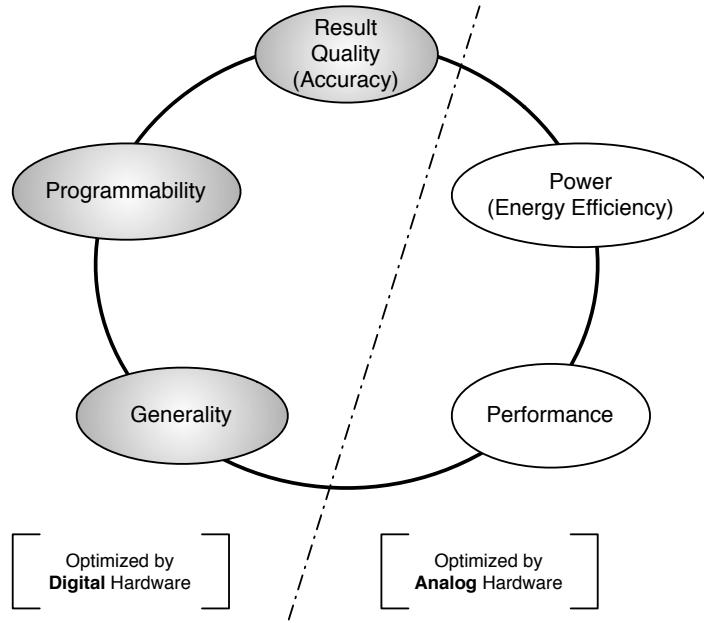

Figure 1.1: Desirable attributes of computation devices.

historical improvements in performance and energy efficiency that have driven the continued advancements in technology scaling. While device scaling provides a larger number of transistors per chip, for a fixed-size chip, a growing percentage of the chip will have to be powered off at any given time due to power constraints; this percentage of dark silicon is expected to reach over 50% at 8 nm [35].

As the multicore approach wanes in its ability to provide performance improvements, the architecture community has focused on special-purpose accelerators to translate the growing number of transistors into gains in performance, though their scope is limited. Accelerators highlight an ‘iron triangle’ consisting of performance, energy, and generality, where designing for any two

aspects sacrifices the third. Accelerators have been proposed to speed-up specific applications or to accelerate code in specific domains, sacrificing generality to reap gains in performance and energy efficiency [21, 83, 101].

Generality, however, is a highly desirable attribute for computer design that has economically driven the industry since the first modern computing machines [31]. (See Chapter 2 for further discussion on the history of computing.) The economic drivers of business determine the desirable attributes of a computing device shown in Figure 1.1: speed, low energy, generality, quality results, and programmability.

## 1.2 Opportunity

Since the advent of modern processing, the attribute of result quality has largely been assumed to be fixed; however, a new class of *approximate* applications have emerged that can tolerate some level of imprecision. Examples of approximation-tolerant applications include those in the areas of machine learning, human-computer interaction, financial analysis, 3D gaming, sensor-data processing, and robotics. For these many applications, accuracy can be sacrificed to gain energy efficiency, performance, and generality, potentially providing a workaround to the iron triangle. Though point solutions exist that express the effect of trading accuracy for those gains [8, 19, 88], the scope of that space is still largely unexplored. The work presented in this thesis aims to investigate this tradeoff space in the context of mixed-signal design, i.e. the combination of analog and digital circuits.

Analog hardware warrants investigation for its potential in the realm of approximate computing since analog circuits traditionally trade accuracy for efficiency. In the analog domain, values are physically represented as voltages and currents. This physical representation can enable fast and efficient computation. For example, multiple values, represented as currents, can be quickly and efficiently summed on a wire. This physical representation, though, also presents challenges due to limited range, as well as inaccuracy due to non-linearity and noise. These limitations have made analog circuits difficult to program and lacking in generality. Figure 1.1 highlights the computing design attributes that favor analog hardware - performance and energy efficiency - and those that favor digital hardware - accuracy, programmability, and generality.

### 1.3 Solutions and Contributions

The work presented in this thesis aims to answer the following questions:

*Can analog circuits be successfully integrated into general-purpose computing to provide performance and energy savings? And, what is required to address the historical analog challenges of inaccuracy, programmability, and a lack of generality, to enable such an approach?*

This thesis work suggests a *neural* approach as a path toward addressing the historical analog challenges of inaccuracy, programmability, and a lack of generality.

**Generality.** Neural networks have been shown to learn complex functions, generating approximate outputs given a set of inputs. In the case of approximate computing, neural networks can address challenges in generality as they can learn arbitrary functions across applications that can tolerate imprecision [37]. Neural networks, therefore, have the opportunity to retain generality, while providing a fixed-function quality to the computation, which addresses the analog implementation challenge of limited signal ranges.

**Accuracy.** Neural models of computing have been shown to be resilient to various types of hardware inaccuracies, as they utilize a learning process to minimize output errors [44, 29, 28].

**Programmability.** The analog challenge of programmability is linked with a general-purpose, von Neumann model of computing. A neural approach adopts a strategy independent of that model, and the clever application of a neural approach at various layers in the computing stack can overcome the analog challenge of programmability.

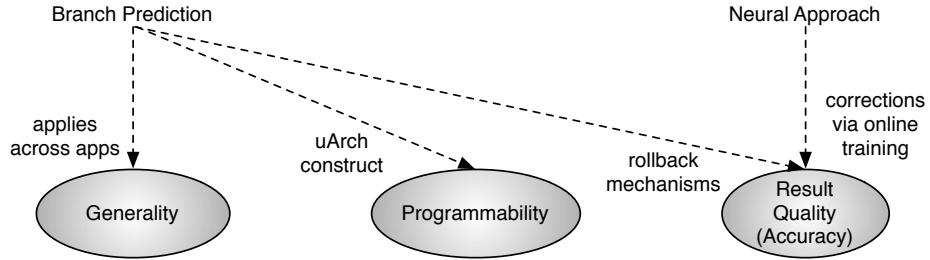

This thesis work investigates the incorporation of analog neural computation to provide gains in efficiency and performance in both microarchitecture-level and application-level approximate computing. Chapter 4 presents an analog neural branch predictor (SNAP), which applies analog neural computation at the microarchitecture level [121, 122]. Figure 1.2 illustrates how this technique addresses the high-level challenges of analog hardware. The branch

Figure 1.2: Neural prediction: addressing analog shortcomings.

predictor is a microarchitecture construct, and, as such, does not require any change to the programming model. Branch prediction applies across applications, which maintains generality. Additionally, an inaccurate prediction is tolerated with the use of roll-back mechanisms to ensure correct program behavior. A neural approach addresses analog circuit inaccuracy by using online training to improve prediction accuracy.

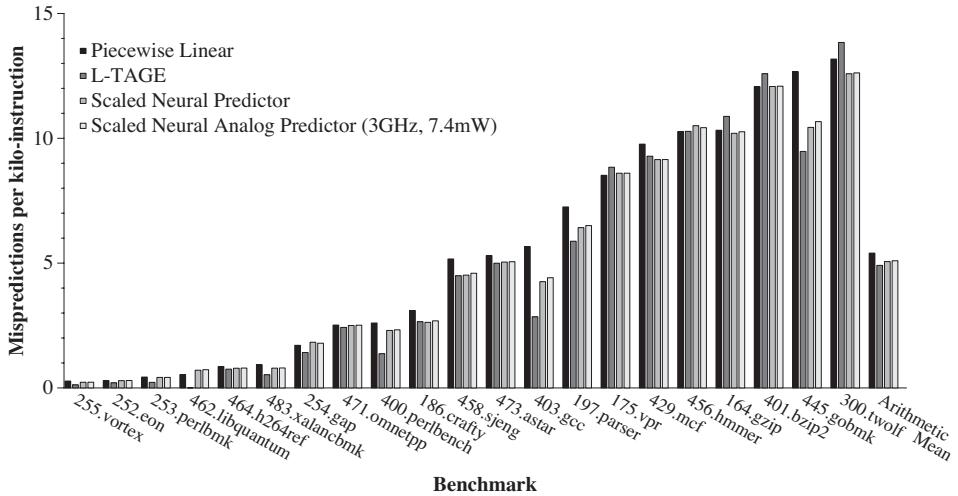

An analog predictor implementation enables a highly-accurate prediction algorithm (Scaled Neural Prediction) that is infeasible to implement in the digital domain as it would require orders of magnitude more power than the analog implementation. We show that despite analog circuit behaviors, such as non-linearity, fast, low-power analog computation enables improvements in prediction accuracy over less-feasible, digital neural predictors (5.18 mispredictions per thousand instructions vs. 5.4 MPKI for the piecewise-linear neural predictor [65]). As compared to a fully-precise, infeasible, digital implementation of the Scaled Neural Prediction algorithm, an analog implementation results in an increase of only 0.12 MPKI. This analog neural prediction

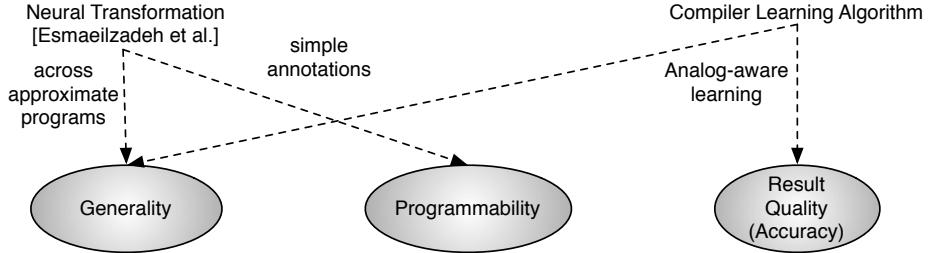

Figure 1.3: Neural acceleration: addressing analog shortcomings.

work opens the door for further advancements in implementing approximation-tolerant microarchitecture tasks with efficient analog hardware. For example, other kinds of predictors, confidence estimators, resource managers, and schedulers that can be mapped to a neural model [84, 60] will benefit from this work.

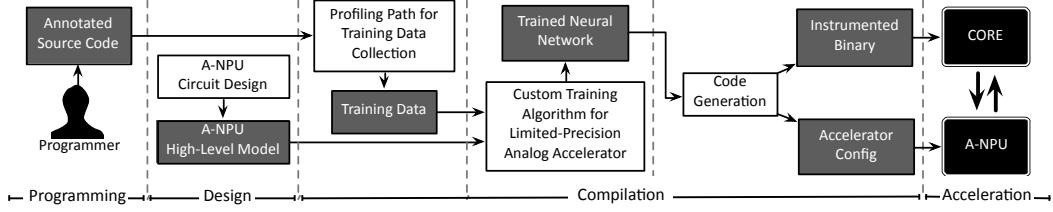

Chapter 5 presents a mixed-signal, neural accelerator (A-NPU) that aims to further investigate the potential for incorporating analog circuits into general-purpose computing by allowing for application-level approximate computing [4]. While an increase in branch prediction accuracy results in application performance and energy improvements, these improvements are limited by the overheads of ensuring precise operation on a von Neumann architecture. The removal of the von Neumann computing model and the addition of analog computation presents the opportunity for improvements in application performance and energy efficiency by orders of magnitude. The A-NPU leverages prior work that outlines a neural approach to transform general-purpose, approximate code regions to a neural network computation that can be accelerated on specialized hardware [38]. As illustrated in Figure 1.3, the leveraged neural transformation addresses the high-level, analog challenges

of programmability and generality, as it requires only simple annotations to identify approximate code regions and can be applied across error-tolerant application domains.

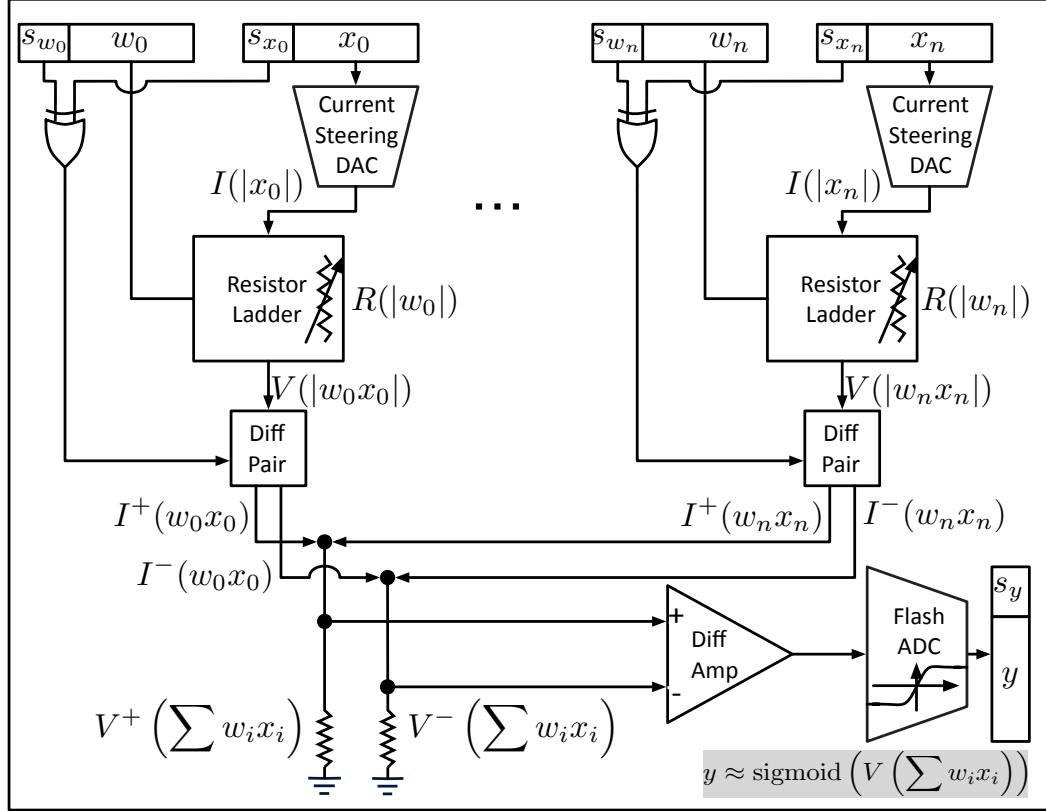

Chapter 5 includes a 45 nm, transistor-level circuit design of the basic computation unit of the A-NPU— an analog neural unit, or ANU. The ANU design demonstrates the effects of analog design-time constraints on the neural model for computation. Specifically, analog range limitations restrict network connectivity by limiting (and fixing) the number of inputs per neuron, restrict the bit widths of inputs, outputs, and weights in the network, and restrict the behavior of the non-linear activation function utilized in the neurons. We show that exposing these analog-imposed limitations to the compiler allows for compile-time techniques that specifically address these limitations and enable the use of analog circuits to improve the performance and energy efficiency of conventionally-written, approximate code.

As compared to an 8-bit digital NPU, the A-NPU achieves 12.1x more energy savings and 3.3x speedup on average for each accelerator invocation. These gains translate to 6.3x energy savings and 3.7x application-level speedup over the original, conventionally-written application run on an aggressive, out-of-order architecture. These gains in speed and energy efficiency come at the expense of accuracy; but, with the proposed compilation support, application error levels remain below 10% despite analog-signal range limitations.

# Chapter 2

## Context

This chapter attempts to set the context for this dissertation work by giving a brief history of analog computing followed by sections on the design space of neural networks and approximate computing. More details on related work can be found in Chapter 6.

### 2.1 A Brief History of Analog Computing

The word *analog*, which we use today to describe a particular class of computing, stems from the 15th-century word *analogy*, meaning *a comparison of two things based on their being alike in some way* [16]. As such, the first analog computers were combinations of physical devices designed to model some physical phenomenon based on their similar behavior. Such mechanical aids for calculation have a long history, beginning with computation systems for navigation and astronomy. The Antikythera mechanism, for example, dated 87 B.C., was a system of various-sized gears for predicting astronomical positions [52]. In 1872, Sir William Thomson developed a tide-predicting machine that used a system of pulleys and chains to model individual tidal harmonics and combine them to predict tide levels for easier navigation [127]. Wheel and

disc mechanisms, first used in planimeters to analyze maps for land taxation and allocation purposes [16, 10], were designed to perform integration and later formed the basis of mechanical differential analyzers [13].

Advancements in electronic technology, necessitated by World War II, gave rise to electronic analog computers, where mechanical integrators were replaced with capacitor-based circuits. These electronic analog computers were important in the fields of science and technology, with their major applications being differential equation solving, modeling complex systems, and simulating control systems [16]. Though electronic, these machines were still not general purpose.

In 1936, Alan Turing demonstrated the computation power of algorithm-based, discrete value manipulation, engendering a new abstraction for thinking about the design of computational devices [130]. Turing’s abstraction presented an opportunity for generality, and the move to digital computation in the 1940s [12, 31] was linked with a goal of providing flexibility and increasing application coverage. In the description of the Electronic Numerical Integrator and Computer (ENIAC), Eckert and Mauchly wrote [31]:

*Analogy computing devices vary greatly in flexibility. These machines are somewhat specialized and restricted in application. A digital machine which can be directed to carry out any of the common arithmetic operations in any desired sequence on any given set of numbers has all the generality and flexibility required for any practical purpose. (It cannot compute the exact value of pi, but it can compute in a finite number of steps any desired approximation of*

*pi.) Therefore, it can, for example, compute to any specified definite approximation the solutions of non-linear partial differential equations which are not obtainable from any existing analogy computer. This attainment is one of the important objects of our invention.*

The move away from analogy computing and toward a general-purpose, computing abstraction favored repeatable, digital design. The ENIAC, a digital electronic computer with vacuum tubes that acted as switches, still required significant time in physical re-wiring to run various programs. With contributions from von Neumann that included the idea of stored-program control, the ENIAC's successor, the EDVAC, represents a truly flexible, general-purpose machine [132]. The von Neumann model, in addition to the development of transistors [119], made computers assets for business, not just science and technology endeavors, economically driving the computing industry in the direction of digital, von Neumann designs.

For decades, device scaling enabled exponential gains in performance within a fixed power budget, while maintaining generality, programmability, and quality results within a digital, von Neumann model of computing. However, scaling limitations at sub-micron technologies halted this trend, as power density increased due to leakage currents. Now the industry must optimize energy efficiency to deliver increased performance, and, as such, the assumptions of the modern computing era must be reconsidered – in particular, that of a digital, von Neumann model of computing.

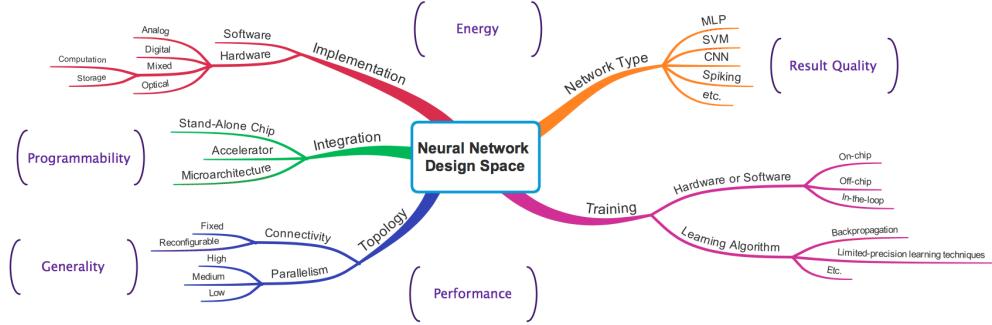

Figure 2.1: Neural network design space. As computing tools, neural-network designs trade off the desirable attributes of a computing device (shown in Figure 1.1): performance, energy efficiency, result quality (accuracy), programmability, and generality.

## 2.2 Neural Networks for Computing

Artificial neural networks offer an abstraction for computation that deviates from the traditional model. These networks can act as arbitrary function approximators that *learn* how to solve various problems through observation. And, as suggested, these networks are inherently approximate. A significant amount of work in artificial neural networks has resulted in various network types and learning techniques, which can be realized in hardware or software. Figure 2.1 illustrates the space of neural network design, and as a computing tool, the neural network design space trades the attributes shown in Figure 1.1. The choice of network type or network topology, for example, can affect the learning ability of the network (result quality) as well as the range of applications that can utilize it to achieve high quality results (generality). The choice of implementation can affect result quality as well as performance and energy

efficiency.

Hardware implementations vary with these design choices depending on their overarching goal. Neural network hardware has been designed with the goals of supporting biological research [62, 45], accelerating specific applications [41, 18], or solving more general-purpose problems in classification [126] and regression [37]. For example, the goal of accelerating biological research may favor a highly-parallel, spiking neuron implementation.

Since the work presented in this thesis aims to achieve improvements in performance and energy efficiency, we choose analog circuits to perform computation; storage resides in the digital domain for easy integration, and both the neural predictor and neural accelerator are mixed-signal designs. The neural branch predictor presented in Chapter 4 sits on the limb of microarchitectural integration [67, 84, 60]. Chapter 5 presents a reconfigurable, mixed-signal, neural accelerator that targets general-purpose regression tasks, where compile-time learning techniques are utilized to compensate for analog non-idealities. For the sake of generality, this accelerator implements a multi-layered perceptron (MLP) network, since MLP networks have been shown to produce quality results over a variety of tasks [20]. The leveraged prior work on neural transformation [37] and the mixed-signal microarchitecture presented in Chapter 5 allow for tight integration with a general-purpose CPU and the acceleration of approximation-tolerant code, while maintaining programmability.

Figure 2.2: Research areas in approximate computing.

### 2.3 Approximate Computing

There is a quickly growing body of work in the area of approximate computing, which spans the computing stack, as shown in Figure 2.2. Architecture support for approximate computing covers both traditional architectures [36] as well as accelerators, and both digital and analog approximate computation blocks have been proposed [30, 82, 75]. Analog functional blocks offer potential performance improvements and energy savings, however, they suffer from difficult integration with high-speed, general-purpose microprocessors

due to challenges such as restricted signal ranges, conversion requirements, and storage technologies. Accelerator architectures for approximate computing can reduce programmability, as some require the use of new programming models [9, 98], and generality, depending on which application, or class of applications is targeted [21, 81].

The analog neural branch predictor presented in Chapter 4 represents the utilization of analog circuits for microarchitecture-level approximate computing. The mixed-signal, neural accelerator presented in Chapter 5 targets an application-level opportunity for approximate computing; it builds on the prior work of a compile-time approximation transformation [37] but additionally adds approximation at the circuit level through the use of analog hardware. We show that exposing analog circuit limitations to the compiler allows for further compile-time optimizations that compensate for inaccuracies due to an analog approach.

## Chapter 3

# Challenges of an Analog Approach to Neural Computation

This chapter gives a review of neural network computation and highlights the potential of an analog implementation. It outlines the challenges of computing in the analog domain, as well as the effects of those limitations on neural computation, and discusses high-level solutions. Additionally, it differentiates between two classes of tasks typically targeted by neural networks, classification and regression, and describes the implications of the two classes on analog neural hardware.

### 3.1 Review of Neural Network Computation

The neural predictor in Chapter 4 and neural accelerator in Chapter 5 both utilize a perceptron-based neural network model. The perceptron was developed as a binary classifier, which takes in a set of rational-valued inputs,  $x_i$ , and produces a binary output that is a function of those inputs,  $f(x_i)$ . The perceptron *learns* a set of weights,  $w_i$ , through training. To produce an output, the perceptron, or neuron, acts as a computation unit that performs a weighted sum of the input values,  $\sum_i x_i w_i$ . After the summation stage, the

neuron applies an activation function, such as a threshold function, where, if the resulting weighted sum is positive, the neuron output is 1, otherwise the neuron output is 0.

These neurons can be connected together to form a multilayer-perceptron (MLP) network, where the neuron outputs in one layer feed into neuron inputs in the following layer. These networks have been shown to solve regression problems (producing a rational-valued output) in addition to classification problems [55]. MLP networks typically utilize, differentiable, non-linear activation functions, such as the *sigmoid* function, rather than the more simplistic threshold function utilized in a single perceptron.

**Classification vs. Regression Tasks.** The MLP neural model has been applied to two different types of learning tasks: (1) classification and (2) regression (function approximation). Classification aims to answer the question – to which set of categories does a new observation (input) belong? Examples of classification tasks include character recognition based on a set pixel values or predicting the presence of cancer based on a set of patient diagnostics. Regression, which is also referred to as function approximation, on the other hand, aims to map inputs to a continuous target function. One simple example of a regression problem is the task of producing the output of the *sine* function given an input value between 0 and  $2\pi$ .

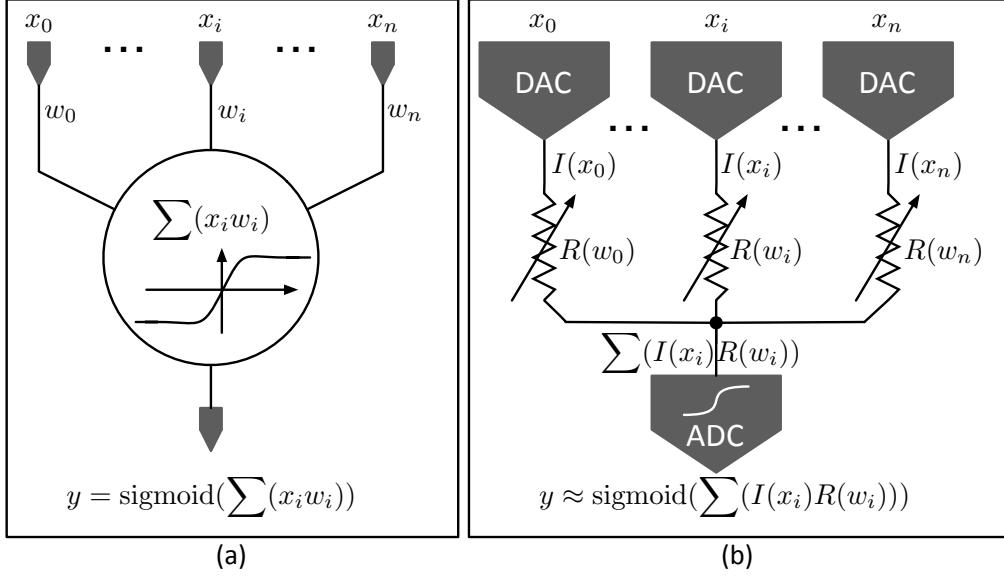

**Potential of Analog Computation.** The neuron computation is characterized by a potentially expensive dot-product operation as well as an activation function. Analog circuits present the opportunity for efficient parallel computation. For example, current-steering techniques can efficiently perform highly-parallel summation by simply steering multiple analog currents to a single wire in accordance with Kirchhoff’s current law [71, 114]. Additionally, transistor physics support the possibility of efficiently implementing a non-linear activation function [85], though limited signal ranges in the analog domain present some practical challenges.

## 3.2 Challenges of an Analog Approach

The three major challenges of an analog approach are limited signal ranges, non-idealities (such as process variation), and noise. These challenges can also be categorized by timeline – design time for limited ranges, manufacture time for non-idealities, and run time for noise. In addition to a discussion of the major challenges of analog hardware and their effect on neural computation, this section discusses the placement of the analog-digital boundary, which is relevant for mixed-signal, neural implementations.

### 3.2.1 Design-Time Signal-Range Restrictions

In the analog domain, values are represented physically as voltages or currents on one or more wires, and the form of physical value representation affects the power, performance, and accuracy of the various computation oper-

ations. For example, addition can be performed extremely fast using currents, whereas a multiply operation executes more efficiently using voltages [1]. Similarly, some analog circuit blocks can only realize efficient computation by restricting the range of the input values. For example, an analog circuit might be able to efficiently compute a sigmoid function by utilizing the physics of transistor behavior, however, the input to that function must be within a specified range and of a specific representation type to produce the desired output. Additionally, such a computation block will produce an output voltage or current within a restricted range. Conversion between representation types and signal scaling are unique challenges in the analog domain.

Data density is another challenge that stems from a physical representation. For example, the range of any voltage signal is fixed by the supply voltage. As such, the same fixed signal range can represent a small (low-precision) or large (high-precision) amount of information. Packing high-precision information within a fixed range exacerbates challenges due to range restrictions.

For neural computation, analog range restrictions can affect the ideal network topology, activation function, and practical bit width of computation, all of which can decrease the learning and approximation capacity of the network.

**Effect on topology.** Limited signal ranges affect the flexibility of the topology connections as well as the degree of parallelism. Since analog circuits are designed to operate well within a certain range, and that range typically must

Figure 3.1: Sigmoid function with varying activation steepness ( $\alpha$ ). Activation steepness determines the numerical range of input values that translate to output values between 0 and 1.

be fully utilized to maintain accuracy, an analog implementation favors a pre-determined number of inputs to a neuron for accurate computation. Data density limits this number of inputs, and therefore, the size of the network and its connectivity.

**Effect on activation function.** In the analog domain, limited signal ranges and data density pose challenges for implementing non-trivial activation functions, such as the sigmoid function. The sigmoid function can be described by  $f(x) = \frac{1}{1+e^{-x\alpha}}$ , where  $\alpha$ , the *activation steepness*, defines the slope of the near-linear portion of the function. Figure 3.1 shows a sigmoid function with various activation steepnesses. As shown, as activation steepness increases, the numerical input range (on the x-axis) that maps to output values

(y-axis) between saturation levels decreases. As such, increasing activation steepness increases pressure on the fixed analog range, as a smaller physical signal range must be translated to a non-saturated output. An analog implementation, therefore, favors shallow activation functions; neural networks, however, require the non-linear activation function for learning, and decreasing the activation steepness can result in a decreased capacity of the network to learn and produce high-quality outputs. Although prior work has shown the implementation of sigmoid functions with analog circuits [56], there is a challenge in scaling the input signal to match a specified sigmoid steepness.

**Effect on bit width.** For a neural network that requires integration with a high-performance microprocessor, the network inputs and outputs must reside in the digital domain. Just as limited signal ranges restrict the number of inputs per neuron, they also limit the bit width of input values and weight values, as increasing the number of bits increases data density. Additionally, analog-to-digital converters (ADCs) can not distinguish between small variations in signal level, and, as such, they place requirements on the minimum size of the signal range between quantization levels. This restriction plus a limited signal range at the input to the ADC restricts the number of output bits. Like topology and activation function restrictions, limited bit-width value representations can limit the ability of the network to learn and produce useful outputs.

### 3.2.2 Manufacture-Time Non-Idealities

Analog circuits suffer from process variation and mismatch between device components on a single die, as well as across dies, and these non-idealities can lead to inaccuracies in computation. For example, a current signal representing a particular input value might be slightly larger on one die than on another due to process variation. Additionally, analog circuits often present a challenge of non-linearity. For example, a digital-to-analog converter (DAC) converts a digital value to an analog one, however, this conversion is not exactly linear.

**Training to address manufacture-time non-idealities.** Because neural networks *learn* to generate quality results through a training process that minimizes error, the use of chip-in-the-loop training, in which a portion of the training takes place on real hardware, can train around manufacture time non-idealities, such as non-linearity and process variation [44, 29, 28].

### 3.2.3 Run-Time Noise

In addition to device mismatch, analog circuits are subject to run-time noise. Noise refers to inaccuracy due to stochastic events such as nearby digital switching and temperature fluctuations. Noise results in decreased result quality.

**Circuit design to mitigate the effects of noise.** Traditional techniques, such as guard rings, can be used to mitigate the effects of substrate noise due to digital switching [123]. A guard ring separates analog and digital circuits and creates a large capacitance that provides noise currents with a low-impedance path to ground. General design practices leave margins to allow for some amount of noise, such as quantization margins for analog-to-digital conversion. Also, certain circuit design blocks are less susceptible to noise than others. Differential circuit designs mitigate non-ideal, analog-signal behavior due to noise by computing with a differential between two nearby signals that change similarly in the presence of noise.

### 3.2.4 Analog-Digital Boundaries

A mixed-signal approach, with conversions to the digital domain, can ease the challenges of an analog approach, though the placement of analog-digital boundaries exhibit tradeoffs in power, performance, and accuracy. One challenge with a mixed-signal approach is to determine the optimal placement of these boundaries to achieve the computational goals of the network. Neural hardware designed for biological research, for example, might input data directly into the analog domain based on sensor data. Alternatively, a neural network designed for integration with a high-performance microprocessor would require digital inputs and outputs to the network. Internal values could reside in either the digital or the analog domain.

A completely analog implementation with fixed-wire connections be-

tween neurons maximizes performance and energy efficiency; however, fixed connections effectively fix the network topology and limit the generality of the neural network. Storing intermediate values can increase generality, however, analog storage does not lend itself to satisfying high-performance requirements. Additionally, the analog domain suffers from challenges in accurately replicating and buffering signals for routing signals between neurons. Conversion to the digital domain can increase network flexibility and limit signal susceptibility to noise; however, conversions between the analog and digital domains are expensive in terms of energy and introduce inaccuracy due to quantization. As such, frequent conversions limit the benefit of analog computation.

### 3.3 Analog Challenges in Classification and Regression

Classification tasks, as compared to regression tasks, place different requirements on a multilayer-perceptron network. One example of a classification task is determining the presence or absence of cancer, and one of regression (or function approximation) is that of approximating the output of the *sine* function. Classification tasks target binary outputs, where regression tasks target multi-bit (and ideally continuous) outputs. Additionally, even for hidden-layer neurons, a trained classification network is typically characterized by extreme neuron outputs (saturated to 0 or 1), where a network trained to perform a regression task often utilizes hidden-layer neuron outputs in the linear portion of the activation function (values between 0 and 1).

Saturated hidden-layer outputs and the requirement of only single-bit

network outputs (which can simply be determined by a threshold function implemented as a single comparator) make classification tasks more robust in the presence of inaccuracies and the challenges of an analog implementation [32]. For example, if the learned network weights are saturated to fit within a specified number of bits, this modification is less likely to result in a change in a neuron output, as the output likely resides in one of the extremes of the activation function. However, for regression tasks that utilize neuron outputs between the extremes, modifying weight values to fit within a specified number of bits is more likely to change the output value of a neuron. Manufacture-time non-idealities and noise result in similar behavior, where small variations in the neuron inputs and weights are less likely to result in changes at a neuron output in the case of classification. As the number of output bits required to perform a regression task increases (which is problem dependent), the challenges and resulting inaccuracies due to an analog implementation become more pronounced and can result in detrimental decreases in network accuracy.

Though multilayer perceptrons have been successfully applied to problems in function approximation [55], this work often assumes full-precision computation. The literature related to *hardware* neural network implementations almost exclusively evaluates classification tasks, which are more robust in the presence of analog implementation challenges [32, 79, 90, 124, 112]. The ability to solve regression problems, however, is highly desirable for upholding generality, as it increases the scope of approximation-tolerant applications that can utilize the hardware.

The neural predictor in Chapter 4 addresses the simpler task of classification; it classifies a branch as taken or not taken. The neural accelerator presented in Chapter 5, however, targets the more challenging task of regression to increase the scope of applications that can benefit from the neural acceleration. The techniques presented in Chapter 5 are necessary steps toward enabling a mixed-signal, neural accelerator capable of solving problems in regression.

# Chapter 4

## Analog Neural Prediction

Certain microarchitecture-level tasks provide the opportunity to exploit approximate computing and trade precise and/or repeatable computation for more energy-efficient computation. These microarchitectural tasks include those that aim to improve processor energy efficiency or performance, for example, but do not impact program correctness. Examples include speculation constructs for increasing instruction-level parallelism, such as control flow and data-dependence prediction, thread scheduling in throughput architectures, and the allocation of shared resources, including power, caches, and memory bandwidth in heterogenous and multicore architectures. In particular, those soft microarchitecture tasks that can be mapped to a neural model can benefit from efficient, mixed-signal computing [84, 60, 73]. This chapter investigates the use of approximate, mixed-signal computation in the microarchitectural task of branch prediction.

Branch prediction offers a unique opportunity for the application of analog circuits to general-purpose computing, as it addresses the historical analog shortcomings of programmability, generality, and accuracy. Branch predictors predict program control flow based on a program’s branch history.

As a microarchitectural construct, branch prediction requires no change in the programming model. This same construct applies across applications, which maintains general applicability. Additionally, roll-back mechanisms allow for the correction of mispredicted branches, which produces accurate program execution in the presence of mispredictions, and, in the case of approximate computing, in the presence of inaccuracies in generating a prediction.

In particular, *neural* branch prediction offers further opportunities for the successful integration of analog circuits. Neural branch prediction is characterized by an expensive dot-product operation, which can be performed efficiently in the analog domain. Additionally, online training has the potential to correct for analog non-idealities, such as process variation, as the training continually adjusts a weights vector toward producing better predictions.

This chapter presents the design of an analog neural branch predictor, called the Scaled Neural Analog Predictor (SNAP). This efficient analog implementation allows for two improvements over previous digital neural predictors, which results in higher prediction accuracy, despite approximate analog computation.

## 4.1 Background on Neural Predictors

This background section describes the computation and training of the first neural predictor, the perceptron predictor [67, 68]. It also highlights the path-based improvements to the original perceptron predictor that improve neural predictor accuracy.

#### 4.1.1 The Perceptron Predictor

**Computation and Prediction:** The basic perceptron predictor [67, 68] consists of a single perceptron, or neuron. This neuron takes as input a binary global history vector that contains the directions of the most recent program branches. Each branch history value acts as a neuron input. A hash of the branch PC selects the appropriate signed weights vector from a table of weights vectors. The neuron computes a dot-product of the inputs and weights and utilizes a threshold activation function that classifies the current branch as *taken* or *not taken*. If the weighted sum is greater than 0, the neuron predicts a taken branch, and if it is less than 0, the neuron predicts a not taken branch.

**Training:** The branch history can be interpreted as a vector of  $-1s$  and  $1s$ , where  $-1$  corresponds to a *not taken* branch, and  $1$  corresponds to a *taken* branch. The sign of each weight indicates a positive or negative correlation between the corresponding bit in the history register and the branch to be predicted; For example, if a bit in the history register contains a  $-1$ , or a *not taken* branch, a positive weight value signifies a positive correlation between the *nottaken* branch, and the direction of the current branch, which suggests that the current branch will also be *not taken*. The magnitude indicates the strength of the correlation.

The perceptron is trained during program execution when there is a misprediction or when the magnitude of the perceptron output is below some threshold value. Upon training, each weight is incremented if the predicted

branch has the same outcome as the corresponding history bit (a positive correlation) and decremented otherwise (a negative correlation).

#### 4.1.2 Improvements to the Perceptron Predictor

Path-based neural predictors improved upon the original perceptron predictor by using path information with ahead-pipelining to reduce latency and increase accuracy [64, 65]. With path-based predictors, the weighted sum is performed in steps ahead of time such that to make a prediction, the neuron only requires a final addition operation. This ahead-pipelining scheme, however, does not fully capitalize on the potential prediction accuracy that could result from efficient parallel computation, since the weights used in the computation were not indexed with the PC of the actual predicting branch.

## 4.2 Analog-Enabled Neural Prediction Algorithm

The analog-enabled Scaled Neural Prediction (SNP) algorithm incorporates two major improvements over previous neural predictors, made feasible by the power and latency reductions of an analog implementation: (1) the elimination of ahead pipelining and (2) the scaling of individual weights by predetermined coefficients, based on their history position, both of which improve predictor accuracy.

**Removal of Ahead Pipelining:** The original path-based neural predictor is ahead-pipelined, i.e., it begins computing the prediction for a branch well

Figure 4.1: Weight position and branch outcome correlation [121]

before that branch is fetched by using path information to index the table of weights. This scheme reduces the effective latency of a prediction. However, some accuracy is lost because, without knowing which branch it is predicting, the predictor may use the same weight to compute predictions for many different branches. That is, the weights used in the computation were not indexed with the PC of the actual predicting branch. Because an analog design can sum all of the weights quickly when the actual branch is being predicted, ahead-pipelining is unnecessary and the predictor can use the branch PC when choosing the weights to sum. Thus, accuracy is improved.

**Scaling Weights by Coefficients:** The weights in a perceptron vector represent the contribution of each branch in a given history to predictability, but each branch does not contribute equally; more recent weights tend to have a stronger correlation with branch outcomes [121]. Figure 4.1 quantifies this non-uniform correlation for a neural predictor with a history length of 128. The  $x$ -axis represents the position of a weight in the history ( $x = 0$  represents the bias weight). The  $y$ -axis gives the average correlation coefficient (Pearson's  $r$ ) between actual branch outcome and the prediction obtained by using only the weight in position  $x$ . The first weights have a much stronger correlation with branch outcome than the later weights. The function  $f(i)$ , fitted to the correlation coefficients, is used to generate scaling coefficients for the various weight positions; By multiplying weights with coefficients proportional to their correlation, the predictor achieves higher accuracy. The analog design achieves the weight scaling efficiently by varying transistor sizes, whereas a digital implementation would need to perform a number of power- and latency-prohibitive multiplications for each prediction.

Figure 4.2 shows a high-level diagram of the prediction algorithm and data path.

**Predictor Parameters:** The two key parameters of the predictor are  $h$ , the length of the vector with which the dot product is computed, and  $r$ , the number of rows in each weights table. In this design,  $h = 128$  and  $r = 256, 512$ , or 2048. Other inputs to the predictor are  $A$ , a vector of the low-order bit

Figure 4.2: Prediction data path [121]

of each of the past  $h$  branch addresses ( $A$  is effectively a path vector), and  $H$ , the global branch history register. This design uses a history register  $H$  of 40 bits. The history vector of  $h = 128$  bits is expanded from the 40 bits of  $H$ , as the use of redundant history has been shown to improve prediction accuracy [115]. Weights are stored as 7-bit signed integers.

**Computation and Prediction:** The computation required to produce a prediction includes multiplying the selected weights vector by  $f(i)$  and then computing the dot-product between the resulting scaled weights vector and the expanded history vector. The size of  $h$ , 128 in this case, determines the

number of multiply and add operations required to compute a prediction. 0 signifies a *taken* prediction, and a dot-product result less than 0 signifies a *not taken* prediction.

**Predictor Updates and Training:** Updating the predictor consists of three phases, some of which can occur in parallel.

- **Updating histories.** When the outcome of a branch becomes known, it is shifted into  $H$ . The lowest-order bit of the branch’s address is shifted into  $A$ . A high-accuracy implementation must keep speculative versions of  $H$  and  $A$  that are restored on a misprediction.

- **Training the predictor.** At commit, if the prediction was incorrect, or if the magnitude of the predictor output was under a set threshold, then the predictor invokes its training algorithm. As in previous neural predictors, the weights responsible for the output are incremented if the corresponding history outcome matches the current branch outcome, and decremented otherwise. The weights use saturating arithmetic.

- **Updating the training threshold.** An adaptive threshold training algorithm dynamically adjusts the threshold at which training will be invoked for a correct prediction. This algorithm is the same as the one used for O-GEHL [116]: the threshold is increased after a certain number of incorrect predictions, and decreased after a certain number of correct predictions whose outputs were not as large as the current threshold.

More details on the prediction algorithm and predictor tuning parameters can be found in the original publication [121]. When evaluated with the Championship Branch Prediction competition (CBP-2) infrastructure and a 32KB hardware budget for predictor state [66], the SNP predictor achieves 5.06 mispredictions per kilo-instruction (MPKI) as compared to 5.40 MPKI for the piecewise linear (PWL) predictor [65], a high-accuracy neural predictor that also has a high implementation cost. Although highly accurate, the SNP predictor is not feasible to implement due to the large number (128) of multiply-add operations. At 3GHz and 45nm, a digital implementation would consume over 2 watts of power in the computation step, where an analog implementation can perform the same computation while consuming under 10 milliwatts (demonstrating potential power savings over 200x for an analog approach) [46].

### 4.3 Scaled Neural Analog Predictor

The goal of the Scaled Neural Analog Predictor (SNAP) circuit, shown in Figure 4.3, is to classify a branch as *taken* or *not taken*. The circuit acts as a neural computation unit, where the inputs are a binary history vector of length 128 and the weights are a selected vector (of comparable length) of signed integers with 6-bit magnitudes. In addition to the traditional dot-product computation between the inputs and weights, this computation unit first scales the weights vector by a predetermined vector of coefficients, which allows for more accurate branch predictions as described in Section 4.2. A simple threshold

Figure 4.3: Top-level diagram of a Scaled Neural Analog Predictor

activation function produces a one-bit, *taken* or *not taken*, prediction. Additionally, the circuit produces two signals to identify whether training should occur, which depends on the result of the weighted sum in comparison to a threshold value. The SNAP circuit uses analog current-steering and summation techniques to perform efficient parallel computation, since currents can be summed quickly on a wire by Kirchhoff’s current law (KCL) [71, 114].

**Analog-Digital Boundaries:** This design places input and weight storage in the digital domain and computation in the analog domain; the final prediction and training outputs of the circuit are also latched as binary, digital values.

**Converting Weights to the Analog Domain:** Simple, high-speed current steering digital-to-analog converters (DACs) are used to convert digital weights to analog signals (currents) that can be combined efficiently [1, 69]. Each DAC uses one transistor per bit, sizing the width of the transistor to account for the magnitude represented by the corresponding bit position. In the DAC shown in Figure 4.3,  $W_0$  through  $W_5$  represent these transistor widths. The transistors are configured as a current mirror, where a unit current,  $I_u$ , is “mirrored” through each transistor approximately proportional to  $W$ . For example, for a 4-bit, base-2 digital magnitude, the DAC transistor widths would be set to 1, 2, 4, and 8 and draw currents  $I_u$ ,  $2I_u$ ,  $4I_u$ , and  $8I_u$ , respectively.

This approach supports near-linear digital-to-analog conversion. A

Table 4.1: Excerpts from the list of DAC transistor widths [121]

| Col. #   | Transistor Widths |       |       |       |       |       |

|----------|-------------------|-------|-------|-------|-------|-------|

|          | Bit 0             | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 |

| 0 (bias) | 1                 | 2     | 4     | 8     | 16    | 32    |

| 1        | 1                 | 2     | 4     | 8     | 15    | 30    |

| 2        | 1                 | 2     | 3     | 7     | 13    | 26    |

| 3        | 1                 | 1     | 3     | 5     | 11    | 21    |

| 10       | -                 | 1     | 2     | 3     | 7     | 14    |

| 20       | -                 | 1     | 1     | 2     | 5     | 9     |

| 128      | -                 | 1     | 1     | 2     | 4     | 8     |

switch is used to steer each transistor current according to its corresponding weight bit, where a weight bit of 1 steers the current to the *magnitude line* and a weight bit of 0 steers it to ground. In the example above, if the digital magnitude to be converted is 5, or 0101, currents  $I_u$  and  $4I_u$  would be steered to the magnitude line, where  $2I_u$  and  $8I_u$  would be steered to ground. By the properties of Kirchhoff's current law (KCL), the magnitude line contains the sum of the currents whose weights bits are 1 ( $5I_u$  in the example) and thus approximates the digitally stored weight.

**Scaling Weights by Coefficients:** To achieve the effect of multiplying weights by coefficients, non-traditional DAC transistor widths are chosen based on the fitted inverse linear curve,  $f(i)$ , mentioned in Section 4.2. As weight position increases and correlation with current branch outcome decreases, DAC transistor widths are scaled down, reducing the amount of current that a weight contributes to the magnitude line. For example, rather than using traditional DAC widths to convert a digital base-2 value to an analog value (1, 2, 4, 8,

16, and 32), a weight in position 3 has DAC transistor widths of 1, 1, 3, 5, 11 and 21, while a weight in position 128 has widths 0, 1, 1, 2, 4, and 8. Table 4.1 shows excerpts of selected DAC transistor widths. Transistor widths are limited to 32, and this technique actually reduces power consumption by drawing less current than would be drawn by traditionally-sized DACs. Where the multiplication operation would increase power in a digital design, it serves to decrease power in an analog one.

**Computing the Dot-Product of Inputs and Scaled Weights:** The scaled magnitude value is then steered to a *positive line* or *negative line* based on the XOR of the sign bit for that weight and the appropriate history bit, effectively multiplying the signed weight value by the history bit. The positive and negative lines are shared across all weights, and again by KCL, all positive values are added, and all negative values are added.

The currents on the positive line and the negative line are split roughly equally by three transistors to allow for three circuit outputs: a one-bit prediction and two bits that are used to determine whether training should occur. Splitting the current, rather than duplicating it through additional current mirrors, maintains the relative relationship of positive and negative weights without increasing total current draw, thereby avoiding an increase in power consumption. The currents from the splitters pass through resistors, creating voltage signals that are used as comparator inputs.

**Threshold Activation Function:** A comparator performs the threshold activation function by comparing a voltage associated with the magnitude of the positive weights to one associated with the magnitude of the negative weights. It outputs a 1, or a taken prediction, if the voltage corresponding to the positive line outweighs the negative line and a 0, or not-taken prediction, otherwise.

The comparator also functions as a one-bit, analog-to-digital converter (ADC) that uses positive feedback to regenerate the analog signal into a digital one. A track-and-latch comparator design [1, 69] was chosen based on its high speed and simplicity.

**Training:** Training should occur if the prediction was incorrect or if the magnitude of the predictor output is less than the threshold value. Rather than actually computing the difference between the positive and negative lines to determine the magnitude of the predictor output (which would require more complex circuitry), and then comparing that magnitude to the threshold value, the circuit instead latches two additional signals, based on comparisons, that will be used when the branch is resolved to indicate whether training should occur ( $T$  and  $N$  in Figure 4.3). If  $C$  is the direction of the branch on commit, and  $P$  is the prediction, the following logic formula indicates training:

$$(C \oplus P) + P\bar{T} + \bar{P}N$$

$C \oplus P$  indicates an incorrect prediction. To determine if the absolute difference between the positive and negative lines is less than the threshold

value, the absolute value comparison is split into two separate cases: one case for the positive weights being larger than the negative weights ( $P\bar{T}$ ) and the other for the negative weights being larger than the positive ones ( $\bar{P}N$ ).  $T$  is the relevant training bit if the prediction is *taken* ( $P = 1$ ), and  $N$  is the relevant training bit if the prediction is *not taken* ( $P = 0$ ).

If the prediction is *taken*, then the positive line outweighs the negative line. To determine whether this occurs by an amount less than or greater than the threshold value, the threshold value is added to the negative line to produce the comparison output  $T$ . If the prediction  $P$  is 1 (*taken*) and  $T$  is 0, which means the negative line with the threshold value added is larger than the positive line, then the difference between the positive and negative weights is less than the threshold value and the predictor should train. Similarly, to produce  $N$ , the threshold value is added to the current on the positive line. If the prediction  $P$  is 0 (*not taken*) and  $N$  is 1, which means the positive line with the threshold value added is larger than the negative line, then the difference between the negative and positive weights is less than the threshold value and the predictor should train. Instead of waiting for the prediction output  $P$  to be produced, which would increase the total circuit delay, all three comparisons are done in parallel.

#### 4.4 Addressing Analog Challenges

This section describes how the SNAP predictor design addresses the challenges of an analog approach to neural computation (discussed in Chap-

ter 3).

**Design-Time Signal-Range Restrictions.** Although the neural branch predictor structure applies generally across applications, it aims to solve a single problem; that is, it aims to predict the outcome of a branch based on branch history information. This shared goal (across applications) allows for a fixed neural topology that can be easily implemented in the analog domain, while maintaining the computing goal of generality. Predetermined scaling coefficients and a predetermined history length allow for known analog signal ranges. Because the predictor uses a mathematically simplistic threshold activation function that simply requires a comparison, data density and limited signal range at the activation function input do not significantly affect prediction accuracy. As branch prediction is a classification task that requires only a single-bit output, output bit width is not affected by limited analog signal ranges.