<u>Cache Models</u> <u>and</u> <u>Program Transformations</u>

> Keshav Pingali University of Texas at Austin

### Memory wall problem

- · Optimization focus so far:

- reducing the amount of computation

- (eg) constant folding, common sub-expression elimination, ...

- On modern machines, most programs that access a lot of data are memory bound

- latency of DRAM access is roughly 100-1000 cycles

- Caches can reduce effective latency of memory accesses

- but programs may need to be rewritten to take full advantage of caches

# Cache abstractions

- · Real caches are very complex

- Science is all about tractable and useful abstractions (models) of complex phenomena - models are usually approximations

- · Can we come up with cache abstractions that are both tractable and useful?

· Focus:

- two-level memory model: cache + memory

- we will define these more precisely in the next slide.

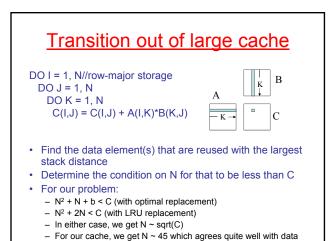

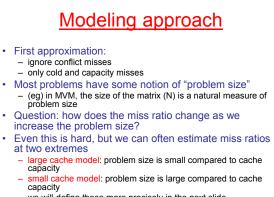

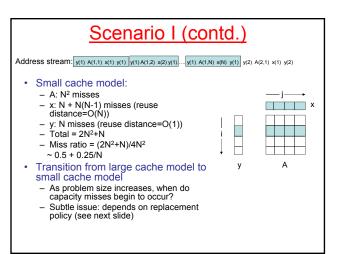

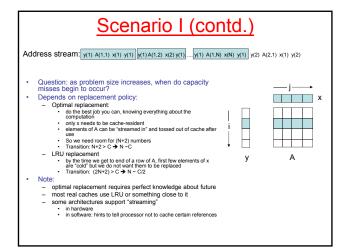

## Large and small cache models

- · Large cache model - no capacity misses

- only cold misses

- · Small cache model

- cold misses: first reference to a line

- capacity misses: possible for succeeding references to a line

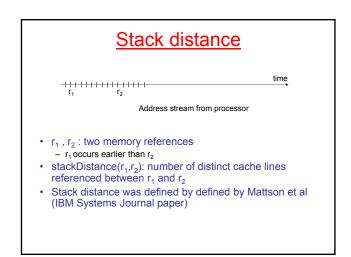

- let r1 and r2 be two successive references to a line - assume  $r_2$  will be a capacity miss if stackDistance( $r_1, r_2$ ) is some function of problem size

- argument: as we increase problem size, the second reference will become a miss sooner or later

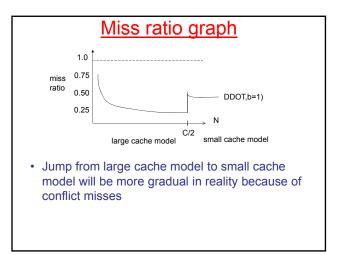

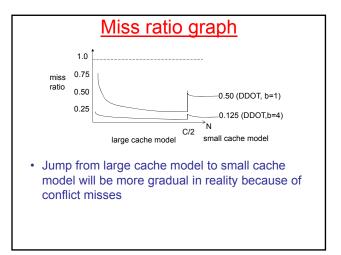

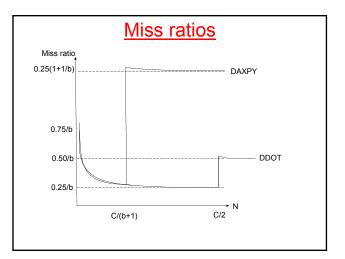

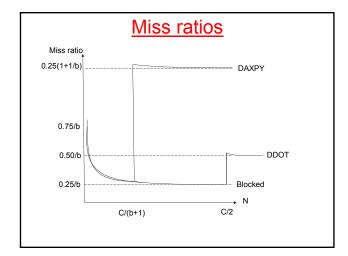

#### · For many problems, we can compute

- miss ratios for small and large cache models

- problem size transition point from large cache model to small cache model

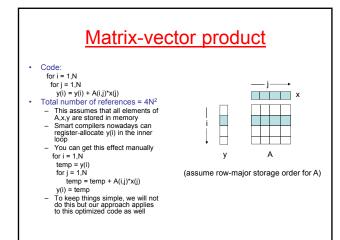

# MVM study

- · We will study five scenarios

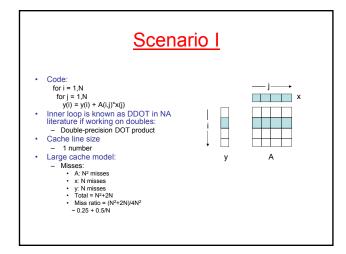

- Scenario I

- i,j loop order, line size = 1 number

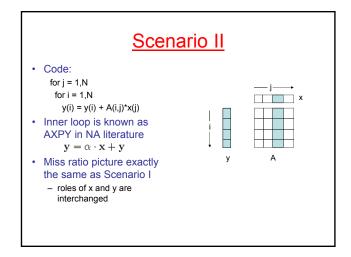

- Scenario II • j,i loop order, line size = 1 number

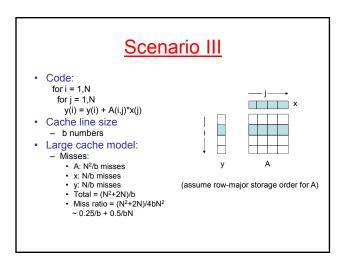

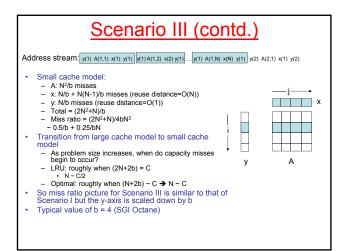

- Scenario III

- i,j loop order, line size = b numbers

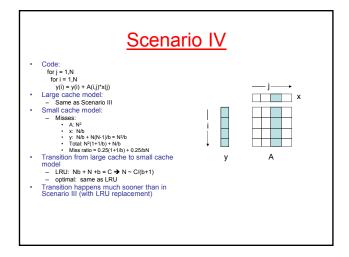

- Scenario IV

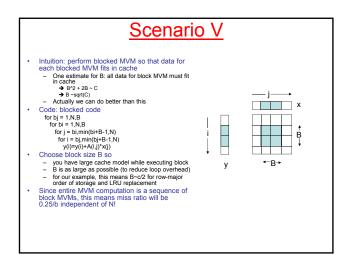

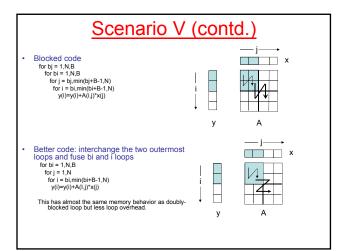

- j,i loop order, line size = b numbers - Scenario V

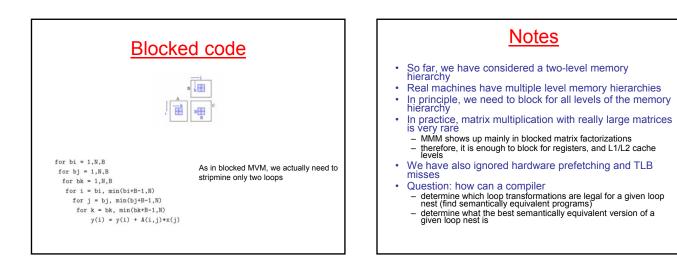

- · blocked code, line size = b numbers

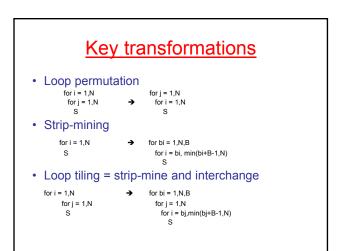

- Strip-mining does not change the order in which loop body instances are executed

so it is always legal

- Loop permutation and tiling do change the order in which loop body instances are executed

so they are not always legal

- For MVM and MMM, they are legal, so there are many variations of these kernels that can be generated by using these transformations

- different versions have different memory behavior as we have seen

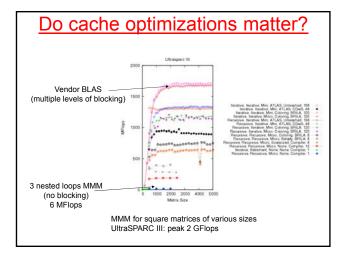

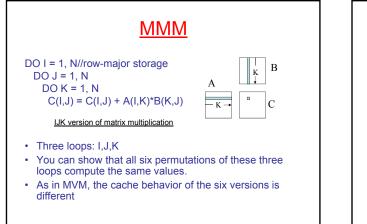

### Matrix multiplication

- · We have studied MVM in detail.

- In dense linear algebra, matrix-matrix multiplication is more important.

- Everything we have learnt about MVM carries over to MMM fortunately, but there are more variations to consider since there are three matrices and three loops.

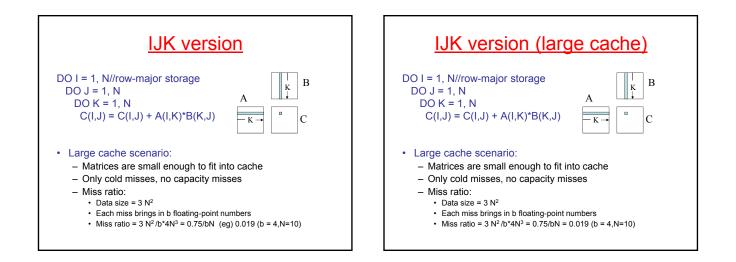

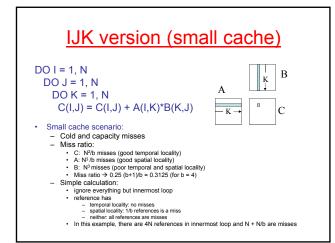

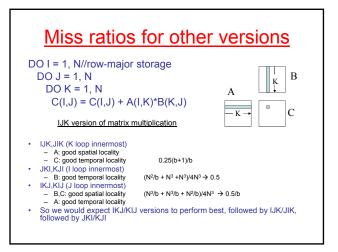

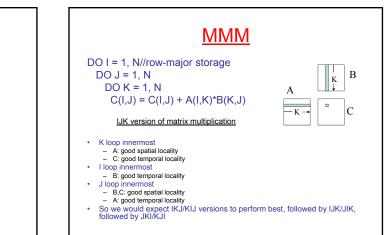

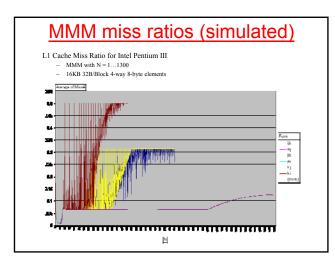

- Miss ratios depend on which loop is in innermost position

- so there are three distinct miss ratio graphs

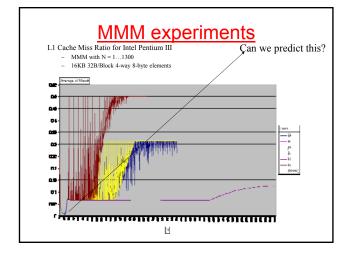

- Large cache behavior can be seen very clearly and all six version perform similarly in that region

- Big spikes are due to conflict misses for particular matrix sizes

- notice that versions with J loop innermost have few conflict misses (why?)