# A Formal Model of Asynchronous Communication and Its Use in Mechanically Verifying a Biphase Mark Protocol

J Strother Moore

Technical Report 68

1992

Computational Logic Inc. 1717 W. 6th St. Suite 290 Austin, Texas 78703 (512) 322-9951

## **Abstract**

In this paper we present a formal model of asynchronous communication as a function in the Boyer-Moore logic. The function transforms the signal stream generated by one processor into the signal stream consumed by an independently clocked processor. This transformation "blurs" edges and "dilates" time due to differences in the phases and rates of the two clocks and the communications delay. The model can be used quantitatively to derive concrete performance bounds on asynchronous communications at ISO protocol level 1 (physical level). We develop part of the reusable formal theory that permits the convenient application of the model. We use the theory to show that a biphase mark protocol can be used to send messages of arbitrary length between two asynchronous processors. We study two versions of the protocol, a conventional one which uses cells of size 32 cycles and an unconventional one which uses cells of size 18. Our proof of the former protocol requires the ratio of the clock rates of the two processors to be within 3% of unity. The unconventional biphase mark protocol permits the ratio to vary by 5%. At nominal clock rates of 20MHz, the unconventional protocol allows transmissions at a burst rate of slightly over 1MHz. These claims are formally stated in terms of our model of asynchrony; the proofs of the claims have been mechanically checked with the Boyer-Moore theorem prover, NOTHM. We conjecture that the protocol can be proved to work under our model for smaller cell sizes and more divergent clock rates but the proofs would be harder. Known inadequacies of our model include that (a) distortion due to the presence of an edge is limited to the time span of the cycle during which the edge was written, (b) both clocks are assumed to be linear functions of time (i.e., the rate of a given clock is unwavering) and (c) reading "on an edge" produces a nondeterministically defined value rather than an indeterminate value. We discuss these problems.

**Keywords**: hardware verification, fault tolerance, protocol verification, clock synchronization, Manchester format, FM format, automatic theorem proving, Boyer-Moore logic, ISO protocol level 1, performance modeling, microcommunications.

## 1. Introduction

In this paper we will (a) formalize the lowest-level communication between two independently clocked digital devices, (b) formalize the statement that, under certain conditions on the clock rates of the two processors, a biphase mark protocol permits the communication of arbitrarily long messages under our model of asynchronony, and (c) describe a mechanically checked formal proof that the statement is a theorem. Put less pedantically, we will exhibit a formal model of asynchronous communication and use it to prove that a commonly used protocol works.

We have tried to make this paper accessible both to hardware engineers, who are familiar with such terms as "asynchronous," "clock rates" and "digital phase locking," and to theorists, who are familiar with "formalize," "theorem" and "proof." Our attempt to bridge the gap between these two communities is largely found in the optional "boxes" scattered throughout the paper. There we try to explain possibly unfamiliar terms without detracting from what is otherwise a direct presentation of our formal model and the example of its use.

The biphase mark protocol—variously known as "Bi-φ-M," "FM" or "single density" and sometimes called a "format" rather than a "protocol"—is a convention for representing both a string of bits and clock edges in a square wave. Biphase mark is widely used in applications where data written by one device is read by another. For example, it is an industry standard for single density magnetic floppy disk recording. It is one of several protocols implemented by such commercially available microcontrollers as the Intel 82530 Serial Communications Controller [17] (where it is implemented with digital phase locking). A version of biphase mark, called "Manchester," is used in the Ethernet [28] and is implemented with digital phase locking in the Intel 82C501AD Ethernet Serial Interface [17]. Biphase mark is also used in some optical communications and satellite telemetry applications [30]. There is no doubt that it works. But, as far as we have been able to determine, a rigorous analysis of its tolerance of asynchrony has not been done. This is a grey area because it is at the boundary between continuous physical phenonmenon (e.g., waves and interference) and discrete logical phenomenon (e.g., counting and algorithms).

Nevertheless, despite the apparent novelty of a rigorous analysis of a fundamental protocol, this paper is not really about the protocol. It is about a formal, logical model of asynchrony. We look at biphase mark only to illustrate how the model can be used.

Whether the assumptions in our model are valid is an engineering problem; indeed, accurately modeling the environment in which a device is expected to work may be the hardest problem the engineer faces. We offer no solution to that problem. In some sense there *is* no solution to that problem. It is up to the engineer to decide if a given model is accurate enough.

By expressing the model formally, one is forced to characterize precisely the requirements and assumptions. This done, one is then free to analyze them rigorously. In fact, we use mechanical aids that make the analysis both easier and less error prone.

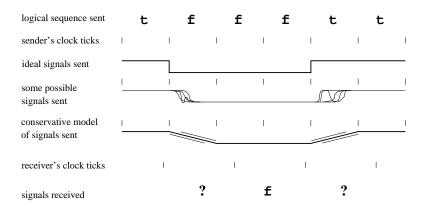

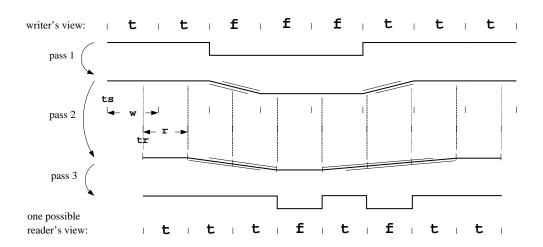

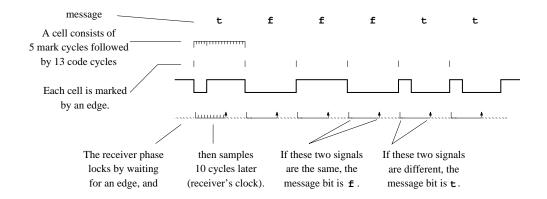

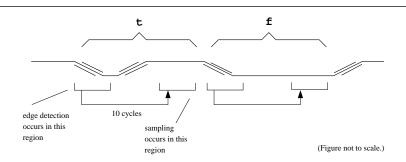

In Figure 1 we illustrate the difficulty of interfacing two independently clocked devices (see box). The figure shows what might happen if one device sends the signal stream "tffftt" to an asynchronous receiver whose clock is half-again slower and initially almost one full cycle out of phase.

¹In this paper we use t and f to denote the Boolean values of "truth" and "falsity." These are also the values we use for "bits" (instead of 1 and 0) and "signals" (instead of 'high" and "low"). Because timing diagrams are helpful in explaining our model, we adopt the convention that t is pictured "high" and f is pictured "low."

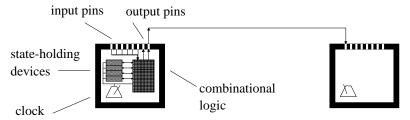

## **Microprocessors**

A microprocessor is finite-state machine. Shapes and sizes vary but it is not inappropriate to imagine a rectangular piece of material about as large as a fingernail. On the outer edges of the rectangle are gold pins that allow electrical connections to other devices. We partition the pins into "input" and "output" pins (though in many devices some pins are both) with the understanding that the device is sensitive to the voltages on the former and sets the voltages on the latter. These voltages are called "signals." When the voltage is above a certain threshhold it is called "high" and when it is below some other threshhold it is called "low." Intermediate voltages are discussed below. Inside the rectangle are the memory devices, which store the state of the machine, and combinational logic, a network of wires and Boolean logic "gates," for computing new states and output signals as a function of the old state and input signals. A metronome-like clock (usually a quartz crystal) ticks constantly during the operation of the machine. Typical clock rates are 20MHz, which means the clock ticks twenty million times a second. Each time the clock ticks the machine changes state. The state change is not instantaneous; it may take an appreciable portion of the cycle from one tick to the next for the new state to stabilize. Exactly when during the cycle the machine "reads" and "writes" its pins is entirely dependent upon the internal design of the machine.

An intermediate voltage on a pin may cause the device to behave contrary to this description. In particular, it may create a "metastable" state. Such a state may may appear to oscillate between different defined states or may spontaneously decay into a stable defined state independently of the clock and the mathematically understood state-transition function. Hardware designers strive to avoid the possibility that intermediate voltages appear on pins.

Now suppose we have two such processors. They are "asynchronous" with respect to each other because their clocks are independent. Suppose we connect an output pin of one to an input pin of the other. On every cycle of the first processor, some signal is written to the output pin and thus, after a suitable delay, appears at the input pin of the other processor. But because of the asynchrony, more than one signal may appear on the pin during a single cycle; the signal actually sensed and used to compute the next state of the receiving processor may be ill-defined or nondetermistically defined.

The problem of interfacing two such processors is a common one and usually occurs whenever a digital computer is connected to any other digital device (e.g., a modum, a disk drive, etc.).

Observe that in the ideal timing diagram, the signal falls from to f on the writer's second cycle. This is an idealization in two senses. First, the edge is not vertical or square, the signal changes continuously and may "ring" before stabilizing at its new level. Second, it does not happen immediately upon the clock tick that starts the second cycle. In fact, all that is promised by the ideal diagram is that the signal is stable and low by the end of the cycle. The funny looking "multivalued ramps" in the conservative model depicted in Figure 1 are intended to convey nothing more than that the signal is considered nondeterministically defined throughout the indicated cycles. We then impose upon that conservative diagram the receiver's clock ticks. Consider the receiver's first cycle. We do not know when during this cycle the receiver samples the signal (the time at which sampling occurs may be data dependent). But since the signal varies during the cycle, the exact time at which the receiver samples determines what is sensed. If it samples at

Figure 1: How Asynchrony Mangles Signals

the "wrong" time it could even read an indeterminate signal that could induce a metastable state. Things are simpler during the receiver's second cycle; the signal is constant at  $\mathbf{f}$  for the duration of the cycle and hence we are assured that it reads an  $\mathbf{f}$ .

The problem of metastability caused by reading on an edge cannot be solved perfectly by digital logic alone. By cascading the asynchronous signal through several state-holding devices on successive clock ticks of the receiver one can increase the probability that the signal stabilizes before it enters into the determination of the next state. Such cascades are called "synchronizers" but there is some degree of wishful thinking here since there remains a non-zero probability that the metastable state persists [22]. One can also build devices with hysteresis, e.g., Schmitt triggers, that require well-defined input before changing their output. Such devices can be used to sharpen an edge, but since these devices essentially just narrow the band of indeterminacy, there is still some chance that metastability will slip in. In summary, metastability is an engineering problem that apparently has no perfect solution. We do not attempt to model it. Our model assumes that "reading on an edge" nondeterministically produces a t or an f.<sup>2</sup> It is up to the engineer to arrange that some well-defined signal is read on each cycle.

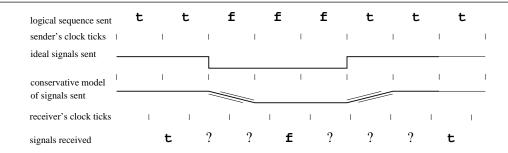

This however does not solve the communications problem. Nondeterministically replacing the question marks in Figure 1 by ts and fs does not enable the recovery of the original signal stream. Even an accurate analysis of which read cycles produce nondeterministic signals or how many such cycles there are requires careful consideration of the two clock rates and their phase displacement. For example, as illustrated in Figure 2, if the rates are nearly identical (the usual case) and the receiver's cycle is the shorter, then, depending on the initial phase displacement (which can be arbitrary for two physically independent clocks), an edge in the arriving signals can affect two or sometimes three successive read cycles. Nondeterministically replacing the question marks by ts and fs has the effect of blurring or shifting the edges in the signal. Differences in the clock rates of the two processors may stretch or shrink the apparent duration of the signal.

Communications protocols have been developed to deal with these problems. To avoid the first problem,

<sup>&</sup>lt;sup>2</sup>It is possible to model indeterminate signals logically. Three- and even four-valued logics are common in hardware description languages. We have mechanically proved that in one such logic it is impossible to build even a simple asynchronous edge detector with perfect reliability. The NQTHM transcript is available upon request.

Figure 2: One Edge Can Influence Several Read Cycles

the asynchronous sender generally encodes its message as a waveform with a relatively long wavelength compared to the cycle time of the receiver, giving the receiver plenty of time to sample the signal away from the edges. To overcome the second problem, the biphase mark protocol encodes the message with "frequency modulation" of the long wavelength "carrier." This allows the receiver to "phase lock" onto the artificially slower clock of the sender.

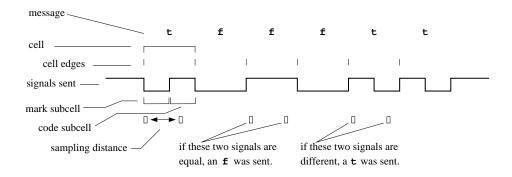

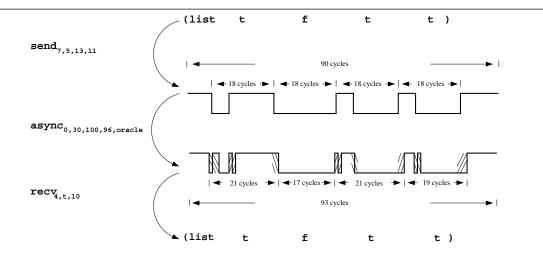

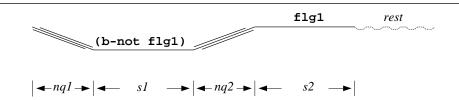

In the biphase mark protocol (see Figure 3), each bit of message is encoded in a "cell" which is logically divided into what we call a "mark subcell" and a "code subcell." During the mark subcell, the signal is held at the negation of its value at the end of the previous cell, providing an edge in the signal train which marks the beginning of the new cell. During the code subcell, the signal either returns to its previous value or does not, depending on whether the cell encodes a t or an f. The receiver is generally waiting for the edge that marks the arrival of a cell. Upon detecting the edge, the receiver counts off a fixed number of cycles, here called the "sampling distance," and samples the signal there. The sampling distance is determined so as to make the receiver sample in the middle of the code subcell. If the sample is the same as the mark, an f was sent; otherwise a t was sent. The receiver then resumes waiting for the next edge, thus "phase locking" onto the sender's clock.

Of course, asynchrony may blur or shift the edges of the code subcell, but if the code subcell is sufficiently long, some region of it (away from the edges) will be well-defined. We call this region the "sweet spot." The receiver should always sample from the sweet spot. What might prevent this? A plausible scenario is that the receiver is late detecting the mark because of nondeterminism and then waits too long before sampling because its clock is slower than the sender's.

This scenario should make it clear that the extent to which the protocol relies upon the near agreement of the two clock rates is dependent upon how far the sweet spot is from the mark. It is while measuring out this time interval (while creating the cell in the sender or waiting to sample in the receiver) that the protocol implicitly assumes the two processors cycle at the same rate. If two clocks are used to measure out some absolute time interval, and the two clock's rates are fixed but slighly different, their discrepancy in the measurement is linearly proportional to the length of the interval measured. Thus, the closer the sweet spot

<sup>&</sup>lt;sup>3</sup>The word "mark" in "biphase mark" comes from the "Automatic Recorder" of 19<sup>th</sup> century telegraphy where the line idle state produced a mark on a rotating drum and the arrival of a pulse lifted the stylus to produce a space [8]. The names MARK and SPACE were adopted for logical 1 and logical 0 respectively. However, except in the name "biphase mark," our use of the word "mark" is intended in its nontechnical sense, i.e., "a conspicuous object serving as a guide for travelers" [24]. Thus we speak of the "mark subcell," so named because it indicates the beginning of the cell, and of "detecting the mark."

Figure 3: Biphase Mark Terminology

is to the mark, the more tolerant the protocol is to different clock rates.

To analyze the behavior of the protocol in the face of asynchrony we must specify the cell size, subcell sizes, and sampling distance. We study a conventional choice and an unconventional one. The conventional choice is cell size 32, equally divided into two 16-cycle subcells, sampled on the 23<sup>rd</sup> cycle after mark detection. The unconventional choice is cell size 18, divided into a 5-cycle mark and a 13-cycle code subcell, sampled on the 10<sup>th</sup> cycle after mark detection. The unconventional choice permits a faster bit rate (since fewer cycles are spent on each bit) and tolerates more divergent clock rates (since the time during which the clocks must "stay together" is smaller). Do they work?

In this paper we formally (see box) define a model of asynchrony and we formally state and prove the theorem that, under the model, the 18-cycle/bit biphase mark protocol properly recovers the message sent, provided the ratio of the two clock rates is between 0.95 and 1.05. According to [29] typical clocks are incorrect by less than  $15\times10^{-6}$  seconds per second and the ratio of the rates of two such clocks are well within our bounds. We have proved that the conventional choice of cell size also works, provided the ratio of the clock rates is within 3% of unity, and we briefly indicate how the proof differs from the proof of the 18-cycle version.

## 2. Logical Foundations

We use the NQTHM "computational logic" described in [6].

Truth values, bits, and signals will all be represented by the logical objects t and f which are distinct constants. We call these two objects the "Booleans" and we define a predicate, boolp, which recognizes just them.

Observe that, as in Lisp, we write function applications with the parentheses "on the outside." Thus, we write (**boolp**  $\mathbf{x}$ ) to mean the value of the function **boolp** applied to  $\mathbf{x}$ , i.e., **boolp**( $\mathbf{x}$ ). As can be seen

#### **Formalization**

What do we mean when we say we define the model or state the theorem "formally?" We mean we exhibit a formula that purportedly captures the idea. Because we are interested in mathematical proof, we write our formulas in the language of a particular mathematical logic. A logic provides a language, some axioms (formulas assumed to be true), and some rules of inference (truth preserving operations on formulas). To prove a theorem is to derive that formula from the axioms using the rules of inference.

The logic we use is called the "NQTHM" or "Boyer-Moore" logic. Its language resembles Pure Lisp; its axioms define the primitive functions for if-then-else, equality, and list and number processing; its rules of inference include such familiar ones as "substitution of equals for equals," "every instance of a theorem or axiom is a theorem" and mathematical induction. We will explain the logic as we go.

But how can we write a formula that says the biphase mark protocol works in the face of asynchrony? Because the NQTHM logic is essentially just a programming language without side-effects, the whole formalization problem can be recast as a programming problem:

**Challenge**: Write a Pure Lisp program (together with its subroutines) with the property that if the program returns **t** on all possible inputs then you will believe that the biphase mark protocol works.

Ah! This is a straightforward programming problem. The solution is to write a "simulator" for the system being modeled. That is, we will develop a Pure Lisp program that takes among its inputs a message to be tested, the precise clock rates of the two processors, and their initial phase displacement and delay, and simulates the encoding, sending, receiving, and decoding of the message. The "simulator" will return  $\mathbf{t}$  if the message is recovered and  $\mathbf{f}$  otherwise.

But how can such a simulator be run on all possible inputs? Clearly it cannot be. That is where we use proof. Since the simulator is just a collection of mathematically defined functions we can use substitution, instantiation, and induction to show that the simulator always returns t.

by an inspection of the definition, (boolp x) is t if and only if x is t or x is f.

The NQTHM logic imposes restrictions on equations purporting to be "definitions." These restrictions insure that one and only one mathematical function satisfies the equation. Because of this assurance, we can add such admissible definitions to the logic without rendering the logic inconsistent. The reader should see [5, 6] for details. In this presentation we do not further concern ourselves with the admissibility of our definitions.

We define the operations of "negation" and "exclusive-or" as follows.

Fundamental to our formalization is the notion of a "bit vector" or a "finite sequence of Booleans." We

use lists (see box) to represent such objects. The following function recognizes bit vectors.

## Definition.

That is, (bvp x) is defined by cases. If x is a listp object, then its first element, (car x), must be Boolean and the rest of its elements, (cdr x), must recursively satisfy bvp. On the other hand, if x is not a listp object, it must be nil. An example bit vector is (list t t f f). That is, (bvp (list t t f f)) evaluates to t.

We shall use (len x) to denote the length of the list x, (app x y) to concatenate the lists x and y, (nth n x) to fetch the n<sup>th</sup> element of the list x (where (car x) is the 0<sup>th</sup> element), (cdrn n x) to cdr the list x n times, and (list n x) to make a list of n repetitions of the object x. We omit the definitions of these simple functions.

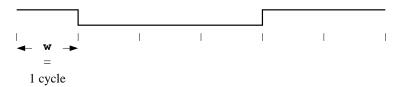

We will use lists of Booleans (bit vectors) to represent streams of signals or "timing diagrams." For example,

will be represented by the list (list t f f f t t) together with the fact that the length of a cycle is w. An alternative way of writing the same list is (cons t (app (listn 3 f) (listn 2 t))).

## 3. The Model of Asynchrony

Consider two independently clocked processors, which we call the "writer" and the "reader." The output pin of the former is connected by a wire to the input pin of the latter and this constitutes the only communication between them. Imagine that on successive cycles the writer is specified to set its output pin to the successive signals in some bit vector called the "writer's view." We wish to define a function, async, which will map the writer's view into the sequence actually read by the reader, which we call the "reader's view."

More precisely, we map the writer's view into any one of the possible reader's views, since there is an element of nondeterminancy here. One parameter of the model, called the 'oracle,' specifies how each nondeterministic choice is to be made on a given application of the model; by varying this parameter one can obtain all possible views by the reader.

Our model is based on three assumptions.

- The distortion in the signal due to the presence of an edge is limited to the time-span of the cycle during which the edge was written. For example, we ignore intersymbol interference [28].

- The clocks of both processors are linear functions of real time, e.g., the ticks of a given clock are equally spaced events in real time. We ignore clock jitter.

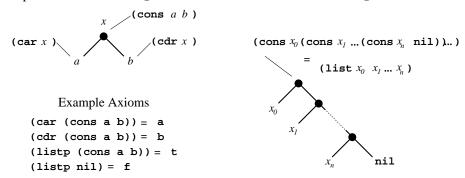

## **List Processing**

In the logic, lists are binary trees. Binary trees are ordered pairs constructed by the function **cons** from any two objects. The functions **car** and **cdr** return the two objects. The function **listp** recognizes just the objects produced by **cons**. That is, (**listp x**) is **t** or **f** depending on whether **x** is an ordered pair. We use (**nlistp x**) as an abbreviation for "non-listp."

We frequently define recursive functions on lists. For example, the "length" of a list  $\mathbf{x}$ , written (len  $\mathbf{x}$ ), is defined

## **Definition**.

Such definitions are usually read as "by cases." "If x is a listp, its length is obtained by adding one to the length of its cdr; if x is not a listp, its length is 0." Thus, (len (list t t f f)) is 4.

Given two lists, we can "concatenate" (or "append") them using the function app,

#### **Definition**.

We might paraphrase this as "To append a nonempty  $\mathbf{x}$  to  $\mathbf{y}$ ,  $\mathbf{cons}$  the first element ( $\mathbf{car}$ ) of  $\mathbf{x}$  to the result of appending the rest ( $\mathbf{cdr}$ ) of  $\mathbf{x}$  to  $\mathbf{y}$ . To append an empty  $\mathbf{x}$  to  $\mathbf{y}$ , return  $\mathbf{y}$ ." Thus,

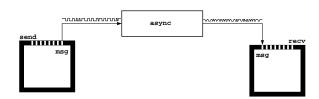

Reading on an edge produces nondeterministically defined signal values, not indeterminate values. Our model of asynchronous communication has three passes, one implementing each of the assumptions above. In Figure 4 we illustrate the passes. In pass 1, we identify those cycles in which the signal is

**Figure 4:** The Three Passes in the Model

undetermined due to the non-zero switching times on the writer. This is indicated in the graph in Figure 4 by the multivalued ramps on two of the write cycles. Pass 2 combines the pass 1 output with certain timing information (the cycle times, w and r, of the two processors and (roughly) their phase displacement, tr-ts) to produce the signal on the pin during each read cycle (up to nondeterminacy). Pass 2 is the key to the model and operates by reconciling all the signals on the pin during each read cycle. Pass 2 generally smears the nondeterminacy over any read cycles which overlap with it. Pass 2 may lengthen or shorten the length of the signal stream but does not change its basic shape. Pass 3 eliminates the nondeterminacy by using the oracle to choose arbitrary values for undetermined signals.

It should be noted that our model puts no constraints on the relationship between the writer's cycle time and the reader's. That is, one can apply this model to communication between two processors whose clocks run at wildly different rates. For example, if the reader runs ten times as fast as the writer, it will see roughly ten times more signals. The model is somewhat pathological if either processor runs infinitely fast (i.e., has a cycle time of 0). We do not constrain the relationship between the clocks until we begin to apply the model to prove that a certain protocol works.

We now back up and give a more detailed physical and formal explanation.

## 3.1 Pass 1

Consider the writer. On every cycle the writer sets the output pin to some value. If that value is the same as the previous value of the pin, then the signal on the pin remains stable at that value for the entire cycle. On the other hand, if the new value is different, then we assume the value on the pin is undetermined for the duration of that cycle. This accounts for our lack of knowledge about when during the cycle the voltage on the pin begins to change, how the voltage varies, and how long it takes it to become stable. Pass 1 in the model thus introduces "multivalued ramps" for the duration of every cycle during which the signal

changes. The ramps in our diagrams are formally represented by the "signal" 'q, which is just a token that will eventually be replaced nondeterministically. There is no need to distinguish "downward" ramps from "upward" ones since they both mean the signal is indeterminate for the entire cycle.

The function formalizing pass 1 is called **smooth** and it takes the previous signal seen, **x**, and a sequence of signals, **1st**.

##

Observe that **smooth** copies **lst**, changing to 'q any signal that is different from the previous one, x. In Figure 4, pass 1 is computed by (smooth t (list t t <u>f</u> f <u>f</u> t t), which replaces the underscored signals by 'qs.

#### 3.2 Pass 2

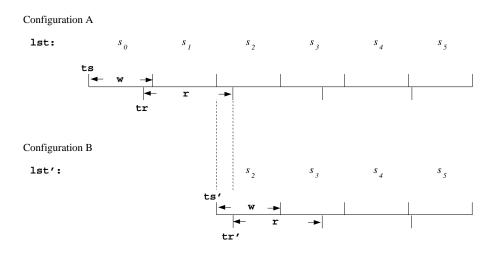

Now, let lst be the output of pass 1. In pass 2 we simulate the arrival of these signals at the input pin of the reader, consider the reader's cycles, and compute the signals read (up to nondeterminacy). Suppose the first signal, (car lst), arrives at the input pin at time ts.<sup>4</sup> All successive signals arrive at intervals of w, where w is the cycle time of the writer. Let tr be the time at which the reader's clock first ticks at or after ts. Without loss of generality we assume  $ts \le tr < ts + w$  because if  $tr \ge ts + w$  then the first signal of lst is simply irrelevant since it does not persist into the reader's first cycle. Finally, suppose the reader's cycle time is r. Given these parameters we can compute the entire list of signals read (up to nondeterminancy). We call the function formalizing pass 2 warp and define it below.

#### **Definition**.

The term (plus tr r), above, is the sum of tr and r and is the time at which the reader's clock next ticks. The definition may be read as follows: If r is zero<sup>5</sup> or else if lst does not have enough elements in it to determine the next signal read, return the empty list nil. The second condition is checked by endp which we discuss below. If r is nonzero and there are enough elements in lst to determine the next signal

<sup>&</sup>lt;sup>4</sup>More precisely, consider that tick of the writer's clock that began the write cycle during which the first signal was written. Let  $\omega$  be the time at which that tick occurred. Let  $\delta$  be the delay along the wire connecting the writer to the reader. Then **ts** is  $\omega$ + $\delta$ . We assume  $\delta$  is constant.

<sup>&</sup>lt;sup>5</sup>Omitting the (zerop r) test produces an inadmissible definition because the recursion described does not terminate.

read, we use **sig** (described below) to compute the signal read during the current cycle, we use **warp** recursively to obtain the list of signals read on successive cycles and then we **cons** together the two results to produce the list of all the signals read.

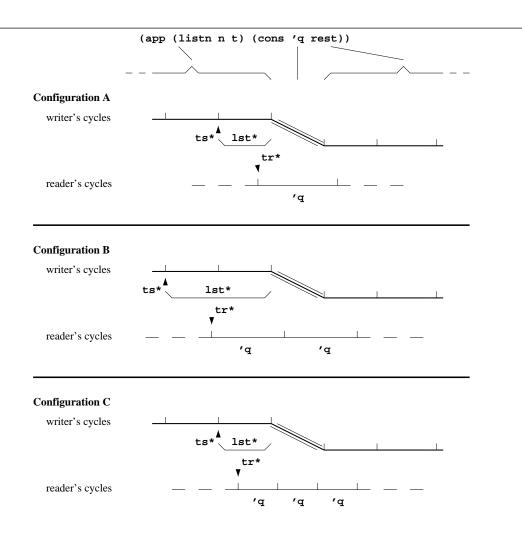

Figure 5: The Recursion in warp

We explain further by referring to Figure 5. Configuration A of the figure depicts the formal parameters of warp upon entry to (warp lst ts tr w r). Note that lst contains six signals,  $s_0$ , ...,  $s_5$  and that  $s_0$  arrives at time ts and persists for time w. The first tick of the reader's clock is at time tr and starts a cycle that persists for time r. By observing the diagram in Configuration A we see that the signals  $s_0$ ,  $s_1$  and  $s_2$  impinge upon the pin during this read cycle. If they are all equal, say, to  $s_0$ , then  $s_0$  will be the signal read on this cycle. But if any two are different, the signal read is nondeterministic (i.e., 'q). This is the computation made by (sig lst ts (plus tr r) w).

Configuration B of Figure 5 shows the parameters passed to the recursive call of **warp** from Configuration A. The call in question is

```

(warp (lst+ lst ts (plus tr r) w)

(ts+ lst ts (plus tr r) w)

(plus tr r)

w r)

```

The easiest argument term to understand is (plus tr), passed as the new value of tr. That is the time of the next tick of the reader's clock and is shown as tr' in Configuration B. The faint dotted line is meant to indicate that tr' is tr+r from Configuration A. Lst' is the new value of lst. Note that (in this case) the first two signals have been removed from lst. That is because they were used in the sig computation for the current cycle and do not affect the sig computation at the next cycle. Note that  $s_2$ , which was used by the sig computation, is still in lst' because it persists into the next cycle. Lst', which is always some cdr of lst, is computed by the function lst+ in the recursive call of warp. The time at which the new first signal arrives, ts', is computed by the function ts+.

The four functions **endp**, **sig**, **1st+**, and **ts+** are all very similar in that they scan **1st**, knowing that the first signal arrives at time **ts** and that subsequent ones arrive at intervals of **w**, and look for the first signal

that persists into the next cycle, i.e., the one that starts at (plus tr r). The function endp returns t if lst is exhausted before the desired signal is reached. Sig reconciles all the signals it reaches, using the auxiliary function reconcile-signals. Lst+ returns the cdr of lst starting with the desired signal. Ts+ returns the arrival time of the desired signal. The definitions are shown below.

```

Definition.

Definition.

(endp lst ts nxtr w)

(sig lst ts nxtr w)

(if (nlistp lst)

(if (nlistp lst)

t

'q

(if (lessp (plus ts w) nxtr)

(if (lessp (plus ts w) nxtr)

(endp (cdr lst) (plus ts w)

(reconcile-signals

nxtr w)

(car lst)

f))

(sig (cdr lst) (plus ts w)

nxtr w))

Definition.

(car lst)))

(reconcile-signals a b)

(if (equal a b) a 'q)

Definition.

Definition.

(1st+ 1st ts nxtr w)

(ts+ lst ts nxtr w)

(if (nlistp lst)

(if (nlistp lst)

lst

ts

(if (lessp nxtr (plus ts w))

(if (lessp nxtr (plus ts w))

lst

(lst+ (cdr lst) (plus ts w)

(ts+ (cdr lst) (plus ts w)

nxtr w)))

nxtr w)))

```

Readers familiar with NQTHM will have noticed that the arithmetic primitives used in warp treat their arguments as natural numbers. That is, ts, tr, w, and r in this model are nonnegative integers. Since time appears continuous, the reals or the rationals seem more appealing domains for these parameters. However, the NQTHM logic does not support the reals. The rationals have been defined within the logic and they were used when the model was first being formalized. However, the proof we will describe is primarily concerned with counting cycles. We found that the proof was complicated by the mix of (formal) natural arithmetic and (formal) rational arithmetic. We decided to simplify matters by adopting natural arithmetic entirely. It should be stressed that this is primarily a technical problem with the NQTHM mechanization and its heuristics.

Inspection of the model will reveal that our use of natural arithmetic does not limit the applicability of the model. In particular, if ts, tr, w, and r are given as rational numbers, one could convert them to four naturals over a common denominator and then do all the arithmetic on the numerators only, using natural arithmetic. This observation relies on the fact that the model only iteratively sums and compares these quantities. But  $\frac{a}{d} + \frac{b}{d} = \frac{a+b}{d}$ , where the first "+" is that for rational arithmetic and the second is that for natural arithmetic. A similar theorem holds for the "less than" relationships in the two systems.

An illustration of warp was presented in pass 2 of Figure 4. In that example, the input list was the output of pass 1, (list t t 'q f f 'q t t), ts was 0, tr was 75, w was 100, and r was 87. The output of warp was (list t 'q 'q f 'q 'q 'q t). We used grossly mismatched w and r merely so that it was easy to see that read cycle 5 (counting from 0) fell entirely within write cycle 5. Exactly identical signal output can be obtained with more realistically matched clocks. For example, let us measure time in tenths of picoseconds, e.g., units of  $10^{-13}$  seconds. If the writer has a perfect 20MHz clock then w is 500,000. Suppose the reader is nominally 20MHz but ticks faster so that in twenty million ticks it

counts off .999996 seconds. That is,  $\mathbf{r}$  is 499,998 and the clock is gaining roughly  $4\times10^{-6}$  seconds per second, which is consistent with the clocks reported in [29]. Then if the first signal in the output of pass 1 reaches the reader  $11\times10^{-13}$  seconds before the reader's clock ticks, the output is as described in pass 2 of Figure 4. I.e., (warp (list t t 'q f f 'q t t) 0 11 500000 499998) is (list t 'q 'q f 'q 'q 'q t).

#### 3.3 Pass 3

It is the job of pass 3 to eliminate the nondeterministic signals using the oracle. The function formalizing this pass is called **det** (for "determine").

##

(det (cdr lst) oracle))))

The oracle parameter to our model is just an arbitrary list. The successive elements of the oracle are matched with the successive 'qs in the list of signals to be processed, lst. Each oracle element specifies whether the corresponding 'q should be replaced by t or by f.<sup>6</sup> Det merely copies the list of signals, replacing each 'q as directed by the oracle.

## 3.4 Combining the Passes

Finally, to define **async** we compose the three passes.

(cons (car 1st)

### Definition.

Observe that we **smooth** the writer's view using t as the initial signal on the pin. This is an arbitrary choice.

## 4. The Biphase Mark Protocol

One use of a formal model of asynchrony is to investigate the circumstances under which communication protocols work properly. We illustrate such a use of our model by considering a biphase mark protocol. Recall Figure 3 where the protocol is informally described.

We will use an unbalanced configuration in which the mark subcell is just long enough to guarantee that it will be detected and the code subcell is just long enough to guarantee that the sweet spot is always sampled. See Figure 6.

<sup>&</sup>lt;sup>6</sup>The axioms of the NQTHM logic define car and cdr to be non-f constants on non-listps. The effect here is that if oracle is too short it is implicitly extended with as many ts as required.

Figure 6: Our Modified Biphase Mark Protocol

In order to state a theorem about the protocol we must formalize it. In our formalization, the sizes of the two subcells and the sampling distance are parameters that are not fixed until we state the correctness theorem.

## 4.1 Sending

We will formalize the send side of the protocol by defining a function that maps from messages to signal streams, both of which are formally represented by bit vectors.

The fundamental notion in the protocol is that of the "cell." Each cell is a list of  $\mathbf{n}+\mathbf{k}$  signals. Each cell encodes one bit,  $\mathbf{b}$ , of the message, but the encoding depends upon the signal,  $\mathbf{x}$ , output immediately before the cell. Let  $\mathbf{\bar{x}}$  be ( $\mathbf{b}-\mathbf{not}\ \mathbf{x}$ ). Let  $\mathbf{csig}$  be ( $\mathbf{if}\ \mathbf{b}\ \mathbf{x}\ \mathbf{\bar{x}}$ ). Then a cell is defined as the concatenation of a "mark" subcell containing  $\mathbf{n}\ \mathbf{\bar{x}}$ s followed by a "code" subcell containing  $\mathbf{k}\ \mathbf{csigs}$ s.

## **Definition**.

Because (if  $b \times (b-not \times)$ ) reoccurs, it is convenient to define it as (csig  $\times b$ ). Observe that the last signal in the cell is (csig  $\times b$ ).

To encode a bit vector,  $\mathbf{msg}$ , with cell size  $\mathbf{n}+\mathbf{k}$ , assuming that the previously output signal is  $\mathbf{x}$  we merely concatenate successive cells, being careful to pass the correct value for the "previous signal."

#### Definition.

We adopt the convention that the sender holds the line high before and after the message is sent. Thus, on either side of the encoded cells we include "pads" of t, of arbitrary lengths p1 and p2. The formal definition of send is

#### Definition.

```

(send msg p1 n k p2)

=

(app (listn p1 t)

(app (cells t n k msg) (listn p2 t))).

```

To send the message (list t f t t) with cells of size 1+2, padding the message at the front with three ts and at the back with five ts, we use (send (list t f t t) 3 1 2 5). Its value is shown in Figure 7.

```

(send (list t f t t) 3 1 2 5)

=

(list t t f f f f t f f t t t t t t )

```

Figure 7: Sending (list t f t t) with Cells of Size 1+2

## 4.2 Receiving

The receive side of the protocol will be formalized as a function from signal streams to messages. We need two auxiliary functions.

scan takes a signal, x, and a list of signals, 1st, and scans 1st until it finds the first signal different from x. If 1st happens to begin with a string of xs, scan finds the first edge.

#### **Definition**.

For example, (scan t (list t t t f f f t)) is (list f f f t).

**Recv-bit** is the function that recovers the bit encoded in a cell. It takes two arguments. The first is the 0-based sampling distance, **j**, at which it is supposed to sample (e.g., if the cell length is 5+13, then **j** is 10). The second argument is the list of signals, starting with the first signal in the mark subcell of the cell.

### Definition.

The bit received is t if the first signal of the mark is different from the signal sampled in the code subcell;

otherwise, the bit received is £.

We can use **scan** and **recv-bit** to define the receive protocol. In our formalization, the receiver must know how many bits, **i**, to recover. In an actual application this might be a constant or it might have been transmitted earlier in a message of constant length. The list of signals on which **recv** operates should be thought of as starting with the signal, **x**, sampled in the code subcell of previous cell. If **i** is 0, the empty message is recovered. Otherwise, **recv** scans to the next edge (i.e., it scans past the initial **x**s to get past the code subcell of the previous cell and to the mark of the next cell). **Recv** then uses **recv-bit** to recover the bit in that cell and conses it to the result of recursively recovering **i**-1 more bits.

#### **Definition**.

Observe that in its recursive call, the new list of signals is the tail of **lst** that begins with the signal sampled by **recv-bit**. The new **x** is that signal.

To illustrate **recv**, let *lst* be the list produced by the **send** expression in Figure 7. Then (**recv 4 t 2** *lst*) is the original message, (**list t f t t**).

The phase locking is essentially implemented by scan. Observe that in all uses of lst, recv uses scan to find the first edge. Thus, no matter how many trailing signals there are in a cell (due to the different rates at which the two processors count), recv phase locks onto the beginning of the new cell. The clock rates are crucially important only from the time the cell is detected to the time the code subcell is sampled.

## 5. The Theorem

Do **send** and **recv** cope with the problems introduced by asynchrony? We can address this question formally now.

Figure 8: The Composition of send, async and recv

The diagram in Figure 8 suggests something we would like to prove about **send**, **async**, and **recv**: their composition is an identity. Of course, this is true only under certain assumptions, which we must make

explicit. The composition we will study is

We discuss this term from the inside out, making our assumptions clear.

(send msg p1 5 13 p2): We send some message msg in cells of size 5+13 with a leading pad of p1 ts and a trailing pad of p2 ts. We will require that msg be a bit vector but it can have arbitrary length. P1 and p2 are arbitrary (though, for technical reasons, we will require that the first one, at least, is a natural number).

(async (send ...) ts tr w r oracle): The signal stream generated by send is fed, in turn, to our model of asynchrony, which has the four clock parameters and the oracle as additional arguments. The model itself imposes certain constraints on the clock parameters: all are nonnegative integers and ts  $\leq$  tr < ts+w. Those conditions put no limitation on the applicability of our result; it would still address arbitrarily clocked processors, arbitrary delay between them, and arbitrary phase displacement. However, some restrictions must be imposed to make the composition an identity. First, we must assume that the cycle times, w and r, are nonzero in order to avoid obvious pathological failures. Second, we must assume that the cycle times are "in close proximity," which we will make precise by defining (rate-proximity w r). The condition we wish to impose is  $\frac{17}{18} \leq \frac{w}{r} \leq \frac{19}{18}$ . But since we have limited ourselves to natural arithmetic, we define rate-proximity equivalently via

#### **Definition**.

```

(rate-proximity w r)

=

(and

(not (lessp (times 18 w) (times 17 r)))

(not (lessp (times 19 r) (times 18 w)))).

```

We put no restrictions on oracle, thus addressing ourselves to all possible nondeterministic behaviors.

(recv (len msg) t 10 (async ...)): Finally, the output of our model is fed to the receiver. We impose no additional restrictions due to this term. But note that the first three arguments to recv limit the applicability of the theorem to cases in which we are trying to recover the correct number of bits of message, the line is initially high, and each cell is sampled 10 cycles after mark detection.

The theorem we will prove, named "BPM18" for "Biphase Mark, 18-cycles/bit," is

```

Theorem.

BPM18

(implies

(and (bvp msg)

(numberp ts)

(numberp tr)

(not (zerop w))

(not (zerop r))

(not (lessp tr ts))

(lessp tr (plus ts w))

(rate-proximity w r)

(numberp p1))

(equal (recv (len msg)

t 10

(async (send msg pl 5 13 p2)

ts tr w r oracle))

```

msg)).

The theorem would appear simpler had we built in the constants 10, 5 and 13 as well as the pad lengths, **p1** and **p2**, and the initial line value, **t**. We stated the theorem this way so it was convenient to experiment with different values.

The definition of **rate-proximity** forces  $\frac{\mathbf{w}}{\mathbf{r}}$  to be within  $\frac{1}{18}$  of unity. For what it is worth,  $\frac{1}{18}$  is  $0.0\overline{5}$ , or somewhat more than 5%.

## **Formalization Revisited**

Recall that the formalization problem can be cast as a programming problem:

**Challenge**: Write a Pure Lisp program (together with its subroutines) with the property that if the program returns  $\mathbf{t}$  on all possible inputs then you will believe that the biphase mark protocol works.

BPM18 can be regarded as a Pure Lisp program that takes eight arguments: msg, ts, tr, w, r, p1, p2, and oracle. For specifically given values of those eight arguments it is straightforward to compute the value of the formula. The value will be t if the arguments satisfy the hypothesis and the conclusion is true or if the arguments fail to satisfy the hypothesis. The value will be f otherwise.

If BPM18 is a theorem, then this program will return **t** on all inputs. Suppose it is a theorem. Do you believe that the biphase mark protocol always works under the hypothesis given? *That* is the formalization problem.

## 6. Formal Experiments

Before attempting to prove anything about **send** and **recv** we simply execute them to illustrate how they cope with **async**. Suppose we want to send the message (list t f t t), using our 5+13 cycle protocol. To be concrete, we will precede the transmission with seven high cycles and follow it with eleven high cycles. The appropriate **send** expression is (**send** (list t f t t) 7 5 13 11). A total of 90 write cycles are modeled in the output of this expression. The output is displayed graphically in Figure 9.

Now suppose the writer has a cycle time of 100, suppose the reader has a cycle time of 96, and suppose the first signal in the output arrives at the reader 30 time units before the reader's clock next ticks. Figure 9 shows (one of) the received waveforms. The **oracle** argument to **async** determines which of the waveforms is actually received. **Recv** must be able to cope with all of them. Observe that in this example, a total of 93 read cycles are modeled. The cells parsed by **recv** consume varying numbers of cycles. This variance is in part due to the slightly faster cycle time of the reader and in part to the nondeterministic choices on where the edges are located.

**Recv** correctly recovers the message (list t f t t) in this example.

Figure 9: An Experiment with send, async, and recv

## 7. Proofs

BPM18 can be proved by transforming it into a slightly different form and then appealing to a more general theorem which we prove by induction. We give the proof later. We do not include in this paper the entire NQTHM transcript. Readers interested in the transcript should write the author. The transcript will reproduce the entire proof on the released version of the NQTHM theorem prover.

Our proof strategy is roughly as follows.

- We derive the shape of the **send** waveform after it has been processed by the first two passes of **async**, that is, we produce the ramped version of the received waveform. To do this we shall have to develop a body of lemmas about **async** and its subfunctions. We call this the "reusable theory" of **async** because it is independent of our particular application.

- We establish bounds on the lengths of each of the regions in the ramped waveform. This is basically a continuation of the reusable theory.

- We move into **recv** and show that scanning across a ramp nondeterministically defines a point in a region whose length is one larger than the ramp.

- Finally, this point is translated down the ramped waveform a fixed distance by **cdrn**, where it becomes the sampling point, and is shown to fall in the "sweet spot"—that portion of the code subcell unaffected by ramps. This final step requires proving two key inequalities that establish that the sweet spot entirely contains the nondeterministically defined sampling point. These inequalities are proved by appealing to the bounds on the lengths of the various regions.

Because the message is of arbitrary length, all four of these steps are wrapped in an induction on the length of the message and are applied in turn to that portion of the wave generated in response to a single bit of the message.

## 7.1 The Reusable Theory of Async

## 7.1-A The Waveform Generators

While some steps in the proof are concerned with the peculiar properties of **send** and **recv**, most of the work is in establishing general properties of **async** and its interaction with the waveform primitives, **app** and **listn**.

In what sense are **app** and **listn** the "waveform primitives?" Informally, ideal signals are square waves; in our formalism, these square waves are generated by combinations of **listn** and **app** expressions—we use **listn**s to generate either "high" or "low" horizontal lines and then use **app**s to stick them together to form the vertical edges. As the signals get smoothed and warped in our model, the square corners become multivalued ramps; these ramps are formally generated by more **listn** expressions, only this time the signal repeated is 'q. Thus, from the formal or algebraic point of view, the signal generators are **app** and **listn**. Because timing is crucial, we are also interested in the length, i.e., **len**, of such waveforms.

Given some input waveform, described formally, we would like to have enough symbolic machinery to allow us to derive the waveform produced by **async**. We would like both the input and the output waveforms to be described in terms of **app** and **listn**. Therefore, we seek a collection of theorems about **app**, **listn**, **len** and the three passes of **async**. Most of the theorems express distributivity laws, e.g., how to express the **smooth** of an **app** as the **app** of two **smooths**. These theorems are independent of the particular signals generated by the biphase mark protocol. They are a first step toward what we call a "reusable formal theory" or "rule book" for **async**. They are only the first step because we stopped when we had enough rules to prove biphase mark correct.

#### 7.1-B Elementary Rules

There are a variety of rules about **app** and **listn** that we here take for granted, though they were stated and proved in our mechanically checked work. We state a few as warm-up exercises.

The last rule may bear explaining. Generally when we see the **app** of two **listn** expressions it describes an edge. But if the signal repeated by the first **listn** is the same as that repeated by the second, there is no edge and the **app** can be collapsed into a single **listn**. That is, if you draw a horizontal line at

"high" followed by a horizontal line at "high" you get a (longer) horizontal line at "high."

We also assume all the usual theorems of integer arithmetic.

#### 7.1-C Rules about Smooth

Suppose we are confronted by an application of **async** to the **app** of some **listns**, i.e., we are trying to derive the shape of the waveform after **async** has mangled it. The definition of **async** can be expanded into a composition of **smooth**, **warp**, and **det**. If we can distribute these functions over **app** and **listn** we can derive the shape of the output. We treat **smooth** and **det** first and then turn to the much more complicated **warp**.

Recall that **smooth** takes as its first argument a Boolean flag, **flg1**, which is the "signal just previously passed" while smoothing a waveform supplied in the second argument. Some important theorems about **smooth** are shown below.

```

Theorems.

(equal (len (smooth flg lst)) (len lst)).

(implies (not (b-xor flg1 flg2))

(equal (smooth flg1 (listn n flg2))

(listn n flg2)))

(implies (and (b-xor flg1 flg2)

(not (zerop n)))

(equal (smooth flg1 (listn n flg2))

(cons 'q (listn (sub1 n) flg2))))

(implies (not (b-xor flg1 flg2))

(equal (smooth flg1

(app (listn n flg2) rest))

(app (listn n flg2)

(smooth flg1 rest))))

(implies (and (b-xor flg1 flg2)

(not (zerop n)))

(equal (smooth flg1

(app (listn n flg2) rest))

(app (smooth flg1 (listn n flg2))

(smooth flg2 rest))))

```

The first says that **smooth** does not change the **len** of the waveform. The second rule says that smoothing a list of **n** repetitions of **flg2** is a no-op if the signal just passed is Boolean-equivalent to **flg2**. I.e., no edge, no ramp. The third rule says that smoothing a list of **n** repetitions of **flg2** produces a ramp followed by **n**-1 repetitions of **flg2**, if the signal just passed is different from **flg2** and **n** is nonzero. The last two rules consider how to smooth a wave that starts with **n** repetions of **flg2** and then continues with some signals **rest**. If the signal just passed is equivalent to **flg2**, we can skip the smoothing of the initial segment and just smooth **rest**. If the signal just passed is different, we must smooth the initial segment (which, by the second rule, will produce a ramp) and then smooth **rest**, using **flg2** as signal just passed.

These theorems, and all other theorems displayed in this paper, have been proved mechanically with the NQTHM theorem prover (see box).

## The NQTHM Theorem Prover

The NQTHM logic is supported by a mechanical theorem proving system [6]. The system enforces all the rules of the logic and also knows hundreds of heuristics for proving theorems in the logic. The user interacts with the system by submitting proposed definitions and theorems. The system checks each definition for admissibility and tries to prove each theorem. When it is successful, the theorem is processed into a "rule" and stored in a data base for future use.

The system's proof attempts are driven by its heuristics and the rule base. When the system fails to find a proof, the user may guide it by submitting easier theorems that, when used as rules, lead the system to the proof it missed. To guide the theorem prover to the proof of a hard theorem the user must know a proof of the theorem and must understand how the system derives rules from theorems. In essence, the user programs the theorem prover in the art of proving particular kinds of theorems. Since the system must prove everything before using it, the user bears no responsibility for the correctness of proofs.

The system prints its proof as it goes. Users learn how to read these proofs so they know when the system is going down a blind alley. Here is the output produced for

```

Theorem . LEN-APP

(equal (len (app a b)) (plus (len a) (len b))).

Proof.

Call the conjecture *1.

Perhaps we can prove it by induction. Three inductions are

suggested by terms in the conjecture. They merge into two likely

candidate inductions. However, only one is unflawed. We will induct

according to the following scheme:

(AND (IMPLIES (NLISTP A) (p A B))

(IMPLIES (AND (NOT (NLISTP A)) (p (CDR A) B)) (p A B))).

Linear arithmetic, the lemmas CDR-LESSEQP and CDR-LESSP, and the

definition of NLISTP can be used to prove that the measure (COUNT A)

decreases according to the well-founded relation LESSP in each

induction step of the scheme. The above induction scheme leads to

two new goals:

Case 2. (IMPLIES (NLISTP A)

(EQUAL (LEN (APP A B))

(PLUS (LEN A) (LEN B)))),

which simplifies, opening up the definitions of NLISTP, APP, LEN,

EQUAL, and PLUS, to:

т.

Case 1. (IMPLIES (AND (NOT (NLISTP A))

(EQUAL (LEN (APP (CDR A) B))

(PLUS (LEN (CDR A)) (LEN B))))

(EQUAL (LEN (APP A B))

(PLUS (LEN A) (LEN B)))),

which simplifies, applying PLUS-COMMUTES1, CDR-CONS, and PLUS-ADD1,

and unfolding NLISTP, APP, and LEN, to:

That finishes the proof of *1. Q.E.D.

[0.0 0.6 0.3]

```

The system refers to rules by name, e.g., **PLUS-COMMUTES1**. **LEN-APP** is the name of the rule derived from this theorem. The time taken to do the proof is 0.6 seconds on a Sun Microsystems 3/60.

#### 7.1-D Rules about Det

The crucial rules about **det** are shown below.

The first says that **det** does not change the length of the waveform. The second says that if **flg** is Boolean (in particular, if **flg** is not 'q), then determining (listn n flg) with any oracle is a no-op, i.e., no ramps, no nondeterminacy. The third rule tells us we can distribute **det** over an **app**—but note that the theorem mentions a function we have not seen before, **oracle\***. This function was defined precisely so that we could state the distributivity rule for **det** and **app**. Recall that **det cdr**s the oracle every time it sees a 'q in its list of signals. Consider the oracle that **det** is using at the time it finishes processing **lst1** in (**app lst1 lst2**): it is the original oracle **cdred** once for every 'q in **lst1**. **Oracle\*** is defined to be just that oracle.

#### Definition.

Observe that as we apply the distribution law to a right-associated nest of **app**s, the oracle argument becomes increasingly messy as calls of **oracle\*** pile up. It turns out that we do not care. Since the oracle is arbitrary, the one returned by **oracle\*** may as well be too. None of our theorems require us to investigate the structure of the oracle.

Before leaving this section, let us get a glimpse of where we are going. Suppose we have a term such as

```

(async (send msg pl 5 13 p2) ...).

```

Note that we have underlined **send** above. This is merely intended to draw the reader's eye to the term in question. By "opening" or "expanding" the definition of **send**—that is, replacing the call of **send** by its body and simplifying the result— we can expose the fact that it generates the leading pad with **app** and **listn**. Thus, (async (send msg p1 5 13 p2) ...) becomes

```

(async [app (listn p1 t) ...] ...).

```

Note that we have used square brackets to delimit the new material. These brackets should be read as parentheses. Note that we have also underlined a new focal point. By expanding the definition of **async** we see that it is a composition of **smooth**, **warp**, and **det**,

```

[det (warp (smooth t (app (listn p1 t) ...)) ...].

```

We can distribute the **smooth** over the **app** and observe that there is no initial edge because the previous signal on the pin is assumed to be **t** and the waveform starts with a string of **t**s. Thus, our term becomes

```

(det (warp [app (listn p1 t) (smooth t ...)] ...) ...).

```

We have not yet shown how to distribute warp over app but we will. Unlike the other passes, warp may change the length of the waveform and we get

```

(det [app (listn pl t) (warp (smooth t ...) ...)] ...),

```

where p1 is some expression involving p1 and the clock parameters of warp. Finally, we can distribute the **det** over the **app** and then observe that since t is Boolean the **det** of (listn p1 t) is (listn p1 t). The result is

```

(app (listn pl t) (det (warp (smooth t ...) ...)).

```

We have succeeded in getting the initial pad of ts out of the sender, through the model (which may change its length), and into the jaws of the receiver!

## 7.1-E Rules about Warp

Recall that warp takes four clock parameters in addition to the list of signals to be processed. Those parameters are usually assumed to satisfy

#### **Definition**.

```

(clock-params ts tr w r)

=

(and (numberp ts)

(numberp tr)

(not (lessp tr ts))

(lessp tr (plus ts w))

(not (zerop w))

(not (zerop r))).

```

**7.1-E(1) The Length of Warp.** The number of signals coming out of **warp** is related to the number going in via

#### Theorem.

Note that we introduce an auxiliary function,  $\mathbf{n}^*$ , to express the relationship. We could define  $\mathbf{n}^*$  algebraically. Under the assumption (clock-params ts tr w r), we can show that ( $\mathbf{n}^*$  n ts tr w r) is  $\lfloor \frac{\mathbf{n} \times \mathbf{w} - (\mathbf{tr} - \mathbf{ts})}{\mathbf{r}} \rfloor$ . This fact will be useful when we need to bound the number of signals. But for our present purposes, it is easier to deal with a recursive definition of  $\mathbf{n}^*$  that mimics the way warp recurses.

#### **Definition**.

The number of signals in the output of warp depends on the number in the input, but not on the identities of the signals. Thus, we have chosen to make n\*'s first parameter be the number of input signals rather

than the signals themselves. We therefore have to define auxiliary functions **nendp**, **nlst+**, and **nts+** which are analogous to **endp**, **lst+**, and **ts+** except that they take the length of the waveform (and, in the case of **nlst+**, return the length of the waveform that **lst+** returns). The definitions of these functions are exactly analogous to those of their counterparts and we omit them for brevity.

The proof of the theorem that n\* is the length of warp is by an induction "unwinding" warp (see box). It requires the analogous lemmas connecting endp to nendp, lst+ to nlst+, and ts+ to nts+.

#### Theorems.

#### **Recursion and Induction**

Recursion and induction are duals. The execution of a recursive definition proceeds by decomposing composite objects into simpler components until the answer is obvious. An inductive proof shows how the truth of a proposition is preserved as one uses simple objects to construct composite ones. This duality is often useful in discovering proofs of theorems about recursive functions. By choosing an induction that "unwinds" a recursive function, you can set up a base case in which the function computes the answer trivially and an induction case in which the induction hypothesis provides exactly the information you need to know.

For example, consider the following recursive prescription for deciding if i is an even number. If i is 0, the answer is "yes"; if i is 1, the answer is "no"; otherwise recursively ask whether i-2 is even.

Now consider the proposition: "if i is even and j is even, then i+j is even."

**Proof**. Let us induct so as to unwind "i is even."

**Base Case 0.** Suppose i is 0. In this case, the proposition becomes "if 0 is even and j is even, then 0+j is even" which simplifies to the obvious truth "if j is even then j is even."

**Base Case 1**. Suppose i is 1. Here the proposition becomes "If 1 is even and ... then ..." but since 1 is not even (as the definition of even tells us) the proposition is true because its hypothesis is vacuous.

**Inductive Case.** Suppose i is not 0 and not 1. We may assume the proposition with i-2 replacing i. That is, our *Induction Hypothesis* is "if i-2 is even and j is even then i-2+j is even." We must prove

"if i is even and j is even, then i + j is even."

By the definition of even this is

"if i-2 is even and j is even, then (i+j)-2 is even."

But by arithmetic this is

"if i-2 is even and j is even, then i-2+j is even,"

which is our induction hypothesis. Q.E.D.

**7.1-E(2)** Distributing Warp over Listn. If there are no ramps in the input to warp then the waveform passes through unchanged except for its length,

```

Theorem.

```

This theorem is proved by an induction that "unwinds" (n\* n ts tr w r).

7.1-E(3) Distributing Warp over App. Warp distributes over app,

#### Theorem.

Again we see that we have to define auxiliary concepts to express the theorem. As warp processes the list of signals, weakly decreasing the length of the list each step, ts and tr increase as cycles of lengths w and r are laid out against eachother. If the list of signals is (app lstl lst2) then at some point warp will need to look at the first signal in lst2. At that point, warp's lst, ts and tr parameters will have some values,  $lst^*$ ,  $ts^*$  and  $tr^*$ .  $Lst^*$  will be some cdr of (app lstl lst2); in fact, it will be (app  $lstl^*$  lst2) where  $lstl^*$  is some cdr of lstl.  $Lstl^*$  will not necessarily be empty: it may contain many signals, just not enough to account for the entire read cycle from  $tr^*$  to  $tr^*+r$ . The functions  $lst^*$ ,  $ts^*$  and  $tr^*$  compute  $lstl^*$ ,  $ts^*$ , and  $tr^*$ .

#### **Definition**.

Observe that this definition is analogous to warp's except that instead of building up the output waveform it just returns the value of the lst parameter when the recursion terminates. The definitions of ts\* and tr\* are analogous but return the final values of the ts and tr parameters. We also define nlst\*, nts\*, and ntr\*, the versions of these three functions that operate on the length of lst rather than on lst itself (and, in the case of nlst\*, return the length of the result returned by lst\*). For example,

## Definition.

We prove the obvious theorems about these functions and their counterparts, e.g., (len (lst\* lst ts tr w r)) is (nlst\* (len lst) ts tr w r).

The proof of the distribution law for warp over app is by an induction unwinding (warp lst1 ts tr w r). The proof requires several analogous lemmas about how endp, lst+, ts+ and sig handle app, e.g.,

#### Theorems.

7.1-E(4) Warping in the Vicinity of a Ramp. When we distribute warp over (app lstl lst2) we get two warp expressions. The first one is simply the warp of lstl. But the second one, which intuitively is the warp of lst2, actually depends on what happens as warp crosses the "gap" between lstl and lst2. An example makes this clear.

Suppose that the input waveform is (app (listn n t) rest). The distribution law tells us that the warp is

Of course, we know that (warp (listn n t) ts tr w r) is (listn (n\* n ts tr w r) t) and so the initial part of the emerging waveform is known. But we cannot yet see how *rest* emerges because we have not driven warp across the gap. The last few remaining signals in the first part must be processed in conjunction with the first few signals of *rest*. One read cycle spans this gap, the one that starts at the time computed by (tr\* (listn n t) ts tr w r).

Because warp is used exclusively after smooth (and the use of the fool's edge rule), the first signal after a string of ts (or fs) will be a ramp. That ramp will necessarily participate in the reconciliation of the signals arriving during the read cycle identified by tr\*. It may influence several read cycles, causing warp to produce a string of ramps. If w and r are within a factor of 2 of eachother, i.e., neither cycle time is long enough to completely contain two cycles of the other processor, then a single ramp coming into warp can produce 1, 2, or 3 ramps coming out. We illustrate the three possibilities in Figure 10.

In Figure 10 we show how warp passes through the ramp in (app (listn n t) (cons 'q rest)) in three different contexts involving how the two series of cycles overlap. Recall that the read cycle that starts at tr\* is, by definition, the first read cycle that is influenced by the ramp. That cycle may also be influenced by the last few signals in the first part of the incoming waveform, in this case, the last few ts of (listn n t). Lst\* is, by definition, those last few signals— the signals preceding the ramp that must be reconciled with the ramp. Ts\* is the arrival time of the first signal in lst\*.

In Configuration A, the read cycle that starts at tr\* entirely consumes the ramp. In the picture, we show lst\* as containing one signal, the last one preceding the ramp. This is just one of two possibilities. It is

Figure 10: Warping Across a Ramp

possible for lst\* to be empty (i.e., for the signals preceding the ramp to determine a whole number of read cycles). In Configuration B, the read cycle at tr\* splits the ramp so that it falls into two read cycles. Again, our picture shows one of several possibilities regarding lst\*: it contains the last two signals preceding the ramp here, but if the reader's cycle time were shorter it could contain only the last signal or no signals. Finally, in Configuration C, the read cycles fall so that the one after tr\* is entirely consumed by the ramp. If the read cycle can be arbitrarily shorter than the write cycle, an arbitrary number of 'qs might emerge from warp due to a single ramp. But in our reusable theory about warp we chose to limit our attention to processors whose cycle times are within a factor of 2 of eachother.

Once warp has gotten past the ramp, how many signals remain in rest to process? In the three configurations illustrated, the first signal in rest is always involved in the determination of the first read cycle after passing the ramp. But this need not be the case. To see why, consider Configuration B and slide the reader's cycles down about half a write cycle, so that lst\* now contains only one element and the first signal of rest is consumed in emitting the second 'q. Under our "factor of 2" assumption, there are only two cases: no signals from rest are consumed in passing the ramp or one signal is consumed.

The observations just made can be combined with our previously proved theorems about warp, app, and listn to derive the following extremely useful rule.

#### Theorem.

The functions nq, dw, ts, and tr will be discussed below, but first let us consider this theorem. It addresses itself to warping across a ramp in the general case where the ramp is preceded by an arbitrarily long stable signal. The clock rates must be within a factor of 2 and there must be at least one signal after the ramp. The theorem tells us that the emerging signal is composed of three parts. First, we get the warped image of the long stable signal (possibly stretched or shrunk), i.e., (listn (n\* n ts tr w r) flg). Then we get a certain number of ramps, (listn (nq n ts tr w r) 'q), where the function nq tells us how many. Nq, defined below, is either 1, 2, or 3. Finally we get the warped image of some cdr of rest. The function dw determines how many signals are chopped off of rest and its value is either 0 or 1. The values of ts and tr used while warping the rest are computed by the functions ts and tr. This is a beautiful result because it formalizes and makes precise the claim that warp stretches or shrinks the waveform without altering its basic shape.

The proof of the above theorem is tedious but straightforward, given our prior results. The general theorem for warping an app applies and, together with the theorem for warping a listn, explains the (listn (n\* n ts tr w r) flg) of the result. We then are left with warping across the ramp and into rest. We do that entirely with case analysis as suggested by Figure 10.

1)

Summarizing, the nlst\*, nts\*, and ntr\* expressions in nq determine the parameters warp has when it first has to process the ramp, and nqg takes those parameters and does a case analysis to determine how many 'qs are emitted before getting past the ramp.

The definitional styles of **dw**, **ts**, and **tr** are identical and we display them without comment. Of course, the case analysis in each is unique.

```

Definition.

Definition.

(dw n ts tr w r)

(dwg k ts tr w r)

(dwg (nlst* n ts tr w r)

(if (lessp (plus r tr)

(nts* n ts tr w r)

(plus ts w (times k w)))

(if (lessp (plus r r tr)

(ntr* n ts tr w r)

(plus ts w w

wr)

(times k w)))

0 1)

(if (equal (plus r tr)

(plus ts w (times k w)))

(if (and (lessp (plus ts w (times k w))

(plus r tr))

(lessp (plus r tr)

(plus ts w w

(times k w))))

(if (lessp (plus r tr)

(plus ts w w (times k w)))

0 1))))

Definition.

Definition.

(ts n ts tr w r)

(tsg k ts tr w r)

=

(tsg (nlst* n ts tr w r)

(plus ts

(nts* n ts tr w r)

(times w k)

(ntr* n ts tr w r)

(times w (dwg k ts tr w r)))

wr)

Definition.

Definition.

(tr n ts tr w r)

(trg k ts tr w r)

(trg (nlst* n ts tr w r)

(plus tr (times r (nqg k ts tr w r)))

(nts* n ts tr w r)

(ntr* n ts tr w r)

```

Of course, the accuracy of this case analysis is questionable until the theorem showing how warp processes a ramp is proved.<sup>7</sup>

It should be observed that (clock-params ts tr w r) implies (clock-params (ts n ts tr w r) (tr n ts tr w r), provided n is numeric and w and r are within a factor of 2 of eachother.

This completes our development of the reusable theory of async.

<sup>&</sup>lt;sup>7</sup>Indeed, we did the analysis incorrectly many times before finally producing the correct one.

## 7.2 Bounding Certain Functions

The reusable theory introduces the functions nq, dw, and n\* which are used in the determination of the lengths of various parts of the received waveform. It is useful in our coming proof to establish bounds for these functions.

## 7.2-A Bounding nq

Nq is the width of the nondetermistic region caused by warping a single ramp. From the definition of nq and its subfunction nqg it is obvious that  $1 \le (nq \ n \ ts \ tr \ w \ r) \le 3$ .

## 7.2-B Bounding dw

**Dw** is the number of signals consumed by **warp** immediately after a single ramp. From the definition of **dw** and its subroutine **dwg**, it is obvious that  $0 \le (\text{dw n ts tr w r}) \le 1$ .

## 7.2-C Bounding n\*

N\* is the length of the result of warping a horizontal region of the waveform. That is, (warp (listn n flg) ts tr w r) is (listn (n\* n ts tr w r) flg). Under the assumption (clock-params ts tr w r), we can show that (n\* n ts tr w r) is  $\lfloor \frac{n \times w - (tr - ts)}{r} \rfloor$ . This algebraic expression of n\* can be proved by an induction unwinding (n\* n ts tr w r) and using properties of nendp and nts+ and natural number arithmetic.

We are interested in bounds on  $n^*$ . However, to derive interesting bounds we must impose some constraints on the cycle times  $\mathbf{w}$  and  $\mathbf{r}$  since otherwise ( $n^*$  n ts tr  $\mathbf{w}$  r) can be arbitrarily larger or smaller than  $\mathbf{n}$ . Because we are headed toward the BPM18 theorem, where we assume (rate-proximity  $\mathbf{w}$  r), i.e., that 18 ticks of length  $\mathbf{w}$  is between 17 and 19 ticks of length  $\mathbf{r}$ , we investigate the bounds on  $\mathbf{n}^*$  in that context.

The following two theorems are fairly straightforward applications of the algebraic identity above and the usual properties of natural number arithmetic.

Roughly speaking, if  ${\bf w}$  and  ${\bf r}$  are in proximity and  ${\bf n}{<}18$ , then

```

n-2 \le (n* n ts tr w r) \le n.

```

In a truly general reusable theory of **async** we would derive bounds theorems that did not refer to the particular notion of proximity used in the intended application.

## 7.3 Scanning across a Ramp

Using the general theory of **async** we will be able to derive the form of the wave reaching the receiver. We now consider how the receiver reacts.

Because of

That is, the receiver simply ignores the leading signals it is scanning past.

Eventually then the receiver will be confronted with a ramp of some arbitrary length followed by a region of parity opposite that being scanned. That is, the receiver will be confronted with a nondeterministically defined edge. We need to say how **scan** deals with such an edge. To state the desired lemma we have to define two new auxiliary functions, **no** and **scan-oracle**. Their definitions are obvious from the lemma we prove,

```

Theorem.

```

Observe that on the left-hand side of the conclusion, scan is scanning past flg1 and has encountered a ramp of length nq followed by a nonempty region of parity opposite that of flg1. Where does scan stop? The right-hand side tells us: it stops and returns a ramp of length (no flg1 nq oracle) followed by everything past the ramp. The term (no flg1 nq oracle) is defined to be the number of cycles in a ramp of length nq after the first one at which oracle differs from flg1. It is an easy consequence of the definition of no that  $0 \le (no flg1 nq oracle) \le nq$ . (Scan-oracle flg1 nq oracle) is the remaining tail of oracle as of the cycle in question.

Of particular interest is the length of the waveform scan returns: it is just (no flg1 nq oracle) + n + (len rest).

## 7.4 Finding the Sampling Point