Copyright

by

Nina Amla

2001

### Efficient Model Checking for Timing Diagrams

by

Nina Amla, B.E, M.S.

#### Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### **Doctor of Philosophy**

### The University of Texas at Austin

May 2001

### Efficient Model Checking for Timing Diagrams

Approved by Dissertation Committee:

To my parents

### Acknowledgments

The time I spent at the University of Texas and Austin has been influenced by many. I am indebted to my advisor Allen Emerson. Allen provided a challenging and rewarding milieu; he has taught me that research is about clarity of thought leading to precision in exposition.

The two summers I spent at Bell Labs influenced this thesis immeasurably. Bob Kurshan made this possible. Bob has had a profound impact on my research perspective. I owe much to Jayadev Misra for his constant encouragement, technical insights and for giving crucial advice when I needed it most. I am grateful to Adnan Aziz for the many productive discussions and for being so generous with his time. I thank Mohamed Gouda and Aloysius Mok for serving on my committee and for the useful feedback.

Kedar Namjoshi has been a superb mentor, both officially and unofficially, and a good friend. Our association goes back to the first projects we collaborated on in Allen's class and continues to this day. Thanks to Richard Trefler, first a wonderful and supportive friend, and now a close collaborator.

To Phoebe Weidmann, my closest friend, thank you for everything. I value the friendship of John Havlicek, Pete Manolios and Natasha Sharygina and have enjoyed our many discussions on technical and non-technical matters. I thank Emery Berger, Emilio Camahort, Esra Erdem, Sergei Gorinsky, John Gunnels, Sam Guyer, Mike Hewett, Subramanian Iyer, Rajeev Joshi, Vineet Kalhon, Lyn Pierce, Jack Sarvela, Jun Sawada, Vasilis Samoladas, Yannis Smaragdakis and Thomas Wahl for the great company and memories from graduate school. Brian Victor, whom I have known the longest, thanks for for being such a dear friend.

None of this would have been possible without the love and encouragement of my family. My mother, a teacher all her life, provided me with a ready role model. Thanks to my father, my guide at all times. I thank my sister Anita for her unflagging support and her company these last years in Austin. Vanya I thank for being my anchor and best friend. Mukund, thanks for having enough ambition, patience and drive for the two of us. Lovable Laila and Bert, thanks for always reminding me that happiness is as accessible as a walk around town lake.

Acknowledgments have to stop somewhere: 'What do I have that I have not received?'

NINA AMLA

The University of Texas at Austin May 2001

#### Efficient Model Checking for Timing Diagrams

Publication No. \_\_\_\_\_

Nina Amla, Ph.D. The University of Texas at Austin, 2001

Supervisor: E. Allen Emerson

Non-terminating systems that continually interact with their environment are called *reactive*. These types of systems are commonplace and are largely acknowledged to be hard to validate using conventional techniques. In a landmark paper, Pnueli argued that temporal logics are an effective way to reason about the correctness of reactive systems. *Model checking* is a formal technique that efficiently determines if a reactive system satisfies a temporal logic specification. In the last decade, model checking has been used extensively to verify complex hardware and software systems. However, in practice, model checking suffers from a phenomenon called *state explosion*, where the global state transition graph may be exponential in the number of subcomponents in the system. The state explosion problem severely limits the size of the systems that one can model check automatically. Another obstacle is that formal specification methods, based on temporal logic or automata, are largely unknown in the design community. This dissertation addresses both these issues by introducing a visual notation that is already used in the informal specification of hardware systems and by providing efficient model checking algorithms for these specifications.

The first part of the dissertation presents, Regular Timing Diagrams (RTDs), an expressive notation for specifying the temporal behavior of asynchronous systems. RTDs have a formal syntax and a simple and precise semantics that correspond to informal usage. We have developed efficient algorithms to translate RTDs into automata on infinite strings ( $\omega$ -automata). We present decompositional model checking algorithms, that exploit the fact that RTDs can be cleanly decomposed into their constituent parts. These polynomial-time algorithms are a significant improvement over previous monolithic algorithms that are exponential in the worst case.

The second part of the dissertation introduces Synchronous Regular Timing Diagrams (SRTDs) that are used to specify the behavior of synchronous systems. The model checking algorithms developed for SRTDs are linear in the size of the diagram. A tool, based on this framework, called RTDT, which allows a user to graphically create SRTD specifications and translate them into automata, is also part of this dissertation. RTDT has been used successfully in conjunction with the model checking tool *COSPAN* to verify that Lucent Technologies PCI Interface Core satisfied actual diagrams found in the PCI Local Bus specification.

The final part of the dissertation offers a way to cope with state explosion by employing a proof technique called *compositional reasoning* that reduces reasoning about the entire system to reasoning about individual components. The *assume-guarantee* paradigm, is a type of compositional reasoning, where each component guarantees properties based on assumptions made about the other components. Applying these proof rules, however, is not automatic; it requires non-trivial human effort to decompose a property into sub-properties and to then derive the appropriate assumptions. Additionally, such proof rules are generally not complete and must be applied differently for safety and liveness properties. A new sound and complete assume-guarantee proof rule is developed in this dissertation which can be applied to both safety and liveness properties. When the property is an SRTD, this rule can be applied in a fully automatic manner by using the fact that SRTDs have a natural decomposition into assume-guarantee pairs. The application of this rule to Lucent's PCI Core and other case studies yielded substantial reductions in the space and time required for model checking.

In summary, this dissertation introduces an alternative and visual way of specifying temporal properties, which makes model checking more accessible to the non-expert user. Furthermore, this work addresses the state explosion problem by presenting efficient model checking algorithms and a general assume-guarantee proof methodology that can be applied in a fully automated manner to specifications in this form.

# Contents

| Ackno   | wledgments                           | $\mathbf{v}$ |

|---------|--------------------------------------|--------------|

| Abstra  | act                                  | vii          |

| List of | Tables                               | xiii         |

| List of | Figures                              | xiv          |

| Chapt   | er 1 Introduction                    | 1            |

| 1.1     | Regular Timing Diagrams              | 4            |

| 1.2     | Synchronous Regular Timing Diagrams  | 5            |

| 1.3     | Assume-Guarantee Reasoning for SRTDs | 6            |

| 1.4     | The RTDT Tool                        | 7            |

| Chapt   | er 2 Background                      | 8            |

| 2.1     | Automata on Finite Strings           | 8            |

| 2.2     | Automata on Infinite Strings         | 9            |

| 2.3     | Linear Temporal Logic (LTL)          | 10           |

| 2.4     | Model Checking                       | 11           |

| 2.5     | Timing Diagrams                      | 13           |

| Chapte | er 3 Regular Timing Diagrams                                   | 16        |

|--------|----------------------------------------------------------------|-----------|

| 3.1    | Introduction                                                   | 16        |

| 3.2    | Regular Timing Diagrams - Syntax and Semantics                 | 19        |

|        | 3.2.1 Syntax                                                   | 19        |

|        | 3.2.2 Semantics                                                | 23        |

| 3.3    | Translation Algorithms                                         | 28        |

|        | 3.3.1 Translating RTDs with Weak Iterative Semantics $\ldots$  | 29        |

|        | 3.3.2 Translating RTDs with Strong Iterative Semantics         | 33        |

| 3.4    | Decompositional Model Checking                                 | 36        |

| 3.5    | Applications                                                   | 39        |

| 3.6    | Related Work and Conclusions                                   | 42        |

| Chapte | er 4 Synchronous Regular Timing Diagrams                       | <b>45</b> |

| -      |                                                                |           |

| 4.1    | Introduction                                                   | 45        |

| 4.2    | Synchronous Regular Timing Diagrams                            | 47        |

|        | 4.2.1 Syntax                                                   | 48        |

|        | 4.2.2 Semantics                                                | 53        |

| 4.3    | Model Checking SRTDs                                           | 56        |

|        | 4.3.1 Translation Algorithm for Overlapping Semantics $\ldots$ | 57        |

|        | 4.3.2 Translation Algorithm for Non-overlapping Semantics .    | 61        |

|        | 4.3.3 Model Checking                                           | 66        |

|        | 4.3.4 Decompositional Model Checking                           | 67        |

| 4.4    | Applications                                                   | 69        |

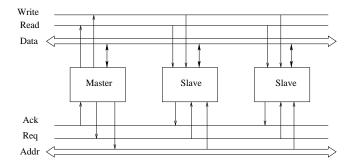

|        | 4.4.1 Master-slave Memory System                               | 69        |

|        | 4.4.2 Lucent's PCI Synthesizable Core                          | 72        |

| 4.5    | Related Work and Conclusions                                   | 75        |

| Chapt  | er 5 Compositional Reasoning with SRTDs          | 78  |

|--------|--------------------------------------------------|-----|

| 5.1    | Introduction                                     | 78  |

| 5.2    | Assume-Guarantee Based Compositional Reasoning   | 80  |

|        | 5.2.1 Preliminaries                              | 80  |

|        | 5.2.2 Compositional Reasoning Rules              | 88  |

| 5.3    | Compositional reasoning with Timing Diagrams     | 104 |

|        | 5.3.1 Translating SRTDs into Automata            | 107 |

|        | 5.3.2 Automatic Construction of Helper Processes | 107 |

|        | 5.3.3 Compositional Model Checking of SRTDs      | 111 |

| 5.4    | Applications                                     | 111 |

|        | 5.4.1 Memory Access Controller                   | 112 |

|        | 5.4.2 Lucent's PCI Synthesizable Core            | 113 |

| 5.5    | Related Work and Conclusions                     | 118 |

| Chapt  | er 6 The Rtdt Tool                               | 120 |

| 6.1    | Introduction                                     | 120 |

| 6.2    | RTDT Design Issues                               | 121 |

| 6.3    | The RTDT Editor                                  | 122 |

| 6.4    | The RTDT Translator                              | 124 |

|        | 6.4.1 Generating the Automata                    | 125 |

|        | 6.4.2 Generating the Helper Processes            | 127 |

| 6.5    | Related Work and Conclusions                     | 127 |

| Chapt  | er 7 Conclusions                                 | 130 |

| Biblio | graphy                                           | 133 |

| Vita   |                                                  | 144 |

# List of Tables

| 3.1 | Verification Statistics for Master-Slave Design                       | 42  |

|-----|-----------------------------------------------------------------------|-----|

| 4.1 | Verification Statistics for Master-Slave Design                       | 72  |

| 4.2 | Verification Statistics for Lucent's Synthesizable PCI Core $\ . \ .$ | 75  |

| 5.1 | Verification Statistics for Memory Access Controller Design           | 114 |

| 5.2 | Verification Statistics for PCI Synthesizable Core Design             | 116 |

# List of Figures

| 2.1  | (a) Ambiguous Diagram (b) Unambiguous Diagram                           | 14 |

|------|-------------------------------------------------------------------------|----|

| 3.1  | (a) Ambiguous RTD (b) Unambiguous RTD                                   | 20 |

| 3.2  | RTD $T$ Annotated with Symbolic Points $\ldots \ldots \ldots \ldots$    | 22 |

| 3.3  | RTD Annotated with Points                                               | 25 |

| 3.4  | Ambiguous RTD $T$                                                       | 27 |

| 3.5  | RTD T Annotated with Unordered Events $\ldots \ldots \ldots$            | 29 |

| 3.6  | Automata for (a) Waveform $A$ (b) Waveform $B$ (c) Sequential           |    |

|      | Dependency                                                              | 30 |

| 3.7  | $\omega$ -NFA $\mathcal{A}_{\overline{T}}$ for Weak Iterative Semantics | 31 |

| 3.8  | <i>NFA</i> $\mathcal{A}_{de}$ for Events $d$ and $e$ in Figure 3.5      | 34 |

| 3.9  | Master-Slave Architecture                                               | 39 |

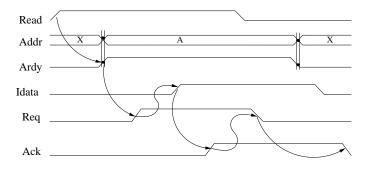

| 3.10 | RTD for the Memory Read Cycle                                           | 40 |

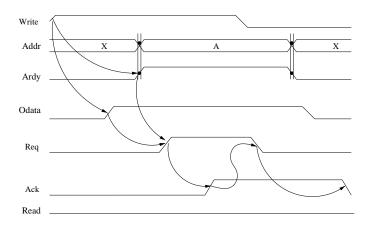

| 3.11 | RTD for the Memory Write Cycle                                          | 41 |

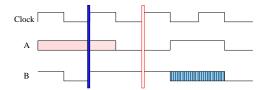

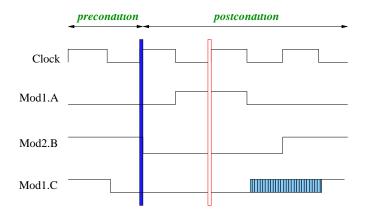

| 4.1  | Annotated Synchronous Regular Timing Diagram                            | 49 |

| 4.2  | SRTD with an Overlapping Precondition                                   | 56 |

| 4.3  | SRTD with Don't-Care Values in the Precondition                         | 58 |

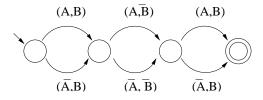

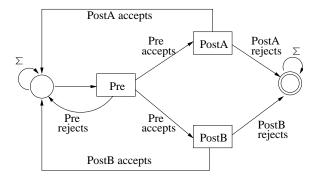

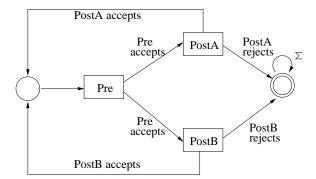

| 4.4  | The DFA $A_{pre}$ for the Overlapping Semantics                         | 58 |

| DFA's for the Postcondition of Waveforms $A$ (top) and $B$ (bottom)                              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\omega$ -NFA for the Complement of the SRTD in Figure 4.3                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

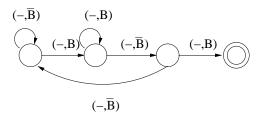

| The DFA $A_{pre}$ for Non-Overlapping Semantics                                                  | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\omega\text{-}\mathit{NFA}\ A_{\overline{T}}$ for the Complement of the SRTD in Figure 4.3 $$ . | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

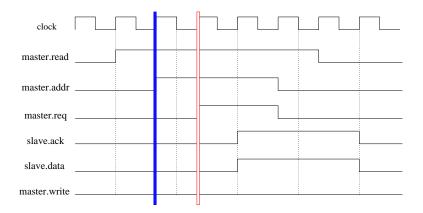

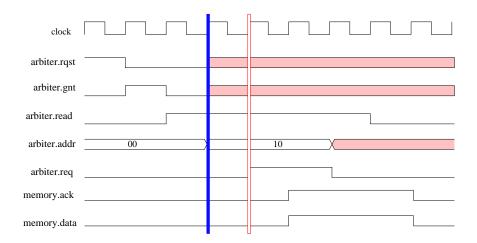

| SRTD for the Read Transaction                                                                    | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

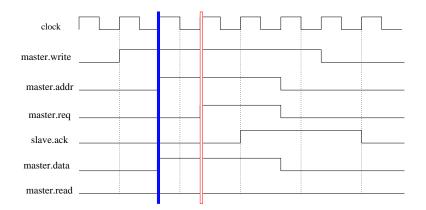

| SRTD for the Write Transaction                                                                   | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

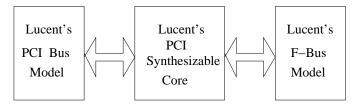

| Block Diagram of Lucent's F-Bus with PCI Core                                                    | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

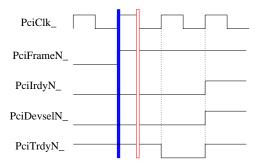

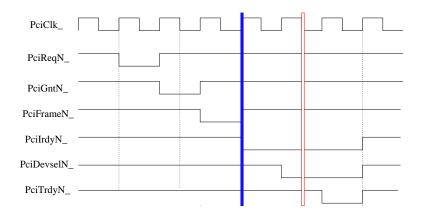

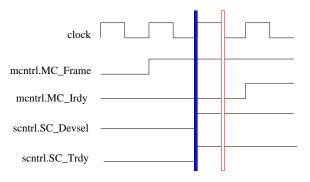

| An SRTD Burst Property for the PCI Bus                                                           | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SRTD for the Non-burst Transaction of the PCI Bus $\ . \ . \ .$                                  | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

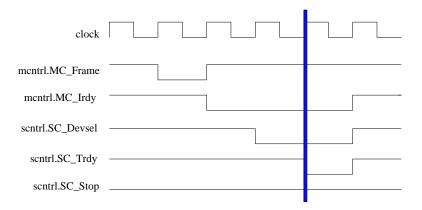

| Augmented Synchronous Regular Timing Diagram                                                     | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Read Transaction for the Memory Access Controller                                                | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Non-burst Property for PCI Core                                                                  | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Burst Property for PCI Core                                                                      | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Editing and Viewing Screens                                                                      | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Help Screen                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                  | $\omega$ -NFA for the Complement of the SRTD in Figure 4.3The DFA $A_{pre}$ for Non-Overlapping Semantics $\omega$ -NFA $A_{\overline{T}}$ for the Complement of the SRTD in Figure 4.3SRTD for the Read TransactionSRTD for the Write TransactionSRTD for the Write TransactionBlock Diagram of Lucent's F-Bus with PCI CoreAn SRTD Burst Property for the PCI BusSRTD for the Non-burst Transaction of the PCI BusSRTD for the Non-burst Transaction of the PCI BusSRTD for the Non-burst Transaction of the PCI BusSRTD synchronous Regular Timing DiagramRead Transaction for the Memory Access ControllerNon-burst Property for PCI CoreBurst Property for PCI CoreSurst Property for PCI CoreSurst Property for PCI Core |

## Chapter 1

## Introduction

The class of systems that are non-terminating and interact with their environment continuously are called *reactive systems* [HP85]. Operating systems, hardware controllers and network routers are well known examples of reactive systems. It is generally acknowledged that it is hard to verify the correctness of reactive systems using conventional validation techniques like testing and simulation. Moreover, formal techniques developed for terminating sequential programs are not applicable to reactive systems. Pnueli [Pnu77], proposed the use of temporal logic as a effective way to reason formally about the correctness of reactive systems. Model checking, introduced by Clarke and Emerson [CE81] (and independently by Quielle and Sifakis [QS82]), is a fully automated procedure that efficiently decides if a reactive system satisfies a temporal specification. The specification may be either a formula in a temporal logic, like CTL (Computation Tree Logic) [EH82] or LTL (Linear Temporal Logic) [Pnu77], or, specified as an automaton on infinite strings [VW86, Kur94]. The survey paper by Emerson [Eme91] presents a comparison of these specification methods and others in terms of efficiency and expressiveness.

Model checking has been applied successfully in the verification of many industrial hardware and software systems. In fact, model checking and other formal techniques are currently used in the design process at companies such as AMD, IBM, Intel and Motorola. Model checking, however, suffers in practice due to the state explosion problem: if system M is defined as the parallel composition of n sub-components, the global state transition graph may be exponential in n. This imposes severe limitations on the size of the systems that can be verified. As a result, ameliorating the state explosion problem is at the forefront of research in this area. Recently developed techniques, like symmetry reduction (cf. [ES93]) and compositional reasoning (cf.  $[dRdBH^+99]$ ) that exploit the structure of the system, have been successful in coping with the state explosion problem. In *composi*tional reasoning, one avoids reasoning directly about a system composed of many sub-components by decomposing the property and proving systematically that sub-components satisfy these sub-properties. A good survey of the main contributions in this area can be found in [dRLP97]. The most well studied compositional reasoning technique is Assume-quarantee reasoning [MC81, Jon81, Pnu85, Sta85, Kur87, CLM89, AL95, AH96, McM97, McM99] where one uses assumptions made about the environment to satisfy the requirements of a compositional proof. While this type of reasoning has been applied in practice [McM98, HQR98] there are, however, many difficulties in actually applying these "circular" proof rules. Firstly, many proof rules apply only to safety properties and restricted types of processes and/or temporal logic. Secondly, it has been shown [NT00] that many of these proof rule are not complete. Finally, decomposing the property and deriving the auxiliary assumptions must be done manually.

Another obstacle to the widespread use of model checking is the complex nature of the specification languages. Such specifications, based on temporal logics or automata, are not well understood in the design community. Visually intuitive specification methods – which are consistent with the users own notational conventions – provide an alternative way to specify temporal behavior. The inclusion of such notations into existing model checkers would make them accessible to the non-expert user and facilitate the wider application of model checking.

This dissertation addresses both issues: the incorporation of common specification methods and the state explosion problem. We introduce formal graphical specification languages, for both synchronous and asynchronous systems, which are based on an informal notation called *timing diagrams*. Timing diagrams are already widely used in the specification of hardware systems. Polynomial-time non-compositional and assume-guarantee style compositional model checking algorithms for these diagrams are presented.

In the first part of this dissertation, we will introduce a visual specification notation, that corresponds to regular languages, called Regular Timing Diagrams (RTDs). RTDs are an effective way to specify asynchronous behavior. We provide model checking algorithms, based on the automata-theoretic approach, that are polynomial in the size of the RTD specification. Next, we will present Synchronous Regular Timing Diagrams (SRTDs) that are tailored for synchronous systems. The model checking algorithms for SRTDs are linear in the size of both the system and the SRTD specification. The final part of the dissertation describes a sound and complete assume-guarantee proof rule that can be applied to both safety and liveness properties. More interestingly, we can use this rule in a fully automated manner to properties specified in SRTD notation. These algorithms have been implemented in a tool called RTDT which is described in the dissertation.

Much of the work done for this dissertation has been published in the following papers: [AE98], [AEN99], [AEKN00], [AENT01] and [AEKN01]. The rest of this section contains a more in-depth discussion of the problems involved and justifications for our methods.

#### **1.1 Regular Timing Diagrams**

Asynchronous timing diagrams are used to specify the behavior of asynchronous handshaking protocols like bus arbitration and memory access. The key attribute of an asynchronous timing diagram is the absence of explicit timing with respect to a global system clock. We introduce a class of timing diagrams for asynchronous systems, called *Regular Timing Diagrams* (RTDs), that have a formal syntax and semantics. The key observation that leads to efficient model checking is that timing diagrams are compositional (conjunctive) in nature. This can be visualized informally as the waveforms acting independently and only interacting with other waveforms through a dependency. Rather than build a single, monolithic  $\omega$ -NFA (Non-deterministic Finite state Automaton on infinite strings) or a temporal logic formula that corresponds to the entire diagram, we decompose the diagram into properties of isolated waveforms and their interactions. This results in a conjunction of simple properties that can be conveniently represented by a succinct  $\omega$ -NFA for the complement of the diagram. The resulting  $\omega$ -NFA can be used as the property in the language containment paradigm to yield a model checking algorithm that is linear in the system size and polynomial in the size of diagram. We describe how these

algorithms can be applied, with the model checker VIS [BHSV<sup>+</sup>96], to verify a master-slave memory system. This work was published in [AE98, AEN99] and is described in Chapter 3.

#### **1.2 Synchronous Regular Timing Diagrams**

It is more common, however, to have a *synchronous* timing specification where the changes along a signal waveform are bound to a global system clock. The encoding of such synchronous properties as RTDs introduces a large number of dependency edges between each transition of the clock and each waveform, resulting in RTDs that are visually cluttered and increasing the complexity of model checking. The Synchronous Regular Timing Diagram (SRTD) notation is, therefore, tailored to describe synchronous timing specifications in a visually clean manner. More importantly, we exploit the regular structure of SRTDs to provide model checking algorithms that are more efficient than that for RTDs. We present decompositional translation algorithms that construct  $\omega$ automata of size that is linear in the size of the SRTD (compared with a polynomial size complexity in [AEN99] for RTDs). This algorithm has been implemented in a tool – the Regular Timing Diagram Translator (RTDT) – which is described in Chapter 6. RTDT has been used in conjunction with the model checker COSPAN [HHK96] to verify timing diagram properties of two systems: a synchronous master-slave system and Lucents' PCI Interface Core [BL96]. This work is presented in Chapter 4 and is based on results presented in [AEKN00].

#### **1.3** Assume-Guarantee Reasoning for SRTDs

In this work we present a new rule for assume-guarantee reasoning which generalizes several earlier proof rules (cf. [Pnu85, AL95, AH96, McM99, NT00]) by removing the sources of incompleteness in some of these rules, by using processes instead of temporal logic formulas as specifications, and by allowing more general forms of process definition and composition. The new rule extends the naïve assume-guarantee proof rule with an additional check for soundness. As the new rule does not discriminate between processes and properties, it fits in well with a top-down approach to designing systems. We show that this new rule is complete, to the extent that if the composed system satisfies a property, then it also satisfies the property with the new rule.

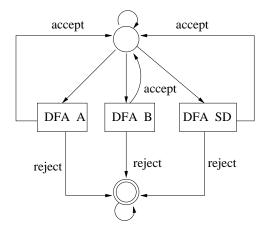

Next, we explore the benefits of applying this rule in the case where the property is specified as an SRTD. We show that not only is task decomposition a relatively simple matter for SRTDs, but also that it is possible to automatically generate assumptions directly from the specification. Furthermore, we identify a class of SRTDs for which the soundness check of the rule is always satisfied, and for which the generation of the assumptions is efficient. This leads to a model checking process that is efficient (linear in the size of the diagram and the system). These algorithms have been incorporated into RTDT, which uses *COSPAN* to discharge model checking subgoals. We report here on its application to a memory controller and a PCI Interface Core; in both cases, we obtain substantial reduction in the space used for model checking. This research was published in [AENT01] and is described in Chapter 5.

### 1.4 The RTDT Tool

The Regular Timing Diagram Translator (RTDT) tool provides a user-friendly graphical editor to create and edit SRTDs and a translator that implements the compositional and non-compositional model checking algorithms. RTDT forms a formal and efficient timing diagram interface to the model checker *COSPAN*. The key features of RTDT are described in Chapter 6 and has appeared in [AEKN00, AEKN01].

### Chapter 2

### Background

In this Chapter, we will present some background on automata theory, temporal logic, model checking and timing diagrams.

#### 2.1 Automata on Finite Strings

**Definition 0 (Nondeterministic Finite state Automata (NFA))** An automaton on finite strings  $\mathcal{A}$  is a tuple  $(\Sigma, Q, \delta, Q^0, F)$ , where  $\Sigma$  is finite input alphabet, Q is a finite set of states,  $\delta \subseteq Q \times \Sigma \times 2^Q$  is a transition relation,  $Q^0 \subseteq Q$  is a non-empty set of start states, and  $F \subseteq Q$  is a set of accepting states.

The automaton  $\mathcal{A}$  is deterministic (DFA) if  $|Q^0|=1$  and  $|\delta(q,a)| \leq 1$ , for all  $q \in Q$  and  $a \in \Sigma$ . A run r of  $\mathcal{A}$  on a finite string  $w = a_0, a_1, ..., a_{n-1} \in \Sigma^*$ is a sequence of states  $q_0, q_1, ..., q_n$  in Q such that  $q_0 \in Q^0$ , and  $q_{i+1} \in \delta(q_i, a_i)$ for  $O \leq i < n$ . A run is accepting if  $q_n \in F$ . The language of  $\mathcal{A}$ , denoted  $\mathcal{L}(\mathcal{A})$ , is the set of finite strings that are accepted by  $\mathcal{A}$ . Automata on finite strings are closed under union, intersection and complementation [RS59]. Deterministic automata can be complemented easily by complementing the acceptance condition. However, complementing a nondeterministic automaton involves determinization and results in a construction that is exponential.

#### 2.2 Automata on Infinite Strings

**Definition 1 (Nondeterministic**  $\omega$ -automata ( $\omega$ -NFA )) An automaton on infinite strings  $\mathcal{A} = (\Sigma, Q, \delta, q^0, \Phi)$  has a finite input alphabet  $\Sigma$ , finite state set Q, transition relation  $\delta \subseteq Q \times \Sigma \times 2^Q$ , start state  $q_0$  and acceptance condition  $\Phi$ .

A run r of  $\mathcal{A}$  on input x in  $\Sigma^{\omega}$  is an infinite sequence of states of  $\mathcal{A}$ , where  $q_0$ is an initial state, and for each i,  $(q_i, x_i, q_{i+1}) \in \delta$ .  $\mathcal{A}$  accepts x if some run r on x satisfies the acceptance condition  $\Phi$ .

An  $\omega$ -automaton is deterministic  $(\omega$ -DFA) if  $|\delta(q, x)| \leq 1$  for all states  $q \in Q$  and symbols  $x \in \Sigma$ . A run r is accepting by the Büchi acceptance criteria if there is an accepting state that repeats in r infinitely often. In this dissertation, we consider  $\Phi$  to be Büchi acceptance.

Büchi automata are closed under union, intersection [Cho74] and complementation [Buc62]. The constructions are, however, much more involved than those for the automata on finite strings. The complexity of complementation is singly exponential [SVW87].

**Definition 2** ( **Dual Run Automata** ( $\forall FA$ ))  $A \forall FA$  on infinite strings  $\mathcal{A} = (\Sigma, Q, \delta, q_0, \Phi)$  has a finite input alphabet  $\Sigma$ , finite state set Q, transition

relation  $\delta \subseteq Q \times \Sigma \times Q$ , start state  $q_0$  and acceptance condition  $\Phi$ .

A run r of  $\mathcal{A}$  on input x in  $\Sigma^{\omega}$  is an infinite sequence of states of  $\mathcal{A}$ , where  $r_0$  is an initial state, and for each i,  $(r_i, x_i, r_{i+1}) \in \delta$ .  $\mathcal{A}$  accepts x by "dual-run" acceptance according to  $\Phi$  iff every run r on x satisfies  $\Phi$ .

The complement of the language accepted by a  $\forall FA \ \mathcal{A}$  is accepted by an  $\omega$ -NFA  $\overline{\mathcal{A}}$ , that has the identical structure but a complemented acceptance condition. This property is formalized in the following theorem. We define  $\mathcal{L}_{NFA}(\mathcal{A})$  as the language accepted by a  $\exists$ -acceptance criteria and  $\mathcal{L}_{\forall FA}(\mathcal{A})$  as the language accepted by a  $\forall$ -acceptance criteria.

**Theorem 0** ([MP87, Var87]) For any  $\forall FA \ \mathcal{A}, \ \neg \mathcal{L}_{\forall FA}(\mathcal{A}) = \mathcal{L}_{NFA}(\overline{\mathcal{A}}).$

#### 2.3 Linear Temporal Logic (LTL)

We will present the syntax and semantics of Linear Temporal Logic (LTL) [Pnu77]. Formulas of LTL are built from a set of atomic proposition  $\mathcal{AP}$ . An LTL formula is defined as follows:

- 1. If  $f \in \mathcal{AP}$  then f is a formula.

- 2. If both f and g are formulas then  $f \land g, f \lor g$  and  $\neg f$  are formulas.

- 3. If f and g are formulas then Xf, Gf, Ff and fUg are formulas.

Where X is "Next time", G is "Always", F is "Eventually" and U denotes "Until".

An LTL formula is interpreted over *computations*, where a computation is a function  $\pi : N \to 2^{\mathcal{AP}}$  that assigns truth values to the elements in  $\mathcal{AP}$  at each time instant. For a computation  $\pi$  and a time instant  $i \in \omega$ , we have:

- $\pi, i \models f \text{ iff } p \in \pi(i), \text{ for } f \in \mathcal{AP}$

- $\pi, i \models f \land g \text{ iff } \pi, i \models f \text{ and } \pi, i \models g$

- $\pi, i \models f \lor g \text{ iff } \pi, i \models f \text{ or } \pi, i \models g$

- $\pi, i \models \neg f \text{ iff not } \pi, i \models f$

- $\pi, i \models \mathsf{X}f$  iff  $\pi, i + 1 \models f$

- $\pi, i \models f \cup g$  iff for some  $j \ge i$ , we have  $\pi, j \models g$  and for all  $k, i \le k < j$ , we have  $\pi, k \models f$

Thus the formula, Ff is an abbreviation for *true*  $\bigcup f$  and Gf is abbreviation for  $\neg F \neg f$ . An LTL formula can be any boolean combination or arbitrary nesting of the above operators, therefore one can express GFp ("infinitely often p") and FGp ("almost everywhere p). A computation  $\pi$  satisfies a formula f, written  $\pi \models f$ , iff  $\pi, 0 \models f$ .

The following theorem relates LTL and Büchi automata.

**Theorem 1** ([VW94]) Given an LTL formula f, one can build a Büchi automaton  $A_f = (\Sigma, Q, \delta, q_0, \Phi)$ , where  $\Sigma = 2^{\mathcal{AP}}$  and |Q| is in  $2^{O(|f|)}$ , such that  $L(A_f)$  is exactly the set of computations satisfying the formula f.

#### 2.4 Model Checking

Model checking [CE81, QS82, CES86] is an automated verification technique to analyze and verify hardware and concurrent reactive systems. In model checking, one checks that a system M satisfies a specification T (written as  $M \models T$ ). Typically the system is a circuit or program and the specification is a formula in a temporal logic, like CTL [EH82] or LTL [Pnu77]. The model checking algorithm performs searches in the transition graph of the system in a systematic manner to determine the truth of sub-formulae. For the temporal logic CTL, the algorithm uses the Tarski-Knaster theorem [Tar55], to compute the set of states that define the least fix-point. The time complexity of this method is linear in both the size of the structure and the formula.

The language containment paradigm [VW86, Kur94, LP85] is an approach to model checking, where both the system and the property are specified as automata on infinite strings. For the system M and specification T, the verification check  $M \models T$  can be cast as  $\mathcal{L}(M) \subseteq \mathcal{L}(T)$ . This is equivalent to  $L(M) \cap \neg \mathcal{L}(T) = \emptyset$ . The algorithm for checking non-emptiness proceeds by computing the strongly connected components of the product automaton and then checking if there is a path from an initial state to a strongly connected component containing an accepting state. Language inclusion may be decided in PSPACE [LP85, VW86], and the non-emptiness problem for Büchi automata is decidable in linear time [EL85a, EL85b]. The model checking algorithm for LTL [VW86] uses Theorem 1, to build a Büchi automaton  $\mathcal{A}_{\neg T}$  for the negation of formula T and then checks  $\mathcal{L}(M) \cap \mathcal{L}(\mathcal{A}_{\neg T})$  for emptiness. The time complexity of model checking that a finite state program M satisfies an LTL formula T is linear in size of M but is exponential in the size of formula T. The Lichtenstein-Pnueli thesis [LP85] argues that an upper time bound that is exponential in the size of the specification is considered reasonable since the specification is usually short.

By the results in [SVW87], we know that complementing a Büchi automaton results in an exponential blowup. As a result, an approach that first constructs the Büchi automaton  $\mathcal{A}_T$  (for LTL formula T) and then complements it, would result in a double exponential blow-up. In the automatatheoretic approach, therefore, it is key that the automaton for the specification be easy to complement. We observe, as a consequence of Theorem 0, that  $\forall FA$ 's are trivial to complement and we will exploit this fact in our work.

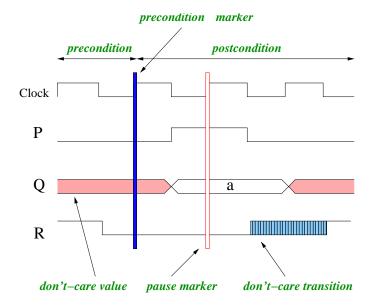

#### 2.5 Timing Diagrams

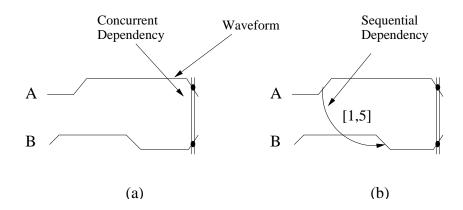

A timing diagram, in its most basic form, consists of a number of waveforms. Each waveform depicts the behavior of a signal or variable over a finite period of time. The value of a waveform at any point in the diagram is chosen from a pre-defined domain; generally this domain is the boolean set  $\{0, 1\}$ . A change in the value of a waveform is known as an *event*. There are several ways that a waveform may interact with other waveforms; these interactions are called dependencies. A concurrent dependency specifies that an event depends on other events occurring at the same time. Concurrent dependencies express properties like "b is low when a rises". A sequential dependency relates two events in the diagram, by specifying that one event occurs within a specified time interval of the other. A sequential dependency can state properties like "event a occurred within 5 time units of event b" or "event a precedes event b. These intervals determine the type of the resulting timing diagram language. Allowing integer constants, variables and arithmetic expressions in the intervals results in a non-regular timing diagram language and restricting the interval to just integer constants and  $\infty$  yields a regular language.

A timing diagram, like the circuit it describes, may be either *asyn*chronous or synchronous. A synchronous diagram includes one or more "clocks" with fixed periods and ensures that the time interval between any pair of events

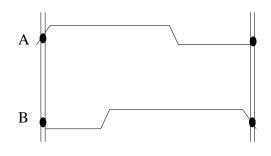

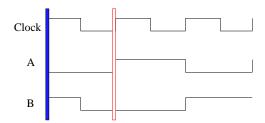

Figure 2.1: (a) Ambiguous Diagram (b) Unambiguous Diagram

is determined up to the clock period. Synchronous diagrams are used to specify timing requirements of clocked systems. On the other hand, *asynchronous* diagrams do not have a clock. Asynchronous timing diagrams are used to specify handshaking protocols like bus arbitration and memory access.

Another feature of timing diagrams, identified by Fisler [Fis96], is that the ordering between events is partial in general; such diagrams are called *ambiguous*. In Figure 2.1 (a), for example, the exact ordering between the rising event on waveform A and the falling event on waveform B is unknown. On the other hand, an *unambiguous* timing diagram has a total ordering on events. In Figure 2.1 (b), the sequential dependency between waveforms Aand B enforces an ordering on those events. In general, synchronous timing diagrams have less ambiguity and more structure than asynchronous diagrams.

A timing diagram is defined for a finite time period and a key issue is an appropriate extension to infinite computations. Fisler [Fis96] addressed this question by considering two kinds of semantics: in the *invariant* semantics, the timing diagram must be satisfied at *every* state of a computation, while in the  $\mathit{basic\ iterative}$  semantics, the diagram must be satisfied iteratively.

### Chapter 3

## **Regular Timing Diagrams**

#### **3.1** Introduction

Asynchronous timing diagrams are characterized by the absence of a global systems clock. These diagrams are generally used to specify handshaking protocols, like bus arbitration, memory access, etc. In this Chapter, we introduce a class of timing diagrams, for asynchronous systems, called *Regular Timing Diagrams* (RTDs). RTDs have a simple and precise semantics and efficient, decompositional model checking algorithms. These diagrams describe changes of signal values over a finite time period, and precedence and timing dependencies between such events; an *event* is defined as a change in signal value. RTDs can express properties like "signal a rises within 5 time units of signal b falling" and "signal b is low when signal a rises". The time intervals are specified by integer constants, ensuring that the diagram defines a *regular* language.

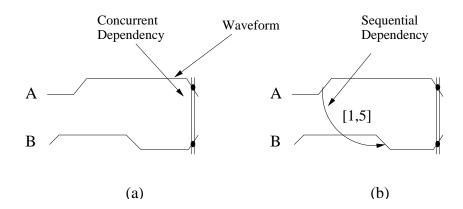

RTDs, like other timing diagrams, may be *unambiguous*, there is a total ordering on events, or *ambiguous*, the ordering between events can be partial

(see Figure 3.1). Since an RTD is defined for a finite time period, an important question that arises in defining the semantics is the manner in which an infinite computation satisfies a timing diagram? Recall that there are two kinds of semantics [Fis96]: in the *invariant* semantics, the timing diagram must be satisfied at *every* state of a computation, while in the *basic iterative* semantics, the diagram must be satisfied iteratively, at points satisfying a precondition of the diagram. In our model, the precondition is a state property. Our semantics is a reformulation of the basic iterative semantics, where we permit a system to satisfy diagrams that express the correctness of different aspects of its operation. For ambiguous diagrams, we further classify this semantics into a *weak* aspect, where a fresh linear ordering of the events is chosen for each satisfaction of the diagram, and a *strong* aspect, where a single linear order is chosen that applies to each satisfaction of the diagram.

The key observation that leads to efficient model checking [CE81, QS82, CES86] is that timing diagrams are compositional (conjunctive) in nature. This can be visualized informally as the waveforms acting independently and only interacting with other waveforms through a dependency. Rather than build the single, monolithic  $\omega$ -NFA or the temporal logic formula that corresponds to the entire diagram, we demonstrate that it is possible to decompose the diagram into properties of isolated waveforms and their interactions. This results in a conjunction of simpler properties that can be conveniently represented by a succinct  $\forall$ -automaton ( $\forall FA$ ) [MP87, Var87]. A  $\forall FA$  (also known as "dual-run" or "universal" automaton) is a finite state automaton that accepts an input iff every run of the automaton along the input meets the acceptance criterion.  $\forall FA$ 's can be exponentially more succinct than NFA's and naturally express properties that are conjunctive in nature.

Moreover, this conjunctivity can be exploited to verify smaller components of the timing diagram in isolation, thus avoiding the construction of the entire  $\forall$ -automaton. We present efficient algorithms that convert RTDs under the various semantics into  $\forall FA$ 's that are in the worst case of size polynomial in the size of the diagram and the largest time constant represented in unary (note that the unary size is exponential in the binary size). These constants are generally performance bounds and tend to be small; thus, we feel justified in claiming polynomial complexity. The use of  $\forall FA$ 's permits the efficient use of the automata-theoretic approach [VW86, Kur94, LP85] to model checking. For a system M and RTD T, the verification check can be cast as  $\mathcal{L}(M) \subseteq \mathcal{L}(\mathcal{A}_T)$ , where  $\mathcal{A}_T$  is the (small, polynomial size)  $\forall FA$  for the diagram T and  $\mathcal{L}(X)$ denotes the language of X. This is equivalent to  $\mathcal{L}(M) \cap \neg \mathcal{L}(\mathcal{A}_T) = \emptyset$ . The complement language of a  $\forall FA$  is accepted by a NFA with identical structure but complemented acceptance condition. Hence, complementation (the  $\neg \mathcal{L}(\mathcal{A}_T)$  term) is trivial, and the complexity of the model checking procedure is linear in the size of the structure and polynomial in the size of the  $\forall FA \ A_T$ . In addition, it is often possible to decompose  $\mathcal{A}_T$  itself into a conjunction of smaller  $\forall FA$ 's, which may be checked independently with M. It is also simple to produce a description of  $\neg \mathcal{L}(\mathcal{A}_T)$  that can be input to a symbolic model checker.

The algorithm is linear in the structure size, polynomial in the number of diagram points and dependencies and in the unary size of the constants. The polynomial complexity of our decompositional algorithm is a significant improvement over the earlier monolithic approaches (cf. [Fis96, DJS94]), where the size may be exponential in the worst case. Not withstanding the Lichtenstein-Pnueli thesis [LP85], in practice, as one reaches the limits of applicability of symbolic model checking tools, the size of the specification is of importance. A detailed discussion of these points is in Section 3.6.

The rest of the Chapter proceeds as follows. In Section 3.2, we give a precise syntax and semantics for Regular Timing Diagrams. Section 3.3 presents the algorithms that convert RTDs into  $\forall FA$ 's. The model checking procedure is presented in Section 3.4. Section 3.5 describes how the algorithms are used with with the model checking tool VIS [BHSV<sup>+</sup>96] for the verification of a master-slave system. We conclude with a discussion of related work in Section 3.6.

## 3.2 Regular Timing Diagrams - Syntax and Semantics

A Regular Timing Diagram (henceforth referred to as an RTD or diagram) is specified by a number of finite waveforms, each defined over a set of "symbolic" values SV, and timed dependencies between points on the waveforms. The set of symbolic values SV is an user-defined domain of values plus the value X, that is used to specify that the value is unspecified or unknown. For boolean signals, the set SV is  $\{0, 1, X\}$ . However, SV could be either an enumerated type, or all the values of an address bus. The set SV is partially ordered by  $\dot{\sqsubseteq}$ , where  $a \stackrel{.}{\sqsubseteq} b$  iff a = X or a = b.

#### 3.2.1 Syntax

**Definition 3 (RTD)** A RTD is a tuple (S, WF, SD, CD), where

• S is a non-empty set of signal names.

Figure 3.1: (a) Ambiguous RTD (b) Unambiguous RTD

- WF is a collection of waveforms; for each signal A ∈ S, its associated waveform is a function A : [0, n) → SV where n > 1 is an integer referred to as the size of the waveform. If A ∈ WF and i ∈ [0, size(A)) then the pair (A, i) is called a point of A.<sup>1</sup> (A, 0) is the initial point and (A, size(A)-1) is the final point of A.

- SD is the set of sequential dependencies on the points of WF. Each dependency is specified as (A, i) <sup>[a,b)</sup>→ (B, j), where a ∈ N, b ∈ N ∪ {∞}, 1 ≤ a and a < b. For convenience, [k,∞) is often written as ≥ k, [1,k] as ≤ k and [k,k] as = k.</li>

- CD is a collection of mutually disjoint, non-empty concurrent dependencies. Each concurrent dependency is a set of points with at most one point from each waveform in WF. The sets of initial and final points of the diagram form predefined concurrent dependencies.

<sup>&</sup>lt;sup>1</sup>A point (A, i) is also a point of WF and the RTD.

**Definition 4 (Event)** The smallest set of points closed under the following rules are the events of an RTDT = (S, WF, SD, CD).

- 1. For every waveform A in WF, (A, 0) is an event.

- 2. Let (A, i) be an event with  $(A, i) \neq X$  and let (A, j) be the first successor of (A, i) such that  $A(i) \neq A(j)$ . If  $A(j) \neq X$  then (A, j) is an event.

- If (A, i) is a member of a concurrent dependency that contains an event, then (A, i) is an event.

- 4. If (A, i) is an event and  $(A, i) \xrightarrow{=k} (B, j)$  is a sequential dependency, then (B, j) is an event.

Notice that for any input string of vectors of signal values, every event has at most one position on the string. This "precise location" property of events is the key to our efficient model checking algorithm. For every event e, it is possible to construct a *DFA* we call *locator*(e) that accepts at the position on an input string where the event holds. This *DFA* essentially encodes the sequence of applications of the rules above that define the point e as an event.

A symbolic point of an RTD is either a concurrent dependency or a singleton set containing a point that is not in any concurrent dependency.

**Definition 5 (Symbolic Point)** p is a symbolic point of an RTD iff either  $p \in CD$  or p contains only one point e, such that for each  $C \in CD$ ,  $e \notin C$ .

The set of symbolic points is denoted by SP. Informally, events in a symbolic point should occur simultaneously. The sequential dependencies of an RTD induce the following ordering relation  $\prec$  on symbolic points.

**Definition 6 (Ordering on Symbolic Points**  $(\prec)$ ) Given symbolic points p and q,  $p \prec q$  iff

- for some waveform  $A \in WF$ , the point  $(A, i) \in p$  and point  $(A, i+1) \in q$ , or

- there exist  $e \in p$  and  $f \in q$  such that  $e \xrightarrow{\alpha} f$  is a sequential dependency.

The RTD syntax allows several definitions that run counter to intuition. For instance, dependencies may be cyclically related, or it may be possible that the location of a dependency is imprecise due to the presence of X (undetermined) parts of a waveform. These cases are ruled out by giving a notion of "well-formed" RTDs, which is defined below.

**Definition 7 (Well-formed RTD)** An RTD is well-formed iff (i) every point of the RTD is an event and (ii) the transitive closure of  $\prec (\prec^+)$  is irreflexive.

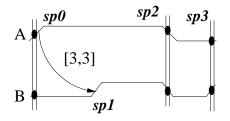

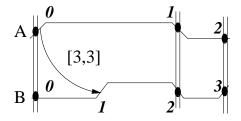

The annotated RTD in Figure 3.2 can be expressed notationally as follows.

Figure 3.2: RTD T Annotated with Symbolic Points

$$\begin{array}{lll} WF &: & \{A, B\} \\ A &: & 0 \mapsto 1, 1 \mapsto 0, 2 \mapsto 0 \\ B &: & 0 \mapsto 0, 1 \mapsto 1, 2 \mapsto 0, 3 \mapsto 1 \\ SD &: & \{(A, 0) \xrightarrow{[3,3]} (B, 1)\} \\ CD &: & \{\{(A, 0), (B, 0)\}, \{(A, 1), (B, 2)\}, \{(A, 2), (B, 3)\}\} \end{array}$$

There are four symbolic points in this RTD: the singleton  $\{(B,1)\}$ and the three concurrent dependencies,  $\{(A,0), (B,0)\}$ ,  $\{(A,1), (B,2)\}$  and  $\{(A,2), (B,3)\}$ . The pre-defined concurrent dependencies at the initial and final points of the RTD are shown in Figure 3.2, however, for visual clarity, we will not always show these concurrent dependencies in the diagrams for the remainder of this Chapter.

### 3.2.2 Semantics

The semantics of an RTD is a set of infinite computations over *states*; each state is a vector indexed by the waveforms of the timing diagram. The set of states is denoted by  $\Sigma$ . The partial order  $\doteq$  defined earlier is extended to states as follows:  $u \doteq w$  iff for each  $i, u(i) \doteq w(i)$ . A computation of the system to be verified consists of an infinite sequence of states from  $\Sigma$ . Since the syntax of an RTD describes only finite sequences of events, a key question is the appropriate extension to infinite computations.

The predefined initial and final concurrent dependencies can be viewed as the begin- and end- conditions of the finite sequence of events described by the RTD syntax; the initial concurrent dependency is a state predicate and the final concurrent dependency is a path predicate. For example, the begincondition for the RTD in Figure 3.2 is  $\langle A = 1, B = 0 \rangle$  and the end-condition is the concurrent dependency at the state  $\langle A = 0, B = 1 \rangle$ . As another example, if the diagram represents the behavior for a "memory-read" transaction, the begin- and end- conditions indicate the states that define the extent of this transaction. Clearly, this diagram should be checked only on the finite subcomputation that starts at a state satisfying the begin-condition and ends with a state satisfying the end-condition. One may thus consider an infinite sequence to satisfy a timing diagram iff the dependencies of the diagram are satisfied in each finite sub-sequence defined by the begin- and end- conditions. This statement, though, is still open to many interpretations, some of which are considered below. We first define what it means for a finite sequence of states to satisfy a timing diagram. Recall that the relation  $\prec^+$  partially orders the set of symbolic points, SP. In the following definitions  $\mathcal{P}$  denotes the set of points in the diagram.

**Definition 8 (Assignment)** Given a string of length n, an assignment  $\pi$  is a function  $\pi : SP \to [0, n)$ , that is strictly monotonic w.r.t.  $\prec (p \prec q \text{ implies} \pi(p) < \pi(q))$  and maps the initial symbolic point to 0.

**Definition 9 (Equivalent Assignments)** Two assignments  $\pi : SP \to [0, n)$ and  $\xi : SP \to [0, m)$  are equivalent iff for all  $p, q \in SP$ ,  $\pi(p) < \pi(q)$  iff  $\xi(p) < \xi(q)$ .

Any assignment  $\pi$  induces the function  $\hat{\pi} : \mathcal{P} \to [0, n)$  which maps a point (A, i) to k iff the (unique, by definition) symbolic point that includes (A, i) is mapped to k by  $\pi$ . From the definition of  $\pi$ , it follows that all points in a concurrent dependency are assigned a common position. **Definition 10 (RTD satisfaction)** An RTD T = (S, WF, SD, CD) is satisfied by a finite sequence  $z \in \Sigma^+$  w.r.t. an assignment  $\pi : SP \to [0, |z|)$ (written as  $z \models_{\pi} T$ ) iff the following conditions hold.

- 1. Point consistency: For every point (A, i), if  $\hat{\pi}((A, i)) = k$ , then  $A(i) \stackrel{.}{\sqsubseteq} z_k(A)$ , where  $z_j(A)$  is  $z_j$  projected onto the coordinates for A.

- 2. Waveform consistency: Let  $\hat{\pi}((A, i)) = k$  and  $\hat{\pi}((A, i+1)) = l$ . For every  $j \in [k, l)$ ,  $A(i) \stackrel{.}{\sqsubseteq} z_j(A)$ .

- 3. Dependency consistency: For every sequential dependency  $e \xrightarrow{[a,b]} f$ ,  $(\hat{\pi}(f) - \hat{\pi}(e)) \in [a,b).$

Figure 3.3: RTD Annotated with Points

We will use the following notation to denote sequences: the angle brackets denote the vector of values at a given state, ";" denotes succession in time and the superscript n on a state s is a shorthand for n successive copies of s. We will also use  $\langle 1, 1 \rangle$  to represent the state  $\langle A = 1, B = 1 \rangle$ . Consider the finite sequence  $y[0..6] = \langle 1, 0 \rangle^3$ ;  $\langle 1, 1 \rangle$ ;  $\langle 0, 0 \rangle$ ;  $\langle 0, 0 \rangle$ ;  $\langle 0, 1 \rangle$ . For RTD T in Figure 3.2, the assignment  $\pi$  maps:  $sp_0$  to 0,  $sp_1$  to 3,  $sp_2$  to 4 and  $sp_3$  to 6. The function  $\hat{\pi}$  is as follows:  $(A, 0) \rightarrow 0$ ,  $(A, 1) \rightarrow 4$ ,  $(A, 2) \rightarrow 6$ ,  $(B, 0) \rightarrow 0$ ,  $(B, 1) \to 3, (B, 2) \to 4$  and  $(B, 3) \to 6$ . The RTD in Figure 3.3 is annotated with the points. Note that y satisfies the conditions in Definition 10, with respect to assignment  $\pi$ , hence  $y \models_{\pi} T$ .

For many systems, it is the case that the begin- condition for the timing diagram does not recur before the end- condition holds. For such nonoverlapping systems, we may consider the following semantics. System computations may be described by the expression  $(\Delta^+ \lor (\#\Delta^+\$))^{\omega}$ , where # and \$ are special vectors of  $\Sigma$  representing the satisfaction of the begin- and endconditions respectively and  $\Delta = \Sigma \setminus \{\#, \$\}$ . The sequence of the form  $\#\Delta^+\$$ is called a *transaction*.

**Definition 11 (Weak Iterative Semantics)** An infinite sequence z satisfies an RTD T under the weak iterative semantics (written as  $z \models_w T$ ) iff for every transaction #y\$ on z, there exists an assignment  $\pi$  for which #y\$  $\models_{\pi} T$ .

**Definition 12 (Strong Iterative Semantics)** An infinite sequence z satisfies an RTD T under the strong iterative semantics (written as  $z \models_s T$ ) iff there exists an assignment  $\xi$  such that for every transaction #y\$ of z, there is an equivalent assignment  $\pi$  such that #y\$  $\models_{\pi} T$ .

Consider the ambiguous RTD T in Figure 3.4 and a finite sequence  $y = \langle 1, 0 \rangle$ ;  $\langle 1, 1 \rangle$ ;  $\langle 0, 1 \rangle$ ;  $\langle 0, 0 \rangle$ ;  $\langle 1, 0 \rangle$ ;  $\langle 0, 0 \rangle$ ;  $\langle 0, 0 \rangle$ ;  $\langle 0, 0 \rangle$ . Let z be an infinite sequence where the y repeats forever. In sequence y, there are two transactions, one where A falls before B rises and another where B rises before A falls. The definition of the weak iterative semantics allows a fresh ordering of events to be chosen on each transaction, therefore,  $z \models_w T$ . On the other hand,  $z \not\models_s T$ , since the ordering used in the two transactions is different.

Figure 3.4: Ambiguous RTD T

We consider now an alternative formulation of Definition 10, which forms the basis for the decompositional algorithms for model checking. If #y\$ satisfies the timing diagram, each event, by Definition 4, may be located precisely on the sequence. The key observation is that, since each dependency consists of precisely located events, it can be checked independently of the others.

**Theorem 2** Let pt be the partial function that defines the location of events on a finite sequence. For an RTD T = (S, WF, SD, CD), and any finite transaction z = #y, there exists an assignment  $\pi$  such that  $z \models_{\pi} T$  iff each of the following conditions holds:

- (a) Every event of T can be located on z and has a value consistent with that in T; i.e., pt is total, and if pt(z, (A, i)) = k then  $A(i) \stackrel{.}{\sqsubseteq} z_k(A)$ .

- (b) Let pt(z, (A, i)) = k and pt(z, (A, i + 1)) = l. For every j in [k, l),  $A(i) \stackrel{.}{\sqsubseteq} z_j(A)$ .

- (c) For each sequential dependency  $e \xrightarrow{[a,b]} f$ ,  $(pt(z,f) pt(z,e)) \in [a,b]$ .

(d) For each pair of events e, f in a concurrent dependency, pt(z, e) = pt(z, f).

**Proof.** ( $\Rightarrow$ )  $z \models_{\pi} T$  implies, by Definitions 8 and 10 and the precise location property, that pt is total. Point consistency, in Definition 10, implies that pt(z, (A, i)) = k then  $A(i) \doteq z_k(A)$ . Condition (c) follows directly from waveform consistency in Definition 10. Dependency consistency in Definition 10 implies  $(pt(z, f) - pt(z, e)) \in [a, b)$ . Definition 8 implies that each pair of events e, f in a concurrent dependency, are assigned by  $\pi$  to the same location, hence pt(z, e) = pt(z, f).

( $\Leftarrow$ ) If  $\hat{\pi}((A, i)) = k$  then, by conditions (a) and (d),  $A(i) \stackrel{.}{\sqsubseteq} y_k(A)$  (point consistency). Conditions a and b ensure waveform consistency (Definition 10). Dependency consistency follows directly from c.  $\Box$

Notice that the theorem essentially transforms the existential  $(\exists)$  condition of Definitions 11 through 12 into a universal  $(\forall)$  condition; this forms the basis for the decompositional check.

## **3.3** Translation Algorithms

Theorem 2 is fundamental to decomposing RTDs into a conjunction of properties of individual waveforms, and ordering or timing restrictions on their interactions, which is the key to efficient model checking. In this section, we provide algorithms that translate an RTD under, both strong and weak iterative semantics, into a  $\forall FA$ . For clarity, we often describe the  $\omega$ -NFA for the complement language instead of the  $\forall FA$ .

## 3.3.1 Translating RTDs with Weak Iterative Semantics

Figure 3.5: RTD T Annotated with Unordered Events

Recall, that we can construct a DFA called locator(e) that accepts at the position on an input string where the event e holds. We now describe the  $\omega$ -NFA  $A_{\overline{T}}$  that accepts the complement of the weak-iterative language of an RTD T = (S, WF, SD, CD).

### Algorithm 1

- 1. Construct a finite string automata for each waveform and dependency as follows:

- Waveform: The automaton  $\mathcal{A}_B$  for a waveform B is constructed as follows: if (B, i+1) is defined in terms of (B, i), then locator((B, i))is extended to ensure that the signal values up to the change of value that defines (B, i+1) are above B(i) in  $\sqsubseteq$  order. Otherwise, locator((B, i)) is used to determine that the value at the position where (B, i) holds is above B(i) in  $\doteq$  order.

- Sequential dependency: The automaton  $\mathcal{A}_{sd}$ , for a sequential dependency  $e \xrightarrow{[a,b]} f$ , is a parallel composition of locator(e) and locator(f)

that accepts iff the time between the acceptance of the locator DFA's is within  $[a, b\rangle$ .

- Concurrent dependency: The ∀FA, A<sub>cd</sub>, for a concurrent dependency C checks that for a fixed event e in C and every other event f in C, locator(e) and locator(f) accept at the same position on the input sequence.

- 2. The  $\omega$ -NFA  $\mathcal{A}_{\overline{T}}$  operates as follows on an infinite input sequence: it nondeterministically "chooses" a transaction #y\$ on the input, "chooses" which waveform or dependency fails to hold of the transaction, and accepts if the automaton for that entity (defined as given above) rejects.

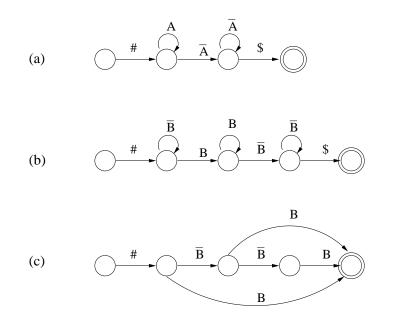

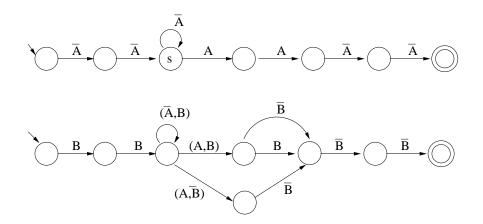

Figure 3.6: Automata for (a) Waveform A (b) Waveform B (c) Sequential Dependency

Notice that each automaton defined above is either a DFA or a  $\forall FA$ ,

both of which can be trivially complemented. The  $\forall FA \ \mathcal{A}_T$  obtained from this  $\omega$ -NFA  $\mathcal{A}_{\overline{T}}$  by complementing the acceptance condition defines the language of the RTD under the weak iterative semantics.

Figure 3.7:  $\omega$ -NFA  $\mathcal{A}_{\overline{T}}$  for Weak Iterative Semantics

**Theorem 3 (Correctness)** For any RTD T and  $x \in \Sigma^{\omega}$ ,  $x \models_w T$  iff  $x \in \mathcal{L}(\mathcal{A}_T)$ .

**Proof.**  $(\Rightarrow) x \models_w T$  implies (by definition 11) that for every transaction #y\$ on x, there exists an assignment  $\pi$  such that #y\$  $\models_{\pi} T$ . Let us assume that  $x \in \mathcal{A}_{\overline{T}}$ . We know, by the construction of  $\mathcal{A}_{\overline{T}}$ , that there must be a transaction z along x such that some DFA (for a waveform or dependency)  $\mathcal{A}_d$  rejects on z. Therefore, by the construction of DFA's  $\mathcal{A}_d$ , there is no assignment  $\pi$  such that  $z \models_{\pi} T$  (i.e. z must violate the constraints on some waveform or dependency). Since  $x \models_w T$ , such a z transaction does not exists; thus  $x \in \mathcal{L}(\mathcal{A}_T)$ .

( $\Leftarrow$ )  $x \in \mathcal{L}(\mathcal{A}_T)$ , by definition 2, iff every run of  $\mathcal{A}_T$  on x is accepting. In the construction of  $\mathcal{A}_T$ , this implies that every transaction along x is accepted by all the *DFA*'s (for the waveforms or dependencies). Let us assume that  $x \not\models_w T$ , this means that x has a transaction z, such that  $\neg(\exists \pi : (z \models_{\pi} T))$ . Therefore, by Definition 10, z violates either (1) point consistency (2) waveform consistency, or (3) dependency consistency. However, the *DFA*'s constructed for waveforms or dependencies satisfy these conditions by construction. Thus, we have a contradiction, and  $x \models_w T$ .  $\Box$

For the diagram T = (S, WF, SD, CD), let l be the size in unary of the largest constant in SD. Define |T| = #points + |SD| + |CD|. The size of  $\mathcal{A}_T$  is cubic in |T| and l.

**Theorem 4 (Complexity)** For any RTD T, the size of the corresponding  $\forall FA \ A_T$  is polynomial in |T| and the unary length of the largest constant in T.

**Proof.** The size of an RTD is T = e+s+c, where e is the number of events in T, s = |SD| and c = |CD|. Let l be the largest constant in unary and w be the number of waveforms. We assume that the transitions in  $\mathcal{A}_T$  are labeled with boolean formulas over the w signals. The size of the transitions in  $\mathcal{A}_T$  is the sum of the length of the formulas labeling the transitions. The size of  $\mathcal{A}_T$  is v + t, where v is the number of states and t is the transition size.

The number of states in each locator automaton is bounded by k = (e + l). In the construction above, the number of states in the *DFA* for a waveform is O(k). Since each transition encodes the values of the signals at each point, the size of each transition is O(w), while the number of transitions is bounded by e. Thus, the transition size of each locator automaton is O(k). The size of the *DFA* for each sequential dependency is  $O(k^2)$ , as it consists of two locators in parallel. The size of the  $\forall FA$  for each concurrent dependency

is  $O(w.k^2)$ , as each concurrent dependency can have at most w events. The size of  $\mathcal{A}_T$  is  $w.O(k) + s.O(k^2) + c.O(k^2)$ , which is cubic in |T|.  $\Box$

## 3.3.2 Translating RTDs with Strong Iterative Semantics

Under the strong iterative semantics, every transaction on an input computation has to satisfy the RTD T with respect to a single event ordering. The  $\omega$ -NFA  $\mathcal{A}_{\overline{T}}$  for the complemented language accepts a computation iff

- Some transaction violates a waveform or dependency constraint, or

- There is a transaction and a pair of events that occur in a different order from that in the first transaction.

The  $\omega$ -NFA  $\mathcal{A}_{\overline{T}}$  for the complement of the RTD T under the strong-iterative semantics is constructed as follows:

#### Algorithm 2

- 1. Construct the  $\omega$ -NFA  $\mathcal{A}_{weak}$  as defined for the weak-iterative semantics.

- 2. For each pair of unordered events e and f, construct an automaton  $A_{ef}$  as follows:  $A_{ef}$  first executes the locator DFA's for events e and f in parallel on the first transaction to determine their relative order.  $A_{ef}$  then chooses a subsequent transaction and executes the locator DFA's of the same events on that transaction to determine the new order, and accepts if the orders differ.

- 3. The  $\omega$ -NFA  $\mathcal{A}_{ord}$ , at the initial state, nondeterministically "chooses" events e and f that are unordered by  $\prec^+$ , runs automaton  $A_{ef}$  and accepts if  $A_{ef}$  accepts.

- 4. The  $\omega$ -NFA  $\mathcal{A}_{\overline{T}}$  accepts if either  $\mathcal{A}_{weak}$  or  $\mathcal{A}_{ord}$  accepts.

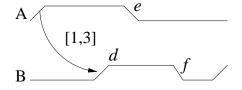

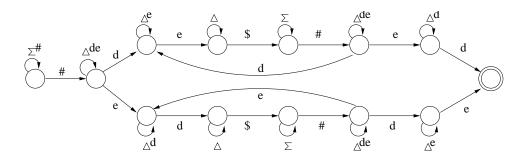

Figure 3.8 depicts the automaton  $\mathcal{A}_{de}$  for events d and e in the RTD shown in Figure 3.5. In Figure 3.8,  $\Sigma$  is the alphabet,  $\Delta = \Sigma \setminus \{\#, \$\}, \Sigma^{\#}$ denotes  $\Sigma \setminus \{\#\}, \Delta^{de}$  denotes  $\Delta \setminus \{d, e\}, \Delta^{d}$  denotes  $\Delta \setminus \{d\}$  and  $\Delta^{e}$  denotes  $\Delta \setminus \{e\}$ .

Figure 3.8: NFA  $\mathcal{A}_{de}$  for Events d and e in Figure 3.5

Let  $\mathcal{A}_T$  denote the  $\forall FA$  obtained from the  $\omega$ -NFA  $\mathcal{A}_{\overline{T}}$  by complementing the acceptance condition. The size of  $\mathcal{A}_T$  is polynomial in |T| and l for the first case  $(\mathcal{A}_{weak})$ ; for the second  $(\mathcal{A}_{ord})$ , it is quadratic in |T| and l with a multiplicative factor of the number of event pairs (which is bounded by  $(\#points)^2$ ).

**Theorem 5 (Correctness)** For any RTD T and  $x \in \Sigma^{\omega}$ ,  $x \models_s T$  iff  $x \in L(\mathcal{A}_T)$ .