Copyright

by

Daniel Angel Jiménez

2002

The Dissertation Committee for Daniel Angel Jiménez Certifies that this is the approved version of the following dissertation:

## **Delay-Sensitive Branch Predictors for Future Technologies**

| Committee:             |

|------------------------|

| Calvin Lin, Supervisor |

| Douglas C. Burger      |

| Stephen W. Keckler     |

| Hugh B. Maynard        |

| Kathryn S. McKinley    |

| Yale N. Patt           |

# Delay-Sensitive Branch Predictors for Future Technologies

by

Daniel Angel Jiménez, B.S, M.S.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2002

## Acknowledgments

In my research, I have received assistance from many people.

Calvin Lin, an assistant professor in Computer Sciences, is my supervising professor. He has been deeply involved in guiding my research and is a co-author on all of my recent publications. Many of the ideas presented in this dissertation were formed in discussions with Calvin, and many of the successful ideas I came up with on my own were ideas I almost gave up on when Calvin said "let's take another look at this." Calvin has made it his responsibility to make sure that I, as well as all of his other students, have had the financial support we need to accomplish our goals; he is a staunch advocate for each of us, and although he leads a busy life, it seems he always has time to meet with us and discuss whatever is on our minds; we are all thankful for him.

The members of my dissertation committee are: Doug Burger, Steve Keckler, Calvin Lin, Hugh Maynard, Kathryn McKinley and Yale Patt. Each of them has made invaluable contributions to this dissertation through discussions, feedback on my writings, and the proposal process.

Steve Keckler, an assistant professor in Computer Sciences, has contributed several distinctive insights to my research through many fruitful discussions as well as actual work on my ideas. It was his idea to study how technology scaling will

affect branch predictors, providing the foundation upon which this dissertation is built. Steve is a co-author on our paper on hierarchical branch predictors [32]. It was his suggestion to use a Wallace-tree to implement the perceptron predictor.

Heather Hanson, a graduate student in Electrical & Computer Engineering, has helped me understand the tools used for studying CMOS circuits. She is a co-author on our paper on the Boolean formula predictor. She helped design the circuit for that predictor and she set up the scripts used to measure its power and delay. She helped me understand the HSPICE tool so that I could use it for studying the perceptron predictor.

Vikas Agarwal, a graduate student in Electrical & Computer Engineering, modified the CACTI 2.0 cache simulator for technology scaling for his research. He provided me with his enhanced versions of CACTI and, through a detailed discussion, helped Calvin and me understand the results his predictor yields.

Rajagopalan Desikan, a graduate student in Electrical & Computer Engineering, has helped me understand various aspects of the Alpha 21264 microarchitecture, including the operation of the branch predictor.

Samuel Z. Guyer, a doctoral candidate in Computer Sciences, and Ibrahim Hur, a doctoral candidate in Electrical & Computer Engineering, provided useful suggestions and feedback on drafts of papers.

Many other fellow students have contributed to my research by providing useful feedback at practice talks. They are: Kartik K. Agaram, Vikas Agarwal, Emery D. Berger, Mary D. Brown, Brendon D. Cahoon, Rich J. Cardone, Rajagopalan Desikan, Samuel Z. Guyer, Heather L. Hanson, Ibrahim Hur, Maria E. Jump, Ramgopal R. Mettu, Hrishikesh S Murukkathampoondi, Ramadass Nagarajan, Erik H. Reeber, Juan C. Rubio, Karthikeyan Sankaralingam, Alison N. Smith, Teck Bok Tok, Francis Tseng and Phoebe K. Weidmann.

During the course of my research, I have submitted several papers to peerreviewed conferences. The anonymous reviewers have provided valuable insights, pointers to literature, and criticisms that I have used to make my research stronger.

Last, but not least, my wife, Stella L. Jiménez, has endured the several years of my graduate career with more cheer than I could have expected. She is my best friend and the source of my strength. She has supported our household financially through my years of voluntarily reduced earnings.

Daniel Angel Jiménez

The University of Texas at Austin May 2002

# Delay-Sensitive Branch Predictors for Future Technologies

| Publication No. |

|-----------------|

|-----------------|

Daniel Angel Jiménez, Ph.D.

The University of Texas at Austin, 2002

Supervisor: Calvin Lin

Accurate branch prediction is an essential component of a modern, deeply pipelined microprocessors. Because the branch predictor is on the critical path for fetching instructions, it must deliver a prediction in a single cycle. However, as feature sizes shrink and clock rates increase, access delay will significantly decrease the size and accuracy of branch predictors that can be accessed in a single cycle. Thus, there is a tradeoff between branch prediction accuracy and latency. Deeper pipelines improve overall performance by allowing more aggressive clock rates, but some performance is lost due to increased branch misprediction penalties. Ironically, with shorter clock periods, the branch predictor has less time to make a prediction and might have to be scaled back to make it faster, which decreases accuracy and reduces the advantage of higher clock rates.

We propose several methods for breaking the tradeoff between accuracy and latency in branch predictors. Our methods fall into two broad categories: hierarchical predictors using purely hardware implementations, and cooperative predictors that off-load some prediction work to the compiler. We describe hierarchical organizations that extend traditional predictors. We then describe a highly accurate branch predictor based on a neural learning technique. Using a hierarchical organization, this complex multi-cycle predictor can be used as a component of a fast delay-sensitive predictor. We introduce a novel cooperative branch predictor that off-loads most of the prediction work to the compiler with profiling. The compiler communicates profiled information to the microprocessor using extensions to the instruction set. This Boolean formula predictor has a small and fast hardware implementation, and will work in less than one cycle in even the smallest technologies with the most aggressive projected clock rates. Finally, we present another cooperative technique, branch path re-aliasing, that moves complexity off of the critical path for making a prediction and into the compiler; this technique increases accuracy by reducing destructive aliasing during the less critical update stage.

# **Contents**

| Acknow    | ledgme        | ents                                                | V    |

|-----------|---------------|-----------------------------------------------------|------|

| Abstrac   | et            |                                                     | viii |

| List of   | <b>Fables</b> |                                                     | xvi  |

| List of I | Figures       |                                                     | xvii |

| Chapter   | r 1 In        | troduction                                          | 1    |

| 1.1       | The Pa        | roblem: Delay in Branch Predictors                  | . 2  |

| 1.2       | Dimer         | nsions of the Problem                               | . 5  |

|           | 1.2.1         | Extending Traditional Predictors in the Near Future | . 5  |

|           | 1.2.2         | Increasing Accuracy in the Face of Delay            | . 6  |

|           | 1.2.3         | Addressing Technology Scaling                       | . 6  |

| 1.3       | Our So        | olutions                                            | . 7  |

|           | 1.3.1         | Scope and Limitations of the Research               | . 9  |

| 1.4       | Thesis        | Statement                                           | . 10 |

| 1.5       | Contri        | butions                                             | . 10 |

| Chapte    | r 2 Ba        | nckground                                           | 12   |

|    | 2.1             | History | y of Branch Prediction            | 12 |

|----|-----------------|---------|-----------------------------------|----|

|    | 2.2             | Charac  | eteristics of Branch Prediction   | 14 |

|    | 2.3             | Branch  | Prediction Mechanisms             | 15 |

|    |                 | 2.3.1   | GAg and GAs Predictors            | 16 |

|    |                 | 2.3.2   | gshare predictor                  | 16 |

|    |                 | 2.3.3   | Agree predictors                  | 17 |

|    |                 | 2.3.4   | Bi-Mode predictor                 | 17 |

|    |                 | 2.3.5   | Static Branch Prediction          | 17 |

|    |                 | 2.3.6   | Branch Predictors in Current CPUs | 18 |

|    | 2.4             | Techno  | ology Scaling                     | 18 |

| C) | h a <b> 4</b> a | . 2 M.  | sthe delegar                      | 20 |

| CI | •               |         | <i>6i</i>                         | 20 |

|    | 3.1             | Simula  | ated Microprocessor               | 20 |

|    | 3.2             | Benchi  | marks                             | 21 |

|    | 3.3             | Branch  | Misprediction Rates               | 22 |

|    |                 | 3.3.1   | Simulated Branch Predictors       | 22 |

|    |                 | 3.3.2   | Tuning Branch Predictors          | 23 |

|    |                 | 3.3.3   | Testing Branch Predictors         | 24 |

|    | 3.4             | Instruc | etions per Cycle                  | 24 |

|    | 3.5             | Circuit | Timings                           | 25 |

|    |                 | 3.5.1   | HSPICE                            | 25 |

|    |                 | 3.5.2   | CACTI                             | 25 |

|    | 3.6             | Compu   | uting Facilities                  | 26 |

| Ω1 | . 4             | 4 111   |                                   | 25 |

| Cl | -               |         | 8                                 | 27 |

|    | 4.1             | Motiva  | ntion                             | 27 |

|    | 12              | Dronoh  | Fraguanay                         | 20 |

| 4.3     | Hierard | chical Organizations for Latency Sensitive Branch Predictors | 29  |

|---------|---------|--------------------------------------------------------------|-----|

|         | 4.3.1   | Caching Prediction Tables                                    | 30  |

|         | 4.3.2   | Cascading Lookahead Branch Prediction                        | 31  |

|         | 4.3.3   | Overriding Branch Predictor                                  | 33  |

| 4.4     | Techno  | ology Scaling                                                | 34  |

| 4.5     | Results | and Analysis                                                 | 35  |

|         | 4.5.1   | Process Technology Scaling                                   | 36  |

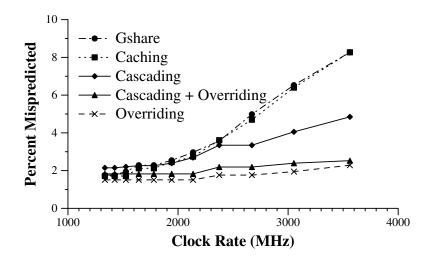

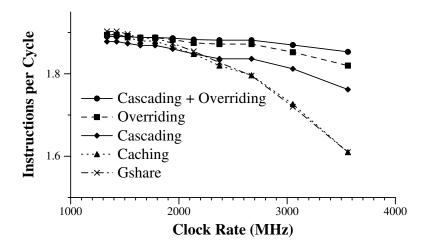

|         | 4.5.2   | Clock Rate Scaling                                           | 41  |

| 4.6     | Summa   | ary                                                          | 43  |

| CI. 4   | 7 D     |                                                              | 4.5 |

| Chapter | · 5 Pei | rceptron Predictor                                           | 45  |

| 5.1     | Neural  | Methods for Dynamic Branch Prediction                        | 46  |

|         | 5.1.1   | Prediction with Neural Methods                               | 47  |

|         | 5.1.2   | Neural Learning for Dynamic Branch Prediction                | 48  |

|         | 5.1.3   | Choosing a Neural Method                                     | 48  |

| 5.2     | Branch  | Prediction with Perceptrons                                  | 49  |

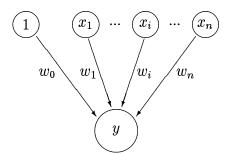

|         | 5.2.1   | How Perceptrons Work                                         | 50  |

|         | 5.2.2   | Training Perceptrons                                         | 50  |

|         | 5.2.3   | Linear Separability                                          | 51  |

|         | 5.2.4   | Branch Prediction with Perceptrons                           | 52  |

| 5.3     | Implen  | nentation                                                    | 53  |

|         | 5.3.1   | Design Space                                                 | 54  |

|         | 5.3.2   | Circuit-Level Implementation                                 | 55  |

| 5.4     | Results | and Analysis                                                 | 57  |

|         | 5.4.1   | Methodology                                                  | 58  |

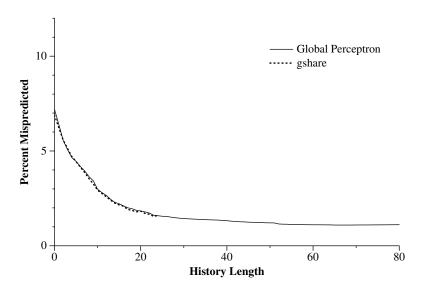

|         | 5.4.2   | Impact of History Length on Accuracy                         | 60  |

|         | 5.4.3  | Misprediction Rates                                | . 60  |

|---------|--------|----------------------------------------------------|-------|

|         | 5.4.4  | Delay Sensitive Perceptron Predictor               | . 63  |

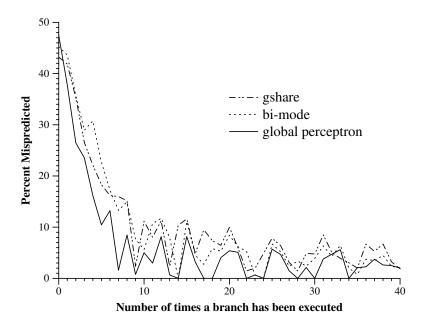

|         | 5.4.5  | Training Times                                     | . 67  |

|         | 5.4.6  | Why Does it Do Well?                               | . 68  |

|         | 5.4.7  | When Does It Do Well?                              | . 69  |

|         | 5.4.8  | Additional Advantages of the Perceptron Predictor  | . 71  |

| 5.5     | Summ   | ary                                                | . 72  |

| Chapter | 6 Co   | ooperative Prediction with Branch Path Re-Aliasing | 82    |

| 6.1     | Branch | h Path Re-Aliasing                                 | . 84  |

|         | 6.1.1  | Path and Outcome Histories                         | . 84  |

|         | 6.1.2  | History Aliasing in a Global Predictor             | . 84  |

|         | 6.1.3  | Our Solution: Branch Path Re-Aliasing              | . 85  |

|         | 6.1.4  | Implementing Inversion Bits                        | . 88  |

| 6.2     | Result | s and Analysis                                     | . 88  |

|         | 6.2.1  | Predictor Simulation Methodology                   | . 89  |

|         | 6.2.2  | Algorithm Implementation                           | . 89  |

|         | 6.2.3  | How <i>not</i> to do Branch Path Re-Aliasing       | . 90  |

|         | 6.2.4  | Simple Two-Level Predictors                        | . 92  |

|         | 6.2.5  | More Complex Predictors                            | . 93  |

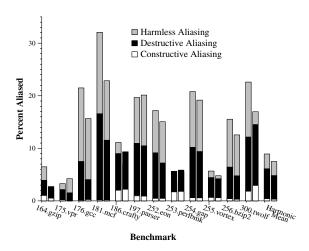

|         | 6.2.6  | Aliasing Rates                                     | . 98  |

| 6.3     | Limita | ations of Branch Path Re-Aliasing                  | . 99  |

| 6.4     | Summ   | ary                                                | . 100 |

| Chapter | . 7 Co | ooperative Prediction with Boolean Formulas        | 101   |

| 7.1     | Branch | h Prediction with Boolean Formulas                 | . 102 |

|         | 7 1 1  | Roolean Formulas as Branch Predictors              | 102   |

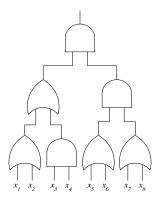

|         | 7.1.2   | Read-Once Monotone Boolean Formulas                         |

|---------|---------|-------------------------------------------------------------|

|         | 7.1.3   | Using Monotone Read-Once Formulas for Branch Prediction 104 |

|         | 7.1.4   | Profiling Algorithm                                         |

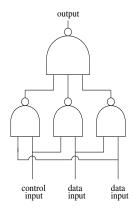

|         | 7.1.5   | Hardware Implementation                                     |

|         | 7.1.6   | Delay                                                       |

|         | 7.1.7   | Power                                                       |

|         | 7.1.8   | Impact of Encoding                                          |

| 7.2     | Results | and Analysis                                                |

|         | 7.2.1   | Methodology                                                 |

|         | 7.2.2   | Predictors Simulated                                        |

|         | 7.2.3   | Misprediction Rates                                         |

|         | 7.2.4   | Distribution of Formulas                                    |

|         | 7.2.5   | Profiling Cost                                              |

| 7.3     | Summa   | ary                                                         |

| Chapter | 8 Rel   | lated Work 124                                              |

| 8.1     | Hint Bi | its in Branch Predictors                                    |

| 8.2     | Combin  | ning Static and Dynamic Branch Prediction                   |

| 8.3     | Branch  | Prediction and Machine Learning                             |

|         | 8.3.1   | Neural Networks                                             |

|         | 8.3.2   | Genetic Algorithms                                          |

|         | 8.3.3   | Decision Trees                                              |

| 8.4     | Latency | y-Sensitive Branch Prediction                               |

| Chapter | 9 Co    | nclusions 129                                               |

| 9.1     |         | outions                                                     |

|         | 9.1.1   | Hierarchical Organizations                                  |

| Vita         |         |                                          | 146   |

|--------------|---------|------------------------------------------|-------|

| Bibliography |         |                                          | 137   |

| 9.3          | Final 7 | Γhoughts                                 | . 135 |

|              | 9.2.3   | Recommendations                          | . 134 |

|              | 9.2.2   | Advantages of Cooperative Predictors     | . 133 |

|              | 9.2.1   | Advantages of Hierarchical Organizations | . 133 |

| 9.2          | Compa   | arison of the Techniques                 | . 132 |

|              | 9.1.2   | Cooperative Predictors                   | . 131 |

# **List of Tables**

| 1.1 | Pipeline depth vs. clock rate for various processors                 |

|-----|----------------------------------------------------------------------|

| 3.1 | Parameters used for the simulations, similar to the Alpha 21264 21   |

| 3.2 | SPEC 2000 integer benchmark suite                                    |

| 4.1 | Projected clock rates using 8 FO4 Clock scaling                      |

| 4.2 | The best configurations of the PHT1 and PHT2 for the cascading and   |

|     | overriding predictors                                                |

| 5.1 | Perceptron Predictor Delay                                           |

| 5.2 | Best History Lengths for <i>gshare</i> and Perceptron 61             |

| 5.3 | Configurations for Large Budget Perceptron Predictors 63             |

| 7.1 | Access times for a 4K-entry gshare predictor vs. two versions of the |

|     | Boolean formula predictor                                            |

| 7.2 | Dynamic power consumption for two versions of the Boolean formula    |

|     | predictor and a 4K-entry gshare                                      |

| 7.3 | Distribution of Boolean formulas for a history length of 4           |

# **List of Figures**

| 1.1 | Instruction Throughput versus Capacity for the gshare predictor             | 4  |

|-----|-----------------------------------------------------------------------------|----|

| 2.1 | Bias in branches                                                            | 15 |

| 4.1 | Inter-branch latencies                                                      | 28 |

| 4.2 | Caching branch predictor                                                    | 30 |

| 4.3 | Cascading branch predictor                                                  | 31 |

| 4.4 | Overriding branch predictor                                                 | 33 |

| 4.5 | Pattern History Table capacity and access latencies                         | 35 |

| 4.6 | Misprediction Rate vs. Technology for the prediction strategies at $f_8...$ | 39 |

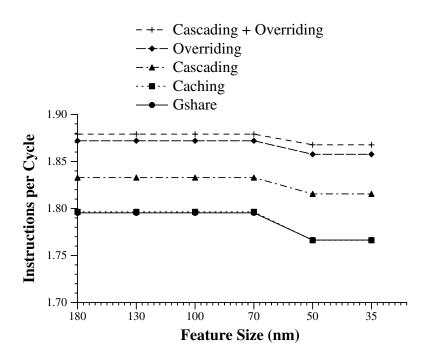

| 4.7 | IPC vs. Technology for the prediction strategies at $f_8$                   | 40 |

| 4.8 | Misprediction Rate vs. Clock Rate in 130 nm Technology                      | 42 |

| 4.9 | Clock Rate vs. IPC in 130 nm Technology                                     | 43 |

| 5.1 | Perceptron Model                                                            | 49 |

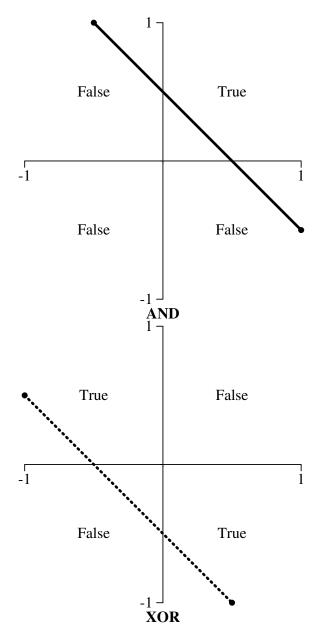

| 5.2 | Bipolar AND and XOR functions                                               | 74 |

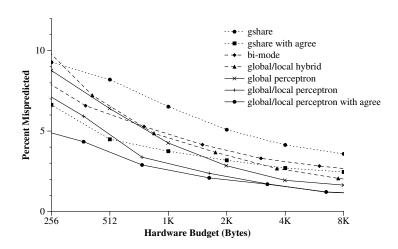

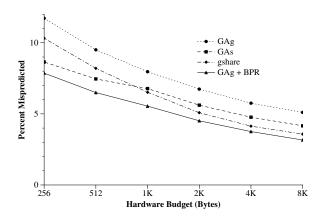

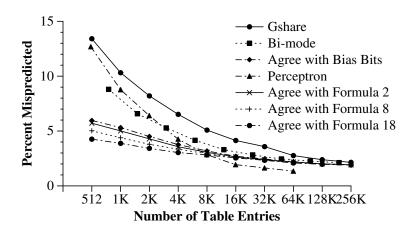

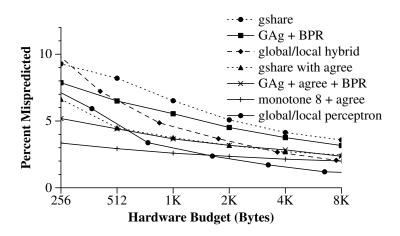

| 5.3 | Hardware Budget vs. Misprediction Rate on SPEC 2000                         | 75 |

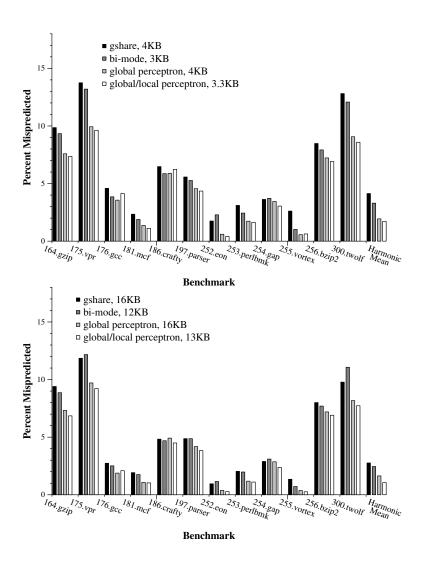

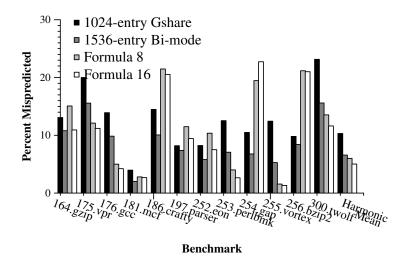

| 5.4 | Misprediction Rates for Individual Benchmarks at 4KB and 16KB Budgets       | 76 |

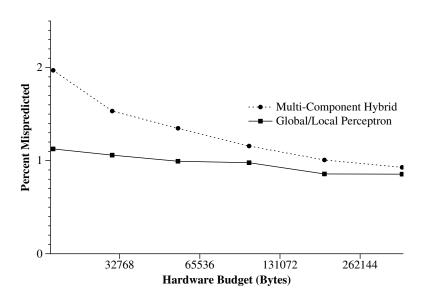

| 5.5 | Hardware Budget vs. Misprediction Rate for Large Predictors                 | 77 |

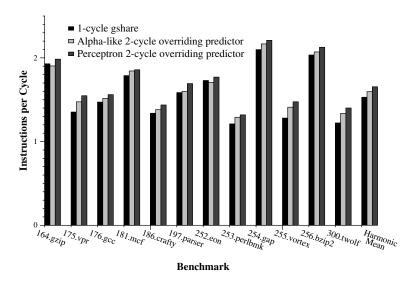

| 5.6 | IPC for overriding perceptron and hybrid predictors                         | 77 |

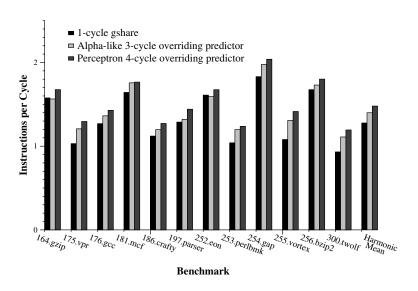

| 5.7  | IPC for overriding perceptron and hybrid predictors with long pipelines 7                                   | 78 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 5.8  | Average Training Times for SPEC 2000 benchmarks                                                             | 78 |

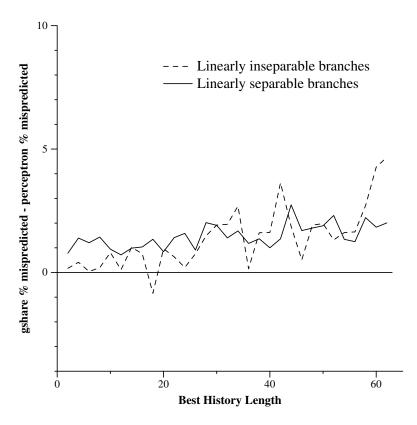

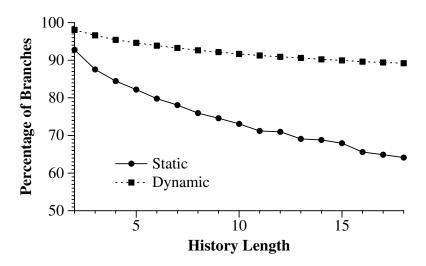

| 5.9  | History Length vs. Performance                                                                              | 79 |

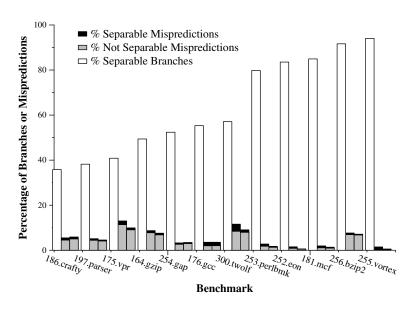

| 5.10 | Linear Separability vs. Accuracy at a 4KB budget                                                            | 79 |

| 5.11 | Classifying the Advantage of the Perceptron Predictor                                                       | 30 |

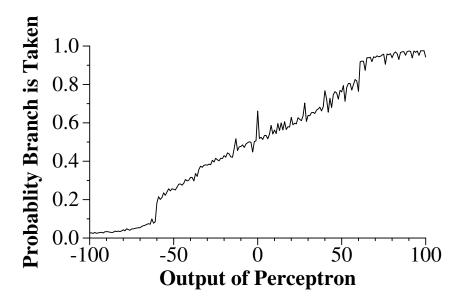

| 5.12 | Probability Branch is Taken as a Function of Perceptron Output 8                                            | 31 |

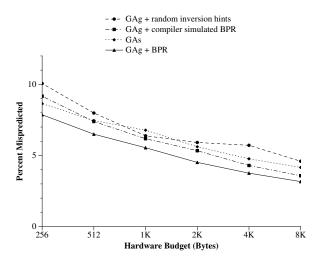

| 6.1  | Misprediction rates for alternate implementations of branch path re-aliasing,                               |    |

|      | along with GAs                                                                                              | 90 |

| 6.2  | Branch misprediction rates on the SPEC 2000 integer benchmarks 9                                            | 92 |

| 6.3  | Branch misprediction rates on each SPEC 2000 integer benchmarks for                                         |    |

|      | agree predictors                                                                                            | 95 |

| 6.4  | Branch misprediction rates on each SPEC 2000 integer benchmarks for                                         |    |

|      | hybrid and agree predictors                                                                                 | 97 |

| 6.5  | Branch aliasing rates on the SPEC 2000 integer benchmarks                                                   | 99 |

| 7.1  | Tree representation of the formula $((x_1 \lor x_2) \lor (x_3 \land x_4)) \land ((x_5 \lor x_6) \land x_4)$ |    |

|      | $(x_7 \vee x_8)$ )                                                                                          | )4 |

| 7.2  | Boolean connective subcircuit                                                                               | )8 |

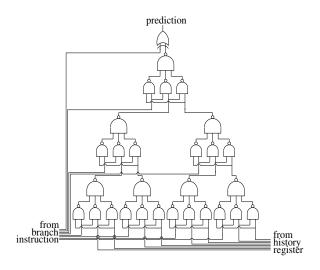

| 7.3  | Boolean formula branch predictor circuit for a history length of 8 10                                       | )8 |

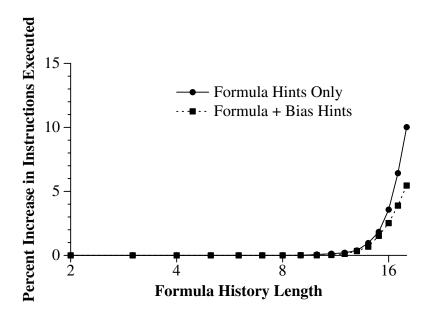

| 7.4  | Impact of Formula Encoding on Performance                                                                   | 13 |

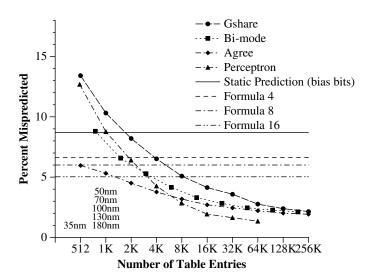

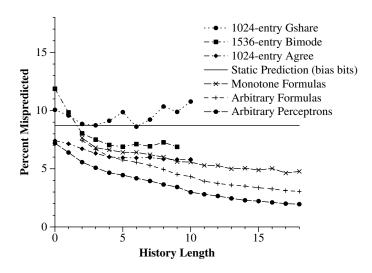

| 7.5  | Accuracy of dynamic branch predictors vs. static prediction and the Boolean                                 |    |

|      | formula predictor                                                                                           | 15 |

| 7.6  | Misprediction rate for the Boolean formula predictor as a function of his-                                  |    |

|      | tory length                                                                                                 | 18 |

| 7.7  | Accuracy of the predictors on each benchmark                                                                | 18 |

| 7.8  | Accuracies of Boolean formula predictors using the agree mechanism.        |     |

|------|----------------------------------------------------------------------------|-----|

|      | Misprediction rates are harmonic means over SPEC 2000                      | 120 |

| 7.9  | Percentage of branches using constant formulas at various history lengths. | 121 |

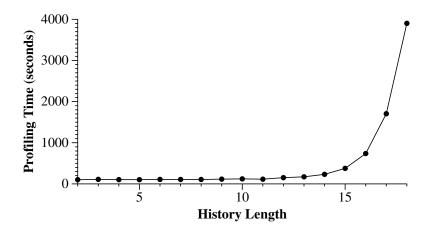

| 7.10 | Average, over all benchmarks, of the amount of time spent profiling as a   |     |

|      | function of history length                                                 | 123 |

| 9 1  | Misprediction Rates of Our Predictors                                      | 132 |

## Chapter 1

### Introduction

Modern microprocessors achieve good performance by executing many instructions in parallel. This instruction-level parallelism (ILP) can be limited by various bottlenecks, so microprocessors often perform speculative work to reduce the impact of these bottlenecks. One particularly important type of speculation is dynamic branch prediction. When a conditional branch instruction is fetched, it may take several cycles for the branch condition to be determined, and until then, it is not clear which path should be followed. A branch predictor uses statistical information to predict which direction the branch will take and to and speculatively fetch and execute instructions along the predicted path. This technique yields a tremendous increase in performance by keeping the pipeline full even in the presence of control hazards. Since about one in seven executed instructions is a branch, branch prediction is essential for modern pipelines that may have tens or even hundreds of instructions simultaneously in flight. If a prediction is incorrect, i.e. there is a misprediction, a considerable number of cycles is wasted executing the wrong instructions and restoring the processor state such that the correct path can be executed. Thus, branch predictors must be highly accurate to avoid mispredictions.

Current techniques can achieve correct branch prediction rates of 95% [41], i.e., *misprediction rates* of 5%, but the high cost of recovering from mispredictions [12] remains one of the largest impediments to performance on current and future processors. Because of the large penalty of a branch misprediction, small improvements in accuracy can have a large impact on performance. As pipelines become deeper to support higher clock rates, the penalty for a mispredicted branch will increase. For instance, the Pentium 4 microprocessor has a 20-stage pipeline, with a branch misprediction penalty of approximately 20 cycles [26]. For a simulated processor with a 20-stage pipeline, increasing the branch misprediction rate from 4% to 7% decreases performance by 11% in terms of instructions executed per cycle (IPC). Thus, we are motivated to find more accurate branch predictors for future technologies.

#### 1.1 The Problem: Delay in Branch Predictors

It takes work to accurately predict branches. The amount of time available to do this work has a large impact on the accuracy of the branch predictor. Branch predictor access delay is a crucial component in determining the performance of the processor, since it has an impact on both clock rate and instruction throughput. This delay is affected by trends in technology. In this section, we explain the source of branch predictor delay and the consequences of ignoring delay.

Modern branch predictors are based on the two-level adaptive branch prediction technique introduced by Yeh and Patt [62]. This scheme uses a table of counters to find correlations between previous branch outcomes to make a prediction. For the branch predictor to be accurate, this table should have hundreds or thousands of entries, causing it to resemble a small cache memory.

In the past three decades, performance improvements in microprocessors have been driven in large part by improvements in *process technology*, i.e., the process with which microprocessors are fabricated on wafers of silicon. As process technology improves, the sizes and delays of the transistors and wires on a microprocessor decrease, allowing computer architects to squeeze more functionality onto the chip, and run the chip at a higher clock frequency. Recent studies, however, have shown that as feature sizes have been shrinking in current and future process technology, increasingly aggressive clock rates and larger wire delays will lead to multi-cycle access to large on-chip structures [1] such as caches and branch predictors.

Until now, the huge body of branch prediction research has focused on only two dimensions of the problem—area and accuracy—and has found that larger hardware budgets yield higher accuracy for two reasons: They allow the use of longer history lengths, and they reduce *aliasing*, which occurs when two unrelated branches destructively share the same hardware branch prediction resources. Indeed, much of the recent work has focused on methods for reducing aliasing [52, 41, 38, 57, 18]. With growing chip capacities, the focus of the research community on area and accuracy has led to large elaborate predictors, some of which require 16K to 64K byte structures [20], and to complex prediction schemes that add levels of logic to combat destructive aliasing [18, 38].

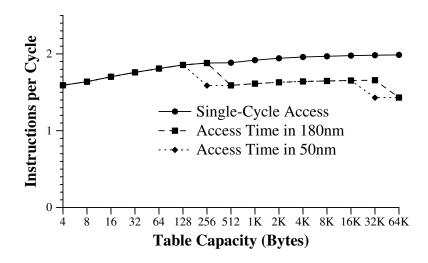

Since dynamic branch predictors use large tables to find correlations and make predictions, future branch predictors will need to consider a third dimension: delay. Figure 1.1 illustrates the problem of ignoring delay. Using an idealized delay of one cycle to access the pattern history table (PHT), the *gshare* predictor [41] sees improved *instructions per cycle* (IPC)—due to improved prediction accuracy—as the size of the PHT is increased. By contrast, with an aggressive clock frequency

(1.9 GHz) and a realistic delay model for today's 180 nanometer technology, the curve drops off at 512 bytes where the PHT requires two cycles to access, and drops again at 64KB where delay becomes three cycles. This problem will be exacerbated by the smaller process technologies of the future, as shown by the curve for 50nm technology and a projected 6.9 GHz clock rate. In this technology, wire delay causes the table access times to slip above one cycle even earlier.

Figure 1.1: Instruction Throughput versus Capacity for the *gshare* predictor.

As an example of a real-world instance of this problem, the branch predictor for the AMD Athlon microprocessor represents a step backward when compared to its predecessor, the K6. While the K6 has a highly accurate 8K-entry GAs predictor, the Athlon uses a less accurate 2K-entry GAs predictor [16]. This change reduces the delay and real estate costs of the branch predictor and could be one reason why the Athlon is able to achieve an aggressive clock rate of 1.4 GHz. Nevertheless, the Athlon has decreased performance in terms of IPC because of the less accurate branch predictor.

Higher clock rates also increase the need for higher branch prediction accuracy. As pipelines become deeper to create less work per cycle, the penalty of a misprediction increases. For example, the Pentium 4 has a 20 stage misprediction pipeline [26]. Table 1.1 shows the clock rates and pipeline depths of several current microprocessors.

In a nutshell, the problem is this: Using smaller branch prediction tables results in lower IPC because of lower accuracy. Naively using larger tables in future technologies results in even lower IPC because of aggressive clock scaling trends and increased relative wire delay. The question that this dissertation addresses is: how can we get both high accuracy and low latency?

#### 1.2 Dimensions of the Problem

As microarchitecture designs evolve and process technology improves, several dimensions of the branch predictor delay problem are emerging. In this section, we explore these dimensions, and ask important questions for the future of branch predictors.

#### 1.2.1 Extending Traditional Predictors in the Near Future

In the near future, i.e., the next few years, we would like to be able to continue using the traditional branch predictors that have provided such good performance in the past. Table-based branch predictors have been researched heavily. Industrial and academic researchers have very good ideas about how to extract a great deal of accuracy using variations of two-level adaptive predictors; we survey several of these efforts in Chapter 2. However, the impressive performance of these predic-

tors comes at the cost of high access delay. As pipelines deepen to support more and more aggressive clock rates in the near future, the viability of these schemes is threatened by the delay they impose. We can't simply throw away these schemes without having something to replace them with. Thus, we are highly motivated to find ways around the delay problem, so that we can extend the utility of these predictors into the future and continue building traditional cores with deeper pipelines and higher clock rates.

#### 1.2.2 Increasing Accuracy in the Face of Delay

Simply sustaining traditional branch predictors is not sufficient, especially since mispredictions are becoming more costly. How can we make the branch predictor more accurate if it has less time? As we have noted, a large amount of research has been done to improve the accuracy of table-based branch predictors. However, by no means do we believe that this research effort is finished. We believe that there are many more ideas yet to be discovered. Indeed, we introduce one such technique of our own in Chapter 5. How can highly accurate predictors with high access delays be used in processors with very short clock periods? Similarly, are there ways to use table-based predictors that result in high accuracy but are more economical with their time?

#### 1.2.3 Addressing Technology Scaling

As the limits of CMOS process technology scaling are approached in the next decade, wire delay and power will become dominant forces shaping processor design. Because of wire delay, the time it takes to access a reasonably large branch predictor may be a significant fraction of the time it takes an instruction to traverse

| Microprocessor  | Integer Pipeline Depth | Clock Frequency (MHz) |

|-----------------|------------------------|-----------------------|

| PowerPC 7400    | 4                      | 733                   |

| HP PA-8700      | 7                      | 800                   |

| Alpha 21264     | 7                      | 833                   |

| AMD Athlon      | 9                      | 1400                  |

| Intel Pentium 4 | 20                     | 1760                  |

Table 1.1: Pipeline depth vs. clock rate for various processors.

the pipeline. Thus, traditional table-based branch predictors may become infeasible or even useless in this new setting, and we will be forced to look for something new. Are there ways to accurately predict branches without tables or other expensive components?

#### 1.3 Our Solutions

Our solution to the problem of delay in branch predictors is to divide the prediction work into parts with different delays. During one part of the prediction, a fast branch predictor operates in a single cycle. During another part of the prediction, either off-line through profiling, or on-line through hardware, more time is spent working on making the branch predictor more accurate. We explore two main techniques for dividing the work:

**Hierarchical Predictors** We propose hierarchical organizations for branch predictors. We describe three branch predictor organizations, each with the common goal of combining a fast predictor with a slower but more accurate predictor to achieve accurate prediction in a single cycle. We apply these ideas in two contexts:

• We demonstrate how these techniques can be applied to conventional predic-

tors whose delay comes from table access time. Thus, we show how traditional predictors can be extended into the next several years of clock scaling and technology improvements.

• We explore the space of more complex predictors that would otherwise be infeasible because of delay: we describe a novel branch predictor based on a neural learning technique. This perceptron predictor has unique properties that allow it to yield high accuracy. Using the techniques described above, this complicated multi-cycle predictor can be used as a component of a fast delay-sensitive predictor. Thus, we show that ever more complex and accurate predictors are still feasible, even in the face of the branch predictor delay problem.

Cooperative Predictors Another way to tolerate delay is to off-load some of the prediction work to the compiler, with profiling. In this way, the compiler and hardware cooperate to produce the prediction. Prediction work takes place in two stages: First, an off-line profiling algorithm analyzes the program's behavior on a training input. The compiler communicates profiled information to the microprocessor using extensions to the instruction set architecture (ISA), indicating how to perform the branch prediction with high accuracy. Second, the instruction set communicates the hints to the branch predictor in the running program such that prediction is quick. We describe two novel techniques:

• *Branch path re-aliasing*, a technique that moves complexity off of the critical path for making a prediction and into the compiler. This technique increases accuracy by reducing destructive aliasing during the less critical update stage. This technique allows us to reduce branch predictor delay by shrinking a

branch predictor from one generation to the next without sacrificing accuracy. This technique is specific to one particular family of branch predictors.

• A branch predictor in which a profiling phase finds a function used to perform branch prediction for each branch. Each function is encoded as a compact Boolean formula in the branch instruction. The PHT is eliminated, so it is no longer a source of delay. This *Boolean formula predictor* has a small and fast hardware implementation and will work in less than one cycle even in the small technologies and aggressive clock rates for which conventional table-based predictors are infeasible.

#### 1.3.1 Scope and Limitations of the Research

In this dissertation, we focus mainly on the effects of technology scaling on the branch direction predictor. Thus, we mainly study the branch direction predictor in isolation, assuming for the sake of simplicity that other microarchitectural structures are not affected by technology scaling. We only briefly consider other related aspects of microarchitecture, such as branch target buffer delay, instruction cache delay, and branch predictor power, and we do not propose complete solutions to these problems. This methodology allows us to make stronger statements about the future of branch predictors themselves without relying on predictions of other components; however, without taking into account these other components, it is more difficult to interpret our simulated performance numbers. It is important to note that other problems may form more important bottlenecks, such as the increasing disparity between DRAM and CPU speeds, and that our IPC results may be optimistic by assuming that these problems will not get any worse.

#### 1.4 Thesis Statement

The central thesis of this dissertation is this:

Despite the effects of aggressive clock scaling, wire delay, and complex organizations, future branch direction predictors can have improved accuracy while still providing a prediction in a single cycle.

#### 1.5 Contributions

This dissertation makes the following contributions:

- We show that delay in the predictor significantly erodes performance, so future branch prediction work must consider delay in their designs. We show that increasing delay to improve accuracy is never a good tradeoff. We show that structures with multi-cycle access times can be exploited by hierarchical organizations for branch predictors.

- 2. We introduce the perceptron predictor, the first dynamic predictor to successfully use neural networks, and we show that it is more accurate than existing dynamic global branch predictors. For example, for a 4K byte hardware budget, our global predictor achieves a misprediction rates on the SPEC 2000 integer benchmarks of 1.94%, compared with 4.13% for a *gshare* predictor of the same size and 2.66% for the McFarling-style hybrid predictor of the Alpha 21264. A version of our predictor that uses both global and per-branch information improves the misprediction rate to 1.71%, an improvement of 36% over the hybrid predictor. By comparing our predictor against a multicomponent hybrid predictor, we provide evidence that the perceptron predictor is the most accurate fully dynamic branch predictor known. We suggest

- how, using hierarchical organizations, the perceptron predictor can be implemented and used in modern CPUs. We show that the perceptron predictor can improve IPC by 15.8% over *gshare* and 5.7% over a hybrid predictor.

- 3. We present branch path re-aliasing, a technique in which the compiler reduces destructive aliasing by setting a hint bit in the ISA, thereby allowing some dynamic predictors to use smaller tables more effectively. We describe an algorithm for using path profiles to set these hint bits. We present experimental evidence that branch path re-aliasing allows small branch predictors to achieve greater accuracy than other, slower predictors. Our simulations show that a 2048-entry GAg predictor enhanced with branch path re-aliasing has a misprediction rate of 6.5%, 21% lower than the misprediction rate of 8.2% for the same sized, but more complicated, *gshare* predictor, and equivalent to the misprediction rate of a *gshare* predictor with twice the size. We also show that our technique improves accuracy even for the *agree* predictor, which was designed to convert destructive aliasing into constructive aliasing, and we show that our technique can improve the accuracy of complex predictors, such as the hybrid predictor of the Alpha 21264.

- 4. We present a new method for branch prediction based on Boolean formulas that breaks the trade-off between delay and accuracy. For instance, in one cycle, our predictor can deliver a prediction with the accuracy of a 8K-entry *gshare* predictor in a technology where only a 512-entry *gshare* predictor can be accessed in one cycle. We describe the hardware implementation of our predictor, showing that it has one third of the delay and consumes 1% of the power of a conventional branch predictor. We describe a profiling algorithm for training our predictor.

### Chapter 2

## **Background**

To familiarize the reader with the ideas of branch prediction, as well as help place our work in its proper context, we now provide some background into branch prediction. We review the history of branch prediction, explain the basic mechanism, describe characteristics of branch predictors, and review some implemented branch predictors. We also provide background into the technology scaling issues addressed by our work.

#### 2.1 History of Branch Prediction

Branch prediction has a long history in high performance computing. In first survey of branch prediction strategies, Smith describes mechanisms already in place in mainframe computers at the end of the 1970's [56]. Most of these mechanisms are simple, and are based on static characteristics of the program. For example, some IBM System 360/370 models predict whether a branch will be taken based on the branch instruction opcode, since certain opcodes are used for loop back edges and other are used for IF/THEN/ELSE statements [56]. Another simple static mechanism is to predict that a backward branch will be taken, while a forward branch will

not, observing that backwards loop back edges are frequently traversed more than once. Smith also proposes simple dynamic branch predictors. The basic idea is to use a hash of the branch address as an index into a table of counters that are incremented when the branch is taken, decremented otherwise. When branch prediction is required, the high bit of the corresponding counter is used as the prediction; 1 means *predict taken*, and 0 means *predict not taken*. These historical prediction mechanisms were moderately accurate, but as branch misprediction penalties started to increase, more accurate techniques became necessary.

An important breakthrough came in 1991 when Yeh and Patt observed that the outcome of a given branch is often highly correlated with the outcomes of other recent branches [62]. This history of branch outcomes forms a pattern that can be used to provide a dynamic context for prediction. Most modern branch predictors are based on this pattern history. In the scheme of Yeh and Patt, every time a branch outcome becomes known, a single bit (0 for not taken, 1 for taken) is shifted into a pattern history register. A pattern history table (PHT) of two-bit saturating counters is indexed by a combination of branch address and history register. The high bit of the counter is taken as the prediction. Once the branch outcome is known, the counter is decremented if the branch is not taken, or incremented otherwise, and the pattern history is updated. Recent branch prediction work focuses on refining this scheme of Yeh and Patt. Several predictors have been proposed to deal with the problem of destructive aliasing, which occurs when two unrelated branches contend for the same PHT resources, resulting in decreased accuracy [38, 57, 18]. Hybrid predictors that combine two branch predictors to improve accuracy have been proposed [41, 20] and implemented [35]. The 1990's produced a great deal of research in improving branch predictor accuracy and studying characteristics of branch prediction, and we expect this research to continue.

#### 2.2 Characteristics of Branch Prediction

Several factors influence the design of branch predictors:

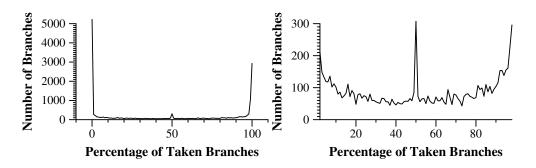

**Branches are biased.** Branches, which can only have two outcomes, *taken* and *not taken*, are highly biased. For instance, a branch that transfers control from the end of a loop back to the beginning will usually be *taken*, since loops usually iterate many times before finishing. Figure 2.1 shows the bias of dynamic branches in the SPEC 2000 integer benchmark suite. The x axis gives the *bias* of a branch, i.e., the percentage of time a branch is *taken*, and the y axis shows the number of branches with a given bias in the SPEC 2000 integer benchmarks. Of all branches, 53% are *taken* at least 98% or at most 2% of the time. The graph on the right excludes these branches, again showing clear biases and a number of branches taken exactly half the time.

Only frequent branches matter. For a conditional branch to have a significant impact on the performance of a program, it must be executed many millions of times. It doesn't matter if a low-frequency branch is incorrectly predicted, because its overall impact on the program's speed is low. Most branches are executed very few times, so it makes sense to concentrate our effort on those few branches that are executed frequently.

**Branch predictors must be fast.** Branch predictors must meet strict physical constraints. They must operate in one CPU cycle and be small enough to fit on a chip. Most of the hardware devoted to branch predictors is memory for large tables, so the *hardware budget* of a predictor, i.e., the cost of the predictor as a component of the chip, is appropriately measured in kilobytes. A typical predictor occupies 4K

bytes of SRAM [35]. However, as we will see, the amount of area reachable in one cycle will decrease in future technologies.

**Aliasing is a problem.** One problem with dynamic branch prediction schemes is *aliasing*, where the limited resources cause two unrelated branches to use the same prediction resources, resulting in poor performance. Many techniques have been proposed to reduce the impact of aliasing [41, 38, 57, 18]. As the amount of resources reachable in one cycle decreases, this problem will become more difficult to solve.

Figure 2.1: Bias in branches.

#### 2.3 Branch Prediction Mechanisms

This section provides background in several branch prediction mechanisms, paying particular attention to branch predictors that directly relate to the research presented in this dissertation.

#### 2.3.1 GAg and GAs Predictors

Our work on branch path re-aliasing focuses on improving the accuracy of GAg branch predictors. Although more accurate predictors exist, GAg and its close relative, GAs, are both used as components of implemented branch predictors in modern machines, as we will see in Section 2.3.6. Yeh and Patt taxonomize two-level branch predictors using a three-letter naming scheme [63]. The first letter represents how the first level branch history is kept. G means a single global history register is used. The second letter denotes the prediction mechanism: A means that a two-bit saturating counter is used. The third letter indicates how the second level table is indexed; g means a single column of counters is used for all addresses while s means that bits extracted from the branch address are used to select a set of counters, and the set is indexed by the history register. Thus, a GAs predictor selects a set of counters from a pattern history table (PHT) using bits from the branch address, and chooses a particular counter from that set using bits from the global history. A GAg predictor uses only the global history to index the PHT.

#### 2.3.2 gshare predictor

One popular variant of the GAs predictor is *gshare* [41]. A *gshare* predictor combines the branch history and branch address by exclusive-ORing them together. The exclusive-OR operation has the effect of evenly distributing accesses to the PHT, which would otherwise be unequally distributed due to the non-uniform nature of branch histories. In this way, *gshare* increases accuracy by reducing the probability that two different branches will interfere with each other in the PHT.

#### 2.3.3 Agree predictors

A branch direction predictor can be enhanced using the *agree* mechanism [57]. Rather than correlating with branch outcome, the PHT entries in an *agree* predictor keep track of whether a branch outcome will agree with a bias bit set in the branch instruction. The *agree* mechanism turns destructive interference into constructive interference, increasing accuracy. However, since the branch instruction opcode must be read and combined with the PHT prediction, the instruction cache is on the critical path for branch prediction. Note that branch biases can be learned and stored in the branch target buffer rather than branch instruction.

#### 2.3.4 Bi-Mode predictor

Several other branch predictor organizations have been proposed to reduce destructive aliasing in the PHT. We choose the Bi-Mode predictor [38] as a representative of these predictors. The Bi-Mode predictor uses three history tables: two PHTs and a choice table that is used to indicate which PHT to use for a particular combination of branch address and history. Details of this predictor allow it to reduce aliasing by separating into different tables histories that would destructively alias one another, at the cost of increased complexity in the organization.

#### 2.3.5 Static Branch Prediction

A purely static branch predictor always predicts the same outcome for a particular static branch. The prediction can be derived from the structure of the branch itself, e.g., the "backwards taken/forwards not taken" approach of the Alpha AXP-21064, or encoded into the branch instruction itself as a bias bit, as in the IA-64 instruction set. The compiler, through profiling or static heuristics [6, 11], can provide hints to

the microarchitecture about the likely direction of the branch. Given enough state, dynamic branch predictors are more accurate than static branch predictors, since dynamic predictors take into account changing conditions at run-time.

#### 2.3.6 Branch Predictors in Current CPUs

Current microprocessors use two-level branch predictors. The following are three notable examples:

- The AMD K6 and K7 (Athlon) processors use GAs predictors [16].

- The HP-PA 8700 uses a 2048-entry GAs with the agree mechanism [39, 59].

- The Alpha 21264 core uses a hybrid predictor composed of two two-level predictors [35]: a 4K-entry GAg is indexed by a 12-bit global branch history while a 1K-entry PHT of 3-bit saturating counters is indexed by one of 1024 local 10-bit branch histories. The final branch prediction is chosen by indexing a third predictor that keeps track of the relative accuracies of the two predictors for a particular global history. The Alpha predictor is very accurate; indeed, it is the most accurate of implemented branch predictors that we have observed. However, its implementation complexity comes with a cost. The Alpha branch predictor overrides a less accurate instruction cache line predictor, introducing a single-cycle bubble into the pipeline whenever the two disagree [35].

# 2.4 Technology Scaling

Branch predictors, like other microarchitecture structures, are affected by two technology scaling trends. Microprocessor designers continue to aggressively increase

the clock rates, outstripping the speed improvements achieved by transistors that have smaller gate lengths in each successive technology [1]. Furthermore, at smaller feature sizes, wire delay grows in significance relative to transistor speeds and can affect the latency of the fetch engine and the branch predictor. Faster clocks exacerbate the tradeoff between capacity and delay in microprocessor components. As these trends continue, the chip area reachable in a single cycle will decrease. This means that large banks of SRAM, such as caches and branch prediction tables, will have to either decrease in size or increase in delay. Branch prediction tables are particularly hard hit by clock scaling because they require more address lines than similarly sized caches because caches have wide lines, while branch predictors have narrow two-bit entries. These extra address lines cause significant decoder delay.

To account for accelerating clock rates, we use a technology independent metric, the fanout-of-four (FO4) delay metric, to measure clock period [27]. One FO4 delay is the time for an inverter to drive 4 copies of itself. Reasonable models show that under typical conditions, the FO4 delay, measured in picoseconds, is equal to  $360 \times L_{drawn}$ , where  $L_{drawn}$  is the minimum gate length for a technology, measured in microns. The number of FO4 delays in a clock period is an indicator of the number of levels of logic in a pipeline stage. An example of an aggressive clock rate is  $f_8$ , which corresponds to a clock period of 8 FO4 delays. The current trends in pipeline depths and clock rates suggest that a clock rate near  $f_8$  may be used in real microprocessors in the near future.

# **Chapter 3**

# Methodology

In this chapter, we explain the general methodology we use to obtain our experimental results. Later sections will go into more detail where appropriate. There are three main types of results that we gather: branch misprediction rates, instructions per cycle (IPC), and circuit timings. We gather these statistics in the context of a out-of-order core simulator based on the SimpleScalar/Alpha simulator [10].

# 3.1 Simulated Microprocessor

We use the SimpleScalar/Alpha out-of-order simulator, configured with microarchitectural parameters similar to those of the Alpha 21264 [35]. We choose this microarchitecture because it is recognized as a leading-edge high performance microprocessor. Since we are focusing solely on the branch predictor, we keep the other structure sizes constant at values shown in Table 3.1. This means that, as we scale feature sizes and clock rates, we assume that the number of cycles to access other structures will not change. Although this is an optimistic assumption, it allows us to isolate the effect of the branch predictor. We assume a baseline microarchitecture with a five-stage pipeline and issue width of four; however, we investigate

|                | Capacity |           |            |       |

|----------------|----------|-----------|------------|-------|

|                | (bits)   | # entries | Bits/entry | Ports |

| BTB            | 48K      | 512       | 96         | 1     |

| Reorder buffer | 8K       | 64        | 128        | 8     |

| Issue window   | 800/320  | 20        | 56         | 8     |

| Integer RF     | 5K       | 80        | 64         | 10    |

| FP RF          | 5.6K     | 72        | 80         | 10    |

| L1 I-Cache     | 512K     | 1K        | 512        | 1     |

| L1 D-Cache     | 512K     | 1K        | 512        | 2     |

| L2 Cache       | 16M      | 16K       | 1024       | 2     |

| I-TLB          | 14K      | 128       | 112        | 1     |

| D-TLB          | 14K      | 128       | 112        | 2     |

Table 3.1: Parameters used for the simulations, similar to the Alpha 21264.

multiple pipeline depths simulated by changing the misprediction penalty. Note that an issue width of four is conservative; as issue width increases, branch prediction becomes even more important since more work is wasted on a misprediction.

By changing the number of cycles for the branch misprediction penalty and for accessing the branch predictor, we simulate the effect of increasing the clock rate and the depth of the pipeline.

#### 3.2 Benchmarks

We simulate the 12 programs in the SPEC CPU 2000 suite of integer benchmarks. The programs are compiled on an Alpha 21264 workstation using the Compaq C compiler V6.3-025 and g++ compiler version 2.9-gnupro-99r1 The optimization levels are chosen from the peak settings for the SPEC-supplied configuration files. Table 3.2 shows the name of each benchmark, along with a short description.

| Benchmark   | Description                      |  |

|-------------|----------------------------------|--|

| 164.gzip    | LZ77 compression                 |  |

| 175.vpr     | Place and route for FPGAs        |  |

| 176.gcc     | C compiler for Motorola 88100    |  |

| 181.mcf     | Minimum cost network flow solver |  |

| 186.crafty  | Chess playing program            |  |

| 197.parser  | Natural language processing      |  |

| 252.eon     | Ray-tracing program              |  |

| 253.perlbmk | Perl                             |  |

| 254.gap     | Computational group theory       |  |

| 255.vortex  | Database                         |  |

| 256.bzip2   | Block-sorting compression        |  |

| 300.twolf   | Place and route                  |  |

Table 3.2: SPEC 2000 integer benchmark suite.

# 3.3 Branch Misprediction Rates

We use the following methodology when reporting branch misprediction rates.

#### 3.3.1 Simulated Branch Predictors

Most of the branch predictors studied are simulated in a C++ framework that is patched into the SimpleScalar/Alpha branch prediction system. The framework can also function in a stand-alone trace-driven simulator. The framework currently supports the following branch predictors:

1. Two-level adaptive branch prediction [62]. This category includes predictors such as *gshare* and other predictors that index a pattern history table (PHT) using a combination of branch address and global (e.g. as in *gshare*) or perbranch history information. The parameters to a two-level predictor are history length, size of the PHT, number of per-branch histories to keep, number

- of bits per counter, and whether or not to exclusive-OR the branch address with the branch history (as in *gshare*).

- 2. Hybrid branch prediction [20]. Any two simulated branch predictors can be combined into a hybrid predictor. A table of two-bit saturating counters indexed by global history and/or branch address is used to keep track of which predictor performs best for which branch, and the prediction from the better predictor is returned. The hybrid predictor of the Alpha 21264 is simulated using this mechanism. The parameters are the size of the chooser table and the sort of information that should be used to index it.

- 3. The *bi-mode* predictor [38]. The parameters are the size of each pattern history table and the global history length.

- 4. The Agree predictor [57]. A method call allows the user to read a table of bias bits into any branch predictor. The table is then used to implement the *agree* mechanism in that predictor.

- 5. Perceptron prediction [33]. The parameters are the number of perceptrons, the number of per-branch history bits, the number of global history bits, the number of per-branch histories to keep, and the threshold value  $\theta$ .

We used this framework to write many trace-driven simulators, testing different areas of our research. The Boolean Formula predictor is simulated alongside this framework, using separate data structures.

## **3.3.2 Tuning Branch Predictors**

It has been observed that branch predictor accuracy is sensitive to history length [41]. We tune each predictor for history length using traces gathered from the each of the

12 benchmarks and the train inputs. The traces record the address and outcome (i.e., taken or not taken) of up to 300 million branches for each benchmark. We exhaustively test every possible history length at each hardware budget for each predictor, keeping the history length that yields the lowest harmonic mean misprediction rate. For the *agree* mechanism, we set bias bits in the branch instructions using branch biases learned from the train inputs.

#### 3.3.3 Testing Branch Predictors

For each benchmark, we gather traces giving the branch address and outcome for 300 million branches for both train and ref inputs. Each benchmark executes over one billion instructions before the simulation ends. In our simulations, we skip the first 50 million branches before beginning to record branch prediction accuracy; we have observed that the benchmarks exhibit highly predictable initialization behavior before this time, and then settle into a steady-state.

# 3.4 Instructions per Cycle

For generating instructions per cycle (IPC) results, we use a modified version of the sim-outorder simulator from SimpleScalar/Alpha that uses our branch prediction framework. We simulate each benchmark, measuring the number of cycles and instructions executed, and add in a number of cycles equivalent to the various delays or penalties associated with the particular experiments. We then divide the number of retired instructions by the number of cycles used. Note that this methodology fails to capture some of the wrong-path effects such as cache pollution that would actually be observed in a real latency-sensitive branch predictor; however, these effects are small. For experiments that require fewer than 1000 executions

of the performance simulator, we run each benchmark for one billion instructions. For experiments that require more than 1000 executions, we run each benchmark for 500 million instructions. For instance, tuning a predictor to search a large design space may require many thousands of executions, but getting results using an already tuned set of configurations may require only dozens or hundreds of executions.

## 3.5 Circuit Timings

Several of our experiments require analysis to determine the delay of circuit components such as pattern history tables and computational elements related to the perceptron and Boolean formula branch predictors.

#### **3.5.1 HSPICE**

We simulate combinational logic circuits using the HSPICE simulator. The HSPICE simulations use transistor models tailored to fabrication processes to simulate the circuit behavior for several technology generations, from current generations with minimum feature (transistor and wires) sizes of 180nm down to future generations that will have minimum feature sizes of 35nm.

#### 3.5.2 **CACTI**

To estimate pattern history table access times for a range of current and future integrated circuit generations, we use circuit simulations and a modified version [2] of the CACTI 2.0 tool for simulating cache delay. This modified version of CACTI is more accurate than the original in several ways. First, while the original version of CACTI 2.0 [49] uses a simplistic linear scaling for delay estimates, the modified

simulator uses separate wire models to account for the physical layout of wire interconnects: thin local interconnect, taller and wider wires for longer distances, and the widest and tallest metal traces for global interconnect. Second, wire resistance is based on copper rather than aluminum material properties. Third, all capacitance values are derived from three-dimensional electric field equations. Fourth, bit-lines are placed in the middle layer metal, where resistance is lower. Finally, bit-addressing is allowed instead of byte-addressing. Our versions of HSPICE and CACTI both use the same parameters for technology scaling.

# 3.6 Computing Facilities

We run our simulations on a network of approximately 200 Pentium III computers using the Condor system for coordinating the execution of many jobs [8].

# **Chapter 4**

# **Hierarchical Organizations**

In this chapter, we examine three organizational approaches for dealing with delay in future process technologies: (1) a two level caching scheme, (2) an *overriding* scheme that allows a first prediction to be overturned by a more accurate second prediction, and (3) a *cascading* lookahead scheme that exploits cycles between branches to do prediction work. We show that delay in the predictor significantly erodes performance, so future branch prediction work must consider delay in their designs. We show that increasing delay to improve accuracy is never a good tradeoff. We show that there are approaches to branch prediction that can effectively use large structures with multi-cycle access times, and give experimental results showing that IPC can be sustained using these techniques.

#### 4.1 Motivation

Larger branch prediction structures lead to larger access delays. Aggressively increasing clock rates (as the marketplace demands) increases the structure access time as measured in clock cycles.

Our studies show that it is never worth increasing the delay of a branch pre-

Figure 4.1: Inter-branch latencies

dictor for the sake of improved accuracy [32]. For example, Figure 1.1 shows that as we increase the capacity of the tables in gshare, we increase delay and decrease IPC. This effect can be explained with the following equation which roughly approximates the cost C of executing a branch instruction:

$$C = d + (r \times p)$$

where d is the delay of branch predictor, r is the misprediction rate, and p is the misprediction penalty. While the delay d may not always be on the critical path of the pipeline, increasing d will reduce the instruction fetch bandwidth to the execution cores. Because misprediction rates tend to be below 10%, changes in delay have a larger impact than small changes in r for practical values of d (i.e., for forseeable pipeline depths).

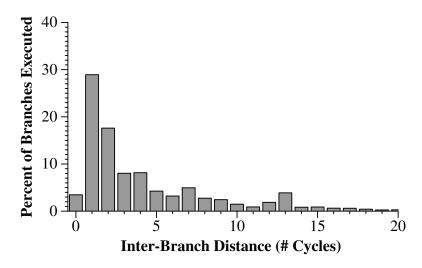

## **4.2** Branch Frequency

A program's control behavior is based not only on the predictability of its branches, but also on the branch frequency. If branch prediction is required on every clock cycle, any delay in branch prediction will substantially slow the instruction fetch rate. However, if branches are widely spaced, then branch prediction latency will have less impact on performance. While the common wisdom is that branches occur on average every fourth or fifth instruction, we find that, in our framework (i.e., a real-world optimizing compiler on the Alpha), branches actually occur one every nine instructions, on average. The actual dynamic distribution of inter-branch latencies is more instructive. We use SimpleScalar/Alpha [10] to measure the average branch frequency the twelve SPEC 2000 integer benchmarks on a 4-way out-oforder machine configuration. Figure 4.1 is a histogram of average inter-branch latencies, measured in cycles between prediction requests, for the SPEC 2000 integer benchmarks. Over 67% of the prediction requests occur more than one cycle after the previous request. The unused cycles provide additional time to predict future branches. For wider issue machines, there is less additional time to make a prediction.

# 4.3 Hierarchical Organizations for Latency Sensitive Branch Predictors

In this section, we describe three ways to configure branch predictors to increase accuracy in the face of increasing latency. These techniques are appropriate when standard techniques for branch prediction might exceed one cycle, and these are general techniques that can be applied to most prediction algorithms.

To achieve high prediction accuracy, the branch predictor may require larger

Figure 4.2: Caching branch predictor

tables. The goal of the microarchitect is to achieve accuracy approaching that of a large table, with the latency of a small table. We examine three methods for achieving this goal.

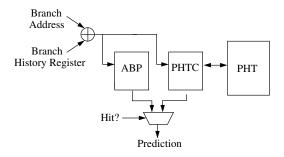

#### **4.3.1** Caching Prediction Tables

The first strategy to combat the long latency of large branch prediction tables is to build a small cache of branch prediction table entries. This strategy allows us to realize the benefits of reduced aliasing and increased history length without the added latency of the large table, since the cache will have an access time of one cycle. For instance, a 128K-entry PHT accessible in two cycles can be cached using a 1K-entry PHT accessible in one cycle. Figure 4.2 shows the organization of the *gshare* predictor augmented by a cache. The branch history and branch address are hashed using the XOR gate, and the resulting address is sent to both the pattern history table cache (PHTC) and the pattern history table (PHT). The PHT consists of 2-bit saturating counters, with the number of counters equal to the number of combinations of addresses produced by the hash function. The PHTC caches a subset of those counters in a smaller table that can be accessed more quickly than

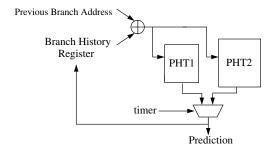

Figure 4.3: Cascading branch predictor

the PHT. If the correct counter is found in the PHTC, then the prediction can be made immediately. If a miss in the PHTC occurs, then the PHT must be consulted to find the correct saturating counter. Like traditional caches, an entry in the PHTC is replaced with the correct counter from the PHT. When the branch direction is determined during a later stage of the execution pipeline, the counters in the PHT and PHTC are updated to reflect the correct or incorrect prediction of that branch.

If a PHTC miss occurs, the wait for the correct prediction from the PHT will delay instruction fetch and will degrade overall performance. Two alternatives can be used to prevent this additional delay. First, the prediction produced by the PHTC, albeit for the wrong branch, can be used. Alternatively, we suggest building a small auxiliary branch predictor (ABP) that can be accessed at the same time as the PHTC. If the PHTC misses, then the result from the ABP is used.

## 4.3.2 Cascading Lookahead Branch Prediction

Lookahead branch prediction has been proposed as a mechanism to increase fetch bandwidth by generating addresses for future branches [64, 54] (see Chapter 8 for more related work). The same technique can be applied to reduce the impact of

longer latency branch predictors. If the branch predictor is not needed on every cycle, then natural spacing between branches can be used to perform a prediction for the next branch that is likely to arrive. Thus, if branches are spaced so that the predictor is accessed only every other cycle, the predictor can have a two cycle latency without introducing additional delay. Figure 4.1 shows us that the predictor is usually needed at most once every other cycle.

The *gshare* predictor can be adapted to look one branch ahead. While *gshare* uses the branch history register and branch address to compute the PHT address, a lookahead predictor uses the predicted history and the address of the most recently fetched branch. Since the prediction can complete before the next branch arrives at the predictor, prediction is instantaneous. However, if the prediction requires multiple cycles (due to a large table) and the next branch arrives before the prediction is complete, the instruction fetch engine stalls.

Cascading lookahead branch prediction implements a series of tables of ascending size and latency. Figure 4.3 shows a two-level cascading predictor. Like a lookahead predictor, the next prediction is based on the last prediction and the last branch address. Prediction begins simultaneously on both levels of the cascading predictor. If the latency to the next branch to be predicted is large, then the prediction from the second level table is selected. If the next branch arrives before the second level table can complete its access, then the prediction from the first level table is used.

Thus, the combination of a small first level table and a larger second level table can provide better aggregate accuracy with the minimum latency. However, the utility of the larger table depends on its access time and the inter-branch latency. If branches occur extremely frequently, the second level of the cascade will not be used. The cascading design can be trivially extended to more than two levels.

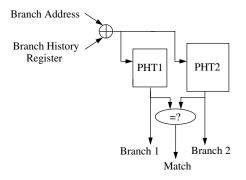

Figure 4.4: Overriding branch predictor

Furthermore, hybrid predictors of varying latencies can be incorporated into the cascading strategy. In our description above, the logic that selects the prediction to use is based only on the arrival time of the next branch. More complicated selectors could trade off latency versus accuracy by predicting which of many predictions is best for the subsequent branch.

## 4.3.3 Overriding Branch Predictor

An overriding branch predictor (Figure 4.4) provides two predictions. The first prediction comes from a fast PHT (PHT1), and the second prediction comes from a slower, but more accurate PHT (PHT2). When branch prediction is requested, the first prediction is used and acted upon while the second prediction is still being made. If the second prediction differs from the first prediction, the actions taken based on the first prediction are squashed and instructions are fetched using the second prediction; thus, the second predictor overrides the first predictor. For the overriding scheme, we assume that the penalty of restarting an overridden fetch is equal to the delay of PHT2. A similar technique is used in the Alpha 21264, in which the branch predictor, whose results become known only in the second stage

| Gate | 8FO4 Clk    |  |  |

|------|-------------|--|--|

| (nm) | $f_8$ (GHz) |  |  |

| 180  | 1.9         |  |  |

| 130  | 2.7         |  |  |

| 100  | 3.5         |  |  |

| 70   | 5.0         |  |  |

| 50   | 7.0         |  |  |

| 35   | 10.0        |  |  |

Table 4.1: Projected clock rates using 8 FO4 Clock scaling.

of the pipeline, can override the less accurate instruction cache line predictor [35] with a single-cycle penalty. We assume the predictor is pipelined such that no branch needs to wait for the completion of a PHT2 lookup for a previous branch.

# 4.4 Technology Scaling

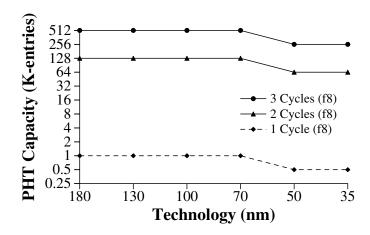

Table 4.1 lists the technologies that we consider and the clock rates that result from aggressive ( $f_8$ ) scaling. We base our estimates of branch predictor delay on the access time of the memory-oriented structures such as the pattern history table (PHT). To model PHT delay, we use the methodology described by Agarwal, et al. [1], which augments the CACTI cache delay modeling tool [49] with scaled technology parameters. We convert the access time produced by the augmented CACTI model into cycles, according to the  $f_8$  clock scaling strategy. As shown in Figure 4.5, only small tables of 1024 entries can be accessed in a single cycle, and at 35nm, only 512 entries can be accessed in one cycle. Accepting a 2 or 3 cycle delay increases the capacity to 16K and 64K entries, respectively.

Figure 4.5: Pattern History Table capacity and access latencies.

# 4.5 Results and Analysis

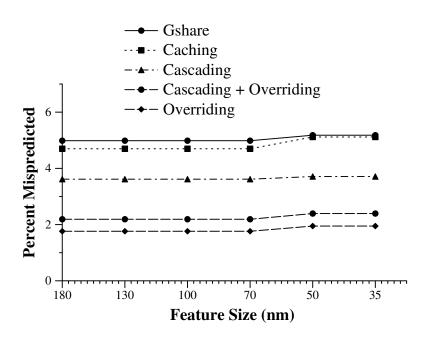

In this section we evaluate the three latency sensitive branch predictors and compare them to *gshare* across a spectrum of process technologies. In addition, we evaluate a fourth predictor that combines the cascading and overriding predictors. This predictor uses a cascading predictor that continues predicting after the branch has been encountered, overriding the first prediction if the second prediction is different.

We used the methodology outlined in Chapter 3 to evaluate the different prediction strategies described above using delay estimates at seven process technologies ranging from 180 nm to 35 nm, representing technologies from today to the predicted smallest feature sizes for which conventional CMOS will be feasible. Each sim-outorder simulation runs for 500 million instructions. In the simulations, the global pattern history register is updated speculatively and backed up on a mispredict, while updates to the PHTs are done when the updating branch commits.

We report two types of results. First, we give results using an aggressive