## DESIGN AND PERFORMANCE EVALUATION OF THE TEXAS OBJECT BASED SYSTEM

by

GAD JOSEF DAFNI, B.SC., M.SC.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December, 1986

# DESIGN AND PERFORMANCE EVALUATION OF THE TEXAS OBJECT BASED SYSTEM

APPROVED BY SUPERVISORY COMMITTEE:

Donnie J. J. pouls.

A. Selberselag

Mill Molloy

K. M. Chardy

## DESIGN AND PERFORMANCE EVALUATION OF THE TEXAS OBJECT BASED SYSTEM

Gad Joseph Dafni

Department of Computer Sciences The University of Texas at Austin Austin, Texas 78712-1188

TR-87-04 January 1987

Copyright

by

Gad Josef Dafni

1986

#### **ACKNOWLEDGEMENTS**

I would like to thank those who helped me to complete this research with their guidance and support. My deepest gratitude is reserved to Dr. James C. Browne for his faithful guidance and inspiration. I am also grateful to Dr. A. Silberschatz for his important help and for providing me financial support through research assistantship. I wish to thank the members of my committee Dr. D. Frailey, Dr. M. Chandy and Dr. M. Molloy for their helpful remarks and advices.

I would also like to express my appreciation to the CS department Unix systems staff that made the completion of this research possible by keeping the Department computers working 24 hours a day 7 days a week.

I thank David K. Bradley for his assistance in programming the assembler and running the early Motorola 68000 tests on the SUN workstation, and P. Horne and Dr. R. Jenevein for running the 68000 tests on the Valid Logic workstation.

Finally, I owe thanks to the National Science Foundation that supported this research by their Grant (MCS-8122039).

The task of formatting this dissertation was greatly eased by use of automated document processing. The Scribe document formatter was conceived of and created by Brian Reid. The current version has been maintained and enhanced by Unilogic, Ltd. The Scribe format definitions for proper dissertation format for The University of Texas at Austin were developed by Richard Cohen.

Gad Josef Dafni

The University of Texas at Austin December, 1986

#### ABSTRACT

Object oriented programming is an approach to reducing software cost by increasing programming productivity, program reliability, integrity and maintainability. This is achieved by bridging the semantic gap between the problem and the hardware concept spaces, that exists in conventional Von Neumann architectures. Achieving this goal involves a significant overhead, which made earlier object based systems inefficient and unable to compete with conventional systems.

This dissertation presents the functional design of an object based machine architecture, which is an efficient and reliable computing element for object oriented programming. Our design avoids the overhead by applying the following principles:

- Early binding of logical entities to their physical properties. This takes place at compile time, link time and at different points at run time.

- Decoupled access/execute processor. The access processor resolves arguments' names, taking advantage of predetermined access modes, while the instructions are executed in parallel by the execute processor.

- Taking advantage of program locality properties. Within the execution locality of a program, the overhead is reduced to a minimum.

Employing these principles involved an analysis of what binding may be done at each step of processing a program, as well as the analysis of the roles of each system component and the exploration of the locality properties of execution domains.

Performance evaluation of the design is done by use of a simulator

that runs on a host machine and emulates the designed system, including its real time. Several benchmark programs were run on this simulator and their runtime was compared to the runtime of the same programs run on other machines. The results show a significant advantage to the proposed design. Combined with the semantic advantages, we believe this system is superior to existing systems.

#### TABLE OF CONTENTS

| Acknowledgements                               | iv     |

|------------------------------------------------|--------|

| Abstract                                       | v      |

| Table of Contents                              | vii    |

| Chapter 1. Introduction                        | possek |

| 1.1. Design Goals                              | 2      |

| 1.2. Conceptual Basis for the Design of TOBS   | 3      |

| 1.3. Review of Past Object Oriented and Object |        |

| Based Systems                                  | 6      |

| 1.3.1. Addressing                              | 7      |

| 1.3.2. Protection                              | 10     |

| 1.3.2.1. The Access-Matrix                     | 11     |

| 1.3.2.2. Access-Lists                          | 12     |

| 1.3.2.3. Capabilities                          | 12     |

| 1.3.2.4. Procedure Call/Return                 | 15     |

| 1.3.2.5. Extended Types                        | 16     |

| 1.3.3. Concurrency Control                     | 17     |

| 1.3.3.1. Test and Set                          | 18     |

| 1.3.3.2. Exchange                              | 18     |

| 1.3.3.3. Decrement and Skip On Zero            | 18     |

| 1.3.3.4. Replace-Add                           | 19     |

| 1.3.3.5. The HEP System                        | 19     |

| PART I: DESIGN                                 |        |

|                                                | 20     |

| Chapter 2. System's Structure               | 21 |

|---------------------------------------------|----|

| 2.1. System's Block Diagram                 | 21 |

| 2.2. Fast Memories                          | 23 |

| 2.3. Queues                                 | 24 |

| 2.4. The AGV Registers                      | 24 |

| 2.5. Deadlock Recovery                      | 26 |

| Chapter 3. Model of Computation             | 27 |

|                                             | 27 |

| 3.1. Objects                                | 27 |

| 3.1.1. Local Objects                        | 29 |

| 3.1.3. Segments                             | 29 |

| 3.1.4. Object Cluster                       | 30 |

| · ·                                         | 31 |

| 3.1.5. Object Structure                     | 32 |

| 3.1.6. Segmented Objects                    | 33 |

| 3.1.7. Distributed Objects                  | 33 |

| 3.2.1. Pointers                             | 33 |

| 3.2.1. The Addressing Mode                  | 35 |

| 3.2.1.2. The Addressing Mode                | 37 |

| 3.2.2. O-pointers                           | 38 |

| 3.2.3. P-pointers                           | 39 |

| 3.3. Protected Domain                       | 39 |

| 3.3.1. Physical Structure                   | 40 |

| 3.3.2. Execution Environment                | 40 |

| 3.3.3. Internal Registers                   | 42 |

| 3.4. Procedure                              | 42 |

| 3.4.1. Call                                 | 42 |

| 3.4.2. Entry                                | 44 |

| 3.4.3. Parameters Accessing                 | 46 |

| 3.4.4. return                               | 46 |

| 3.5. Type Manager                           | 47 |

| 3.5.1. The Access Rights Table              | 47 |

| 3.5.2. The Concurrency Keys and Masks Table | 47 |

| UOUGHO LIL VILLALI VILLY LEVY LILA LILANIE  |    |

| 3.6. Process                               | 48         |

|--------------------------------------------|------------|

| 3.6.1. The Process Environment Table (PET) | 48         |

| 3.6.2. The Process Stack                   | 49         |

| 3.6.3. The Main Module                     | 50         |

| 3.6.4. The Process' Data Segment           | 50         |

| 3.6.5. Process Creation                    | 50         |

| 3.6.6. Context Switching                   | 51         |

| 3.6.7. Interprocess Communication          | 52         |

| 3.6.7.1. Asynchronous Procedures           | 54         |

| 3.6.7.2. System Communication              | 55         |

| 3.7. Job                                   | 56         |

| 3.8. Principal                             | 56         |

| 3.9. Data Types                            | 57         |

| 3.9.1. The Primitive Data Types            | 57         |

| 3.10. Access Modes                         | 60         |

| 3.10.1. Arrays                             | 61         |

| 3.10.2. Records                            | 61         |

| 3.10.3. External                           | 62         |

| 3.11. Instructions                         | 62         |

| 3.11.1. Operands                           | 62         |

| 3.11.2. The Instruction Execution          | 63         |

| 3.11.3. The Instruction Set                | 64         |

| 3.11.3.1. E-Processor Instructions         | 64         |

| 3.11.3.2. A-Processor Instructions         | 66         |

| 3.11.3.3. Control                          | 69         |

| 3.11.3.4. Type Conversion                  | 71         |

| 3.11.3.5. Communication                    | 72         |

| 3.11.3.6. System Instructions              | 72         |

| 3.11.3.7. Selector Operators               | 73         |

| 3.11.3.8. Input Output                     | 74         |

| Chapter 4. Naming and Addressing           | 75         |

| 4.1. Naming                                | 75         |

| 4.1. Naming                                | 76         |

|                                            | 76         |

| 4.1.2. Capabilities                        | <i>5</i> % |

| 4.1.3. Pointers and Nicknames             | 78           |

|-------------------------------------------|--------------|

| 4.1.3.1. The Nickname Table (NNT)         | 78           |

| 4.1.3.2. NNT Components                   | 81           |

| 4.2. Definitions and Structures           | 83           |

| 4.2.1. Definitions                        | 83           |

| 4.2.2. The Global Object Table            | 84           |

| 4.2.2.1. Locality                         | 84           |

| 4.2.2.2. Extendibility                    | 85           |

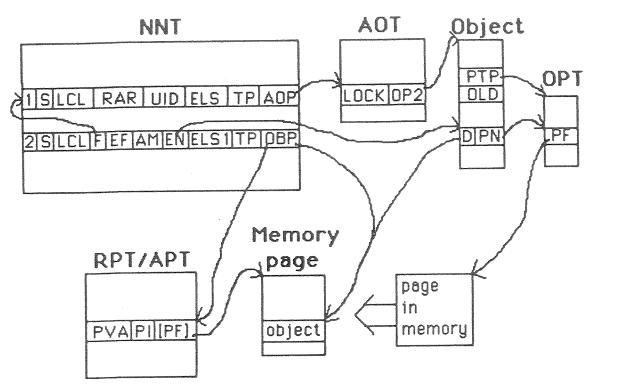

| 4.2.3. The Active Object Table (AOT)      | 86           |

| 4.2.4. The Resident Page Table (RPT)      | 87           |

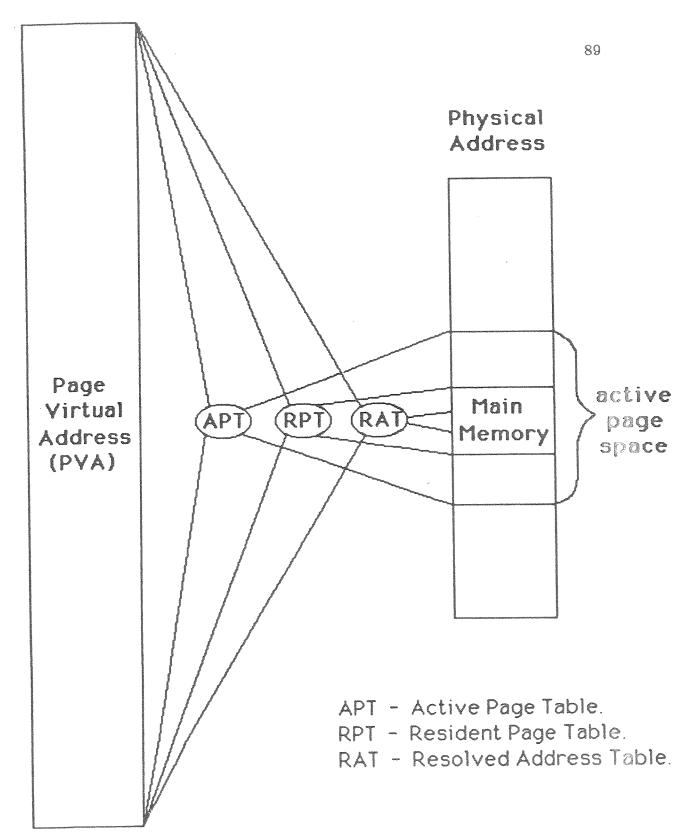

| 4.2.5. The Active Page Table (APT)        | 88           |

| 4.2.6. The Resolved Addresses Table (RAT) | 88           |

| 4.3. Addressing                           | 88           |

| 4.3.1. Addressing Modes                   | 90           |

| 4.3.2. Address Resolution                 | 90           |

| 4.3.2.1. Token's Physical Address         | 91           |

| 4.3.2.2. Object's Physical Address        | 91           |

| 4.3.2.3. Pointer Resolution               | 91           |

| 4.3.2.4. Capability Resolution            | 95           |

| 4.3.2.5. Symbolic Name Resolution         | 99           |

| 4.3.3. Remote Site Accessing              | 100          |

| 4.4. Virtual Memory                       | 101          |

| 4.4.1. The paging System                  | 102          |

| Chapter 5. Protection                     | 105          |

| 5.1. Definitions                          | 105          |

| 5.1. Definitions                          | 106          |

| 5.2.1. Intra Process Protection           | 107          |

| 5.2.1. Intra Process Protection           | 109          |

|                                           | 109          |

| 5.3. The Protection Mechanism             | 110          |

| 5.3.1. Capabilities                       | 111          |

| 5.3.1.1. Access Rights Resolution         | 111          |

| 5.3.2. Finding RSAR                       | 112          |

| 5.3.3.1. Verification                     | 112          |

| 5.3.3.2. Finding MRAR and MRC             | 112          |

| 5.5.3.Z. Finding Winan and Wino           | الله علم علم |

| 5.3.4. Process Creation Time             | 113 |

|------------------------------------------|-----|

| 5.3.4.1. Finding The Process' PAR        | 113 |

| 5.3.4.2. Verification                    | 114 |

| 5.3.5. Procedure Activation Time         | 114 |

| 5.3.5.1. Finding The Procedure's PAR     | 114 |

| 5.3.5.2. Verification                    | 114 |

| 5.3.6. Access Time Verification          | 114 |

| 5.4. Flexibility                         | 115 |

| 5.4.1. Access Rights Granting            | 115 |

| 5.4.2. Access Rights Revocation          | 116 |

| 5.4.3. Access Rights Amplification       | 117 |

| 5.5. Integrity                           | 117 |

| 5.6. Efficiency                          | 118 |

| Chapter 6. Concurrency Control           | 120 |

| 6.1. Discussion                          | 120 |

| 6.1.1. Concurrency Detection             | 122 |

| 6.1.1.1. Early Detection                 | 122 |

| 6.1.1.2. Late Detection                  | 123 |

| 6.1.2. Concurrency Elimination           | 123 |

| 6.1.2.1. Static Concurrency Elimination  | 123 |

| 6.1.2.2. Dynamic Concurrency Elimination | 124 |

| 6.2. TOBS's Concurrency Control          | 125 |

| 6.2.1. Overhead                          | 125 |

| 6.2.2. The Mechanism                     | 125 |

| 6.3. Examples                            | 129 |

| 6.3.1. Semaphores                        | 129 |

| 6.3.2. Readers-Writers                   | 130 |

| 6 2 2 Multiple Lock Evennle              | 130 |

| Chapter 7. Parameterization of the Architecture | 132 |

|-------------------------------------------------|-----|

| 7.1. Memory Parameters                          | 132 |

| 7.2. capabilities                               | 132 |

| 7.3. Pointers                                   | 133 |

| 7.4. O-pointer                                  | 133 |

| 7.5. P-pointer                                  | 133 |

| 7.6. Addressing Tables                          | 133 |

| 7.7. Fields                                     | 137 |

| 7.8. Object Size                                | 138 |

| 7.9. Fast Memories                              | 139 |

| 7.10. Internal Registers                        | 139 |

| 7.11. Opcodes                                   | 139 |

| 7.11.1. E-processor Short Opcodes               | 140 |

| 7.11.2. E-processor Long Opcodes                | 140 |

| 7.11.3. A-processor Opcodes                     | 141 |

| PART II: EVALUATION                             |     |

|                                                 | 144 |

| Chapter 8. Analysis                             | 145 |

| Chapter 9. Simulation                           | 147 |

| 9.1. The Assembler                              | 147 |

| 9.1.1. The Assembly Language                    | 148 |

| 9.1.1.1. The Input Line                         | 148 |

| 9.1.1.2. Pseudo Instructions                    | 148 |

| 9.1.1.3. Assembler Directives                   | 153 |

| 9.1.1.4. Constants                              | 153 |

| 9.1.1.5. Addressing Modes                       | 154 |

| 9.1.2. The Assembler Output                     | 154 |

| 9.1.2.1. Auxiliary memory                       | 155 |

| 9.1.2.2. Context table                          | 156 |

| 9.1.2.3. Profile Table                          | 156 |

| 9.1.2.4. Characteristics Table                  | 156 |

| 9.         | 1.2.5. Principals Table         | 157 |

|------------|---------------------------------|-----|

| 9.2. Tl    | he Simulator                    | 157 |

| 9.2.1      | 1. Time Simulation              | 158 |

| 9.2.2      | 2. Validation of The Simulation | 159 |

| 9.3. Te    | esting                          | 161 |

| 9.3.1      | 1. Linear Search                | 161 |

| 9.3.2      | 2. Recursive Quick Sort         | 162 |

| 9.3.3      | 3. Dot Product                  | 162 |

| 9.3.4      | 4. Matrix Product               | 170 |

| 9.3.5      | 5. Evaluation                   | 179 |

|            |                                 |     |

| Chapter 10 | O. Conclusions                  | 181 |

|            |                                 |     |

### LIST OF TABLES

| Table 9-1: | Simulator output for the Linear Search | 160 |

|------------|----------------------------------------|-----|

| Table 9-2: | Linear Search Test Results             | 165 |

| Table 9-3: | Quick Sort Test Results                | 169 |

| Table 9-4: | Dot Product Test Results               | 173 |

| Table 9-5: | Matrix product test results            | 178 |

| Table 9-6: | Matrix Product Test Results            | 179 |

### LIST OF FIGURES

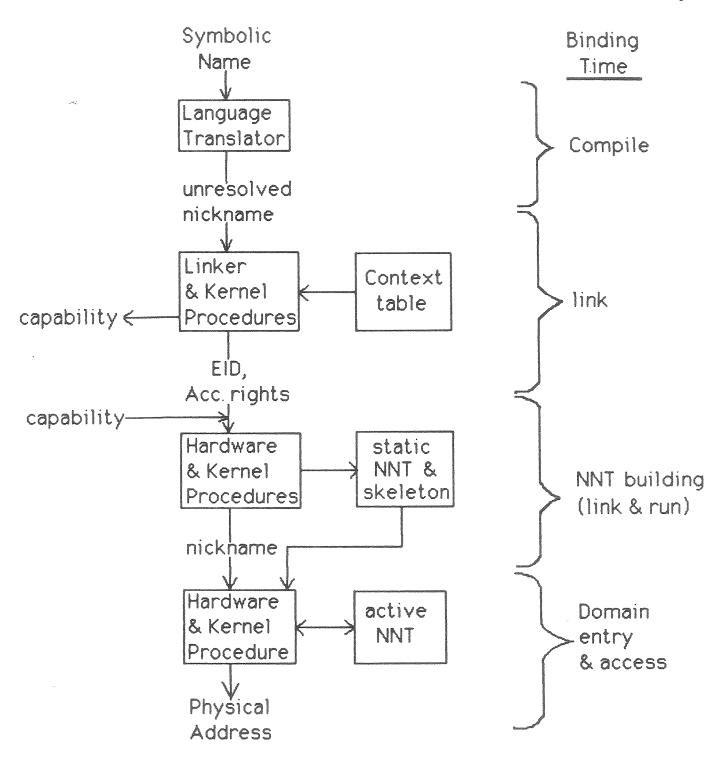

| Figure 1-1: | Name Binding                          | 5   |

|-------------|---------------------------------------|-----|

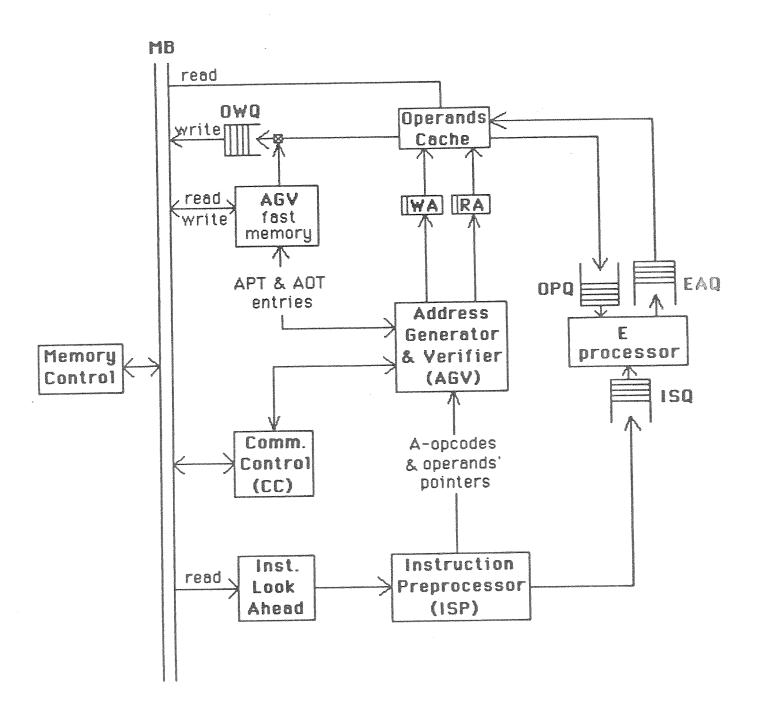

| Figure 2-1: | System's Block Diagram                | 22  |

| Figure 3-1: | Pointer                               | 34  |

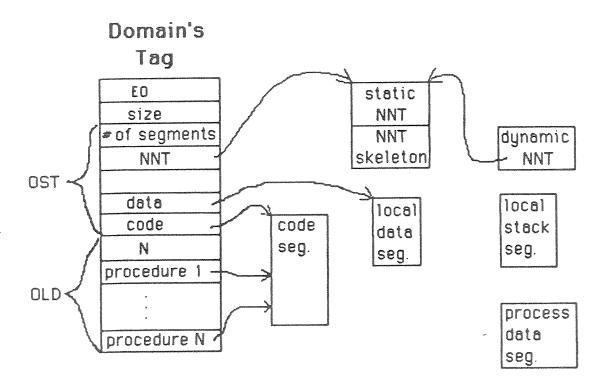

| Figure 3-2: | Protected Domain                      | 41  |

| Figure 3-3: | Local stack after call                | 45  |

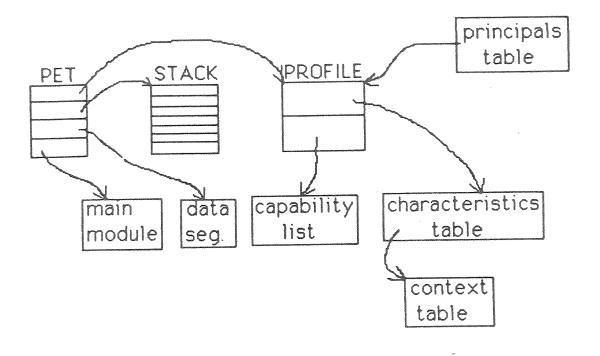

| Figure 3-4: | Process Structure                     | 49  |

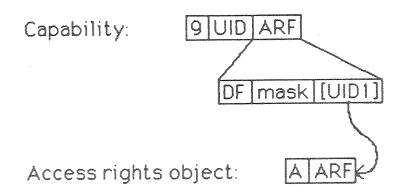

| Figure 4-1: | Capability                            | 77  |

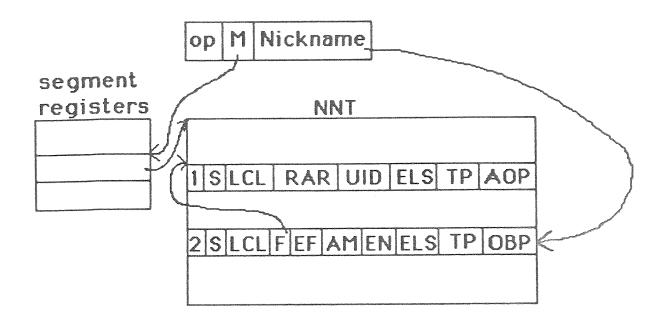

| Figure 4-2: | Addressing by Nickname                | 82  |

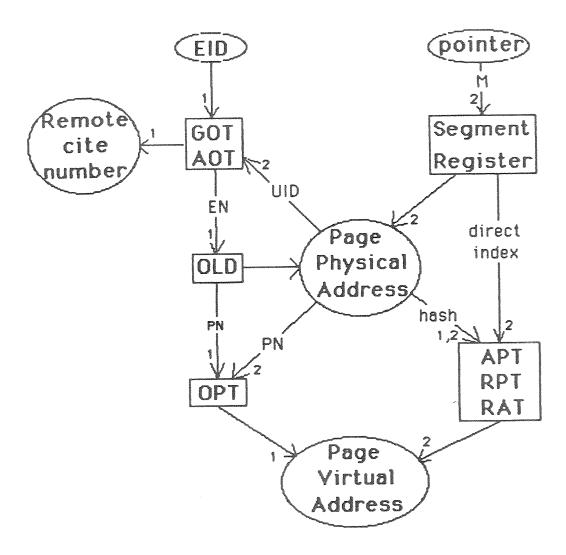

| Figure 4-3: | Page Address Mapping                  | 89  |

| Figure 4-4: | Run Time Object Nickname Resolution   | 96  |

| Figure 4-5: | Page Address Resolution               | 97  |

| Figure 9-1: | The Linear Search Program             | 163 |

| Figure 9-2: | The Quick Sort Program                | 166 |

| Figure 9-3: | The Dot Product Program               | 171 |

| Figure 9-4: | Version 1 Matrix Product Program with | 174 |

|             | remote procedure call                 |     |

| Figure 9-5: | Version 2 Matrix Product Program with | 176 |

|             | local procedure call                  |     |

#### Chapter 1

#### Introduction

An Object-Based System is a computer system where objects are the addressable entities, instead of bits, bytes, words or disc sectors, which are the addressable entities in a conventional computer system. We choose the phrase "object-based" to distinguish this system from object-oriented systems, where some hardware support is given to software implemented object accessing. Objects may be defined as instances of scalar or structured types (variables, structures, abstract types), or the abstraction of an instance of a resource. In general, objects are those entities which are of interest to the user, and which are used in the formulation of a problem. These are rarely bytes or sectors, which are typically the entities defined in hardware machines.

There is a vast conceptual span (sometimes called the semantic gap) between the objects definable in current day programming languages and the entities in which these objects are implemented in most current day computer architectures as described above. A large fraction of the instructions executed in current day computer architectures are interpretive realizations of user defined objects. Programming languages are further evolving towards defining objects at a higher levels of abstraction. There are increasing degrees of sharing in concurrent access to user defined objects. The software

implementation of objects and sharing of objects has been largely inefficient and ineffective. There is thus a current and increasing need for computer architectures which efficiently and effectively support direct definition and manipulation of objects. This dissertation reports research on design and evaluation of the Texas Object Based Architecture System (TOBS), which directly, efficiently and effectively implement objects and sharing of objects.

#### 1.1 Design Goals

The critical top level design goals are efficient and context controlled resolution of names to structured objects and the values associated with these structures. This high level design goal can be resolved to the following subgoals which are the basis for design of mechanisms:

- 1. Multilevel software-hardware scheme for binding names, access rights and concurrency control schemes.

- 2. Object accesses via logical and symbolic names for both primitive and abstract type objects.

- 3. Flexible but rigorous protection, including the encapsulation of object representation.

- 4. Provision for concurrency control and sharing.

- 5. Support for object naming, accessing, and concurrency control in distributed execution environment.

- 6. Competitive performance for this high level abstract hardware machine.

#### 1.2 Conceptual Basis for the Design of TOBS

The design is based upon a coherent synthesis of three principle concepts:

- Incorporation into the total system architecture of multiple levels of binding from names to values.

- Use of a decoupled access/execute architecture.

- Provision of hardware support for exploitation of locality in object accessing.

The subsequent paragraphs sketch each of these design concepts.

Names can be bound to addresses and thus to structures and values at several times in the programming and execution of a computation. Efficiency of access to values usually increases as the binding is brought forward to early phases of the programming or execution process. Binding at the time of actual access in execution involves repetitive interpretation and is thus usually the least efficient but the most flexible of modes of access and control of sharing of data. The essential element of this architecture is identification of the cases where binding can be done early and pushing outward these cases for binding as early as possible. The occasions for binding of structures and values to names include:

- Compilations of the program representing the computation.

- Linking of the compiled program to its execution environment.

- Initialization of the computation.

- At the creation boundaries for different execution domains within the computation.

• As the objects are actually brought from memory to the processor for execution.

These opportunities for binding are displayed in Figure 1-1.

The TOBS architecture has made a series of design decisions which press the binding toward the earlier levels and towards the most efficient possible access at execution times by means of effective exploration of locality. These trade-offs inevitably impact certain other aspects of computational structures. These effects will be discussed fully in later sections.

A computation as it executes, typically passes through phases in which its access is confined to a locality or subset of the total set of objects in This locality property has been explored at the the computation domain. physical level by the virtual memory concept. The smaller the execution domain, the higher the reliability of the computation. The larger the domain, the more readily early binding can be accomplished. The TOBS architecture explores locality in objects accessing by defining domains of moderate dimension, binding as much as possible at the time of domain creation and by creation of efficient mechanisms for addressing within a domain. Accessing within a domain is direct for local objects. Accessing of global objects within a domain is through a nickname table who's entries are resolved as early as possible, either at the domain creation time or at the time of first reference to the object. Thus when possible, repetition of the interpretive binding is avoided. The cost of this efficient binding is the restriction of sharing effectively to procedure or domain boundaries, although "release" mechanisms are also provided (that is, deletion of entries for nickname table).

Figure 1-1: Name Binding

Most modern architectures do implement some pipeline of instruction execution which implements look ahead of the fetching of operands for instructions. Concepts of decoupling of access processing from execution processing have been developed by Davidson and his students [Pleszkum 83] and by Smith [Smith 82]. This concept has been carried further in this architecture to include a much more extensive set of functionalities, including implementation of sharing and concurrency control mechanisms. This synthesis of concepts has given architecture which is shown by simulation to effectively implement Object Based Access. Each of the concepts is defined and discussed in more detail later in this dissertation.

## 1.3 Review of Past Object Oriented and Object Based Systems

Many of the general ideas mentioned above have been known for more than a decade. They were implemented in several object-oriented systems [Fabry 68], [England 74], [Wulf 81], [Jones 79], [Myers 80], and lately in object-based systems [Houdek 81], [Hemenway 81]. They did not gain much success, mainly because they failed to provide a satisfactory solution to the problem of the large overhead that is involved with trying to close the semantic gap mentioned before. As a result, some of them were very inefficient, while others did not carry the object-access principle all the way, by letting the user direct access to the internal representation of objects, in order to enhance performance (see [Jones 79], [Jones 80]). Yet, some of the basic ideas and techniques that were implemented in the past by software may be implemented in hardware in today's technology.

In this section we will look at some of the main problems, and how they were solved in the above systems.

#### 1.3.1 Addressing

The addressing function is the mapping of a logical-name space onto a physical-address space. It is simple when there is a direct mapping between the logical name and the physical address, but this leads to more serious problems (see [Fabry 74]). The simplest case is when the physical address is the object's name, as it was in the Chicago Magic Number Machine [Fabry 68]. This makes access to resident and nonresident objects faster than in other schemes, but we pay for it when an object has to be moved, where a search should be conducted for all the places where its address is used. To avoid this, a level of indirection through a System Capability Table (SCT) was used in the Plessey-250 system [England 74]. The same role is played by GST in Hydra [Wulf 74], [Wulf 81], and by the Global Object Table (GOT, as we shall call it further) in [Lanciaux 78] and [Browne 82].

In order to reference an object, we have to reference its GOT entry. One way to do that is to use the GOT entry's index. This has the disadvantage of a fixed GOT structure, which means that we cannot free GOT entries of objects that no longer exist. We cannot reuse them either, unless we find and destroy all the old references to these entries. That can be a real problem, since as was observed in the Hydra system, 98% of the objects had a very short life span (see [Almes 80] pp. 47), which may result in a GOT fifty times larger than it really has to be. Some other addressing schemes that did not use unique identifiers (UIDs) were investigated by Fabry [Fabry

74] and were found inadequate for addressing shared relocatable objects. Fabry's results are much more significant in distributed systems, therefore the importance of UIDs is much larger in such systems. Of course, the problem of mapping UIDs to GOT entries now arises, but this may be solved by a hardware implemented hash technique.

The number of objects in the system, and hence the GOT size, is usually very large compared with the size of the main memory. This necessitates a memory-management level, which is handled much as in conventional virtual storage systems. There are basically two approaches: single-level (flat) and multi-level schemes. (We refer here to the mechanism rather than the different levels of accessibility of objects, which in general are not the same).

In the single-level scheme, which was suggested in [Fabry 74] and was used in the IBM System-38, UIDs are mapped directly to physical addresses, by means of a page-directory table, which gives the UID and page number (i.e. the virtual page address) of each page resident in main memory. This table is usually found in fast memory and searched either associatively or by a hash procedure. A Non-resident object reference will cause an exception which will bring in the missing object, using the GOT. The single level scheme has the advantage of being simple, straightforward and relatively fast. Yet it has its drawback, which is the size of the address field in the instruction, that must be big enough to contain a UID, and probably a whole capability (that is access rights too).

To avoid large address fields, another level of indirection is introduced, taking advantage of the locality properties of a program. A Local Name Table (LNT) is used in Hydra [Wulf 74], and Nickname Table (NNT) is suggested by Browne and Smith [Browne 82], which contains capabilities (and selectors in Browne & Smith) for all the objects used by a program module. Since the number of objects used by each program module is much smaller than the number of objects in the system, the nickname-table is relatively short and so is the address field of the instruction, which contains an index into the nickname-table (8 bits may be sufficient in many cases).

Some systems, like the ZEUS system [Browne 84], [Browne 85], provide means for dynamic binding of symbolic names. This is added on top of the addressing schemes already described. The symbolic name is translated to a capability by a kernel call. Later the capability or a corresponding nickname-table index may be used. This process is similar to the one used in many file systems, where the symbolic name of the file is translated to a physical address (of a file-table) when the file is opened. This address is usually stored in a variable that is later used to perform file operations on the file. Names are related to a context-table (a directory in our example), and may become globally unique if we specify the path to the name (as it is done in Unix file system). A default context-table for each user is also suggested.

The above addressing scheme, including GOT, nickname-table and symbolic-names, will cost one search in a page-directory-table plus two simple indirection levels (name-index and index-capability) per resident object, after

the symbolic name has been translated. There are ways to make this cost as little as possible, and we will suggest such a way later.

There are still several problems related to addressing, besides the main mapping scheme. These are:

- The *small object* problem, that is successfully dealt with by the use of *selectors* in Browne & Smith [Browne 82], which we adopt.

- The generation of names, which is a problem in distributed systems, and is dealt with in [Browne 85] and [Dafni 85].

- The revocation problem, which is dealt with in [Redell 74] and by us.

- The garbage-collection problem.

#### 1.3.2 Protection

Since objects are the addressable entities, they are also the basic protectable units. It is very natural that the same mechanism that deals with addressing will also deal with protection (as it is with many other addressing mechanisms).

Protection should be rigorous but flexible, so that the principle of minimum privilege may be applied at a low cost. This means that we can change access rights easily, in order to grant each subject the minimum privileges it needs at any time, in order to minimize its ability to do harm.

#### 1.3.2.1. The Access-Matrix

The access-matrix [Graham 72] gives the access rights of all the subjects (users) that may have such rights, to all the objects in the system. Each column contains the access rights of all the users to a single object, and each row contains the access rights of a single user to all the objects. The access rights may include the right to pass certain access rights to some other users.

Manipulating the access-matrix is done by kernel procedures that have the privilege to access it. Each access to an object is verified by the kernel. Knowing the user and the object, the access-matrix is searched, the corresponding access rights entry is fetched and the requested access mode is verified.

The access-matrix method is the most centralized method. It gives the kernel full control of all accesses, thus making it easy to change rights that were granted. The problem with this method is the overhead. First, the access-matrix itself requires a lot of space, since it contains many blank entries (meaning no access rights). Second, the size of the matrix makes the search a time consuming task each time some object is accessed. Third, each manipulation of access rights must be done through the kernel. Fourth, the centralized nature of this method makes it most inadequate for use in distributed systems.

#### 1.3.2.2. Access-Lists

Access-lists are actually the columns of the access-matrix. That is, each object has a list of all the users that have access rights to it. It does not take a special search to find the object's access list, since it may be put in a directory together with the address of the object, that must be found in any case. That makes the search for the access rights simpler than in the case of the access matrix. The access list is smaller than the access-matrix column, because it does not contain empty spaces (for users that have no access to the object). That makes the search even faster.

Access-lists may be distributed according to the distribution of the corresponding objects and their types, which is applicable to distributed systems, and makes the search hierarchical, thus faster.

Maintenance of the access-lists, which means granting and revoking access rights, is done through kernel routines, which is time consuming.

Access lists have an advantage with regard to garbage collection, since it is easy to detect garbage as an object whose access list is empty.

#### 1.3.2.3. Capabilities

The rows of the access-matrix may be viewed as a list of capabilities of a user (subject) to access objects. What is usually meant by *capability* is such an access-matrix entry, which contains the access rights to an object, combined with the object's ID. The user has to present such a capability to a hardware or kernel handler in order to perform an operation on the object.

The handler will translate the ID to the object's physical address and will verify the access rights. In some cases, capabilities will also contain the object's type, which makes it easier to route the handling of the capability to type-managers, where translation, verification and other activity may be done more easily (see [Browne 83]).

To make usage of capabilities flexible, it is desirable to permit moving them around within one's address-space, or transferring them to other processes. This introduces several problems:

- Integrity of capabilities, which means prevention of forgery of capabilities. This must be supported at least by some level of hardware support, that recognizes capabilities as special entities.

- Revocation of capabilities, once granted by a process to another.

- Restriction of access rights of capabilities transferred to another process.

- Amplification of access rights by a process that gets a capability from another one.

The integrity problem has been solved by two methods. One is the protection of certain areas in the virtual address space, that contain capabilities. That means that a user cannot perform unauthorized operations on these areas, and therefore cannot forge capabilities. One can, though, copy capabilities from one such area to another, provided he has access to them. This, together with some other legal operations, provides the flexibility. This method comes in several variants, such as partitioning, fencing and others. (see [Fabry 68], [Wulf 74], [Hemenway 81], [Jones 79]).

The second method is the protection of certain entities according to their contents, which is called tagged architecture. That means that we add some extra bits to each entity, that tell its type, as was suggested in [Feustel 73], [Myers 80], [Gehringer 79] and [Browne 82]. The hardware will not allow performing an operation on the wrong type (as some compilers do). In its primitive form, only two basic types are implemented by hardware capabilities and data, as was used in the IBM System-38 [Houdek 81]. The tagged method has more flexibility than the protected memory method (see [Fabry 74]), and it allows hardware type-enforcement.

Revocation of access rights is relatively simple when using access-lists. It is harder when dealing with capabilities (see [Fabry 68], [Ekanadham 79]). One common solution is to use indirection, as was suggested in [Fabry 68]. The donor makes a copy of the capability in its address-space, and gives the user a capability to that copy. To revoke the capability, the owner must destroy the copy and never use its address again. Therefore it is suggested that the address of the copy will be a pure logical address, such as a UID. Otherwise we may be losing some more valuable resource. It is desirable that the user of such a capability need not be aware of the fact that it is an indirect capability, which means that it should contain an indirect-reference bit, interpreted by the hardware (or kernel). Another solution may be the use of keys, as was suggested in [Ekanadham 79]. This method has a considerable amount of flexibility, yet it requires variable-length capabilities that can accommodate any number of keys, and more interaction with the kernel, for establishing and revoking locks. Later we will present our own solution.

Amplification of access rights is needed when the principle of encapsulation is applied by a procedure (usually in a type-manager or resource-manager) to its parameter. In that case, the procedure has access to the internal representation of an object, which the caller, that supplied it as a parameter, does not have. The privilege to amplify certain capabilities is restricted to special cases, like those mentioned above. This implies that we do not deal with an hierarchy of authority.

Garbage collection may become a problem when capabilities are used. Reference counts may be used, but they must be protected against crashes (see [Almes 80] pp. 26) and must be accompanied with a garbage collector.

#### 1.3.2.4. Procedure Call/Return

A procedure's execution domain is comprised of three kinds of objects: global, local and parameters. Local objects may be dynamic or static. Static objects will include static variables and constants.

A procedure call is a change of domain. A return from a procedure is change back to the previous domain. These domains may be disjoint or not, depending upon the protection policies and the relations between the procedure and the caller. As we have already mentioned, hierarchy of authorization does not apply in general. The LIFO nature of procedure calls within a single process implies use of some kind of stack. Yet, the conventional linear stack, where activation-records are allocated as stackframes, is inconsistent with the idea of objects being the basic units of protection, unless the activation records are separate independent objects.

One should also consider the necessity of revoking access rights to such activation-records, once the procedure's execution terminates. It is possible to put a capability for the caller NNT in the NNT of the procedure when it is called, to be used for returning, as suggested in [Browne 82]. Yet it should be a special kind of capability, that may be used only by the *return* instruction. We will not adopt that solution because we like our protection scheme to be connected to the object rather than to specific instructions.

The solution used in the Hydra system seems conceptually appealing. The activation-record is formed as a new LNT (Local Name Table) and its capability is pushed onto the process-stack. That stack is accessible only to the call and return instructions, therefore protected against unauthorized use. The problem with the Hydra solution is that it is so costly in processing time that each procedure call is considered a major design decision. This is so partly because of the general inefficiency of Hydra, due to lack of hardware support. But the main reason is the overhead of building the LNT each time a procedure is called. In our design we propose a method that uses the same conceptual frame as the Hydra method, but in a more efficient mechanism. Using hardware implementation will reduce the overhead to a minimum.

#### 1.3.2.5. Extended Types

An extended type is an implementation of an abstract type, that extends the set of basic types of the machine. An abstract type is a set of objects, and a set of operations that are allowed on them. It is usually implemented by choosing some convenient representation for the type's objects, and writing a package of functions that implement the operations.

This package is called a type manager. Assuming the type manager is safe, then as long as the objects of the type are manipulated only through the type manager (not including copying them), consistency and integrity may be maintained in regard to that type. To ensure this, anyone but the type-manager is denied access to the objects' representation. This property of such packages is called encapsulation, which means for data very much the same as atomicity means for control.

Object-based systems are most suitable for implementing the encapsulation property, by adding to the list of access rights a right to seal or unseal an object, which controls the ability to access the internal representation. In [Browne 82] we have instead the right to create component-selectors, which is more powerful than the unseal right, since it may be applied hierarchically, to different levels of representations.

#### 1.3.3 Concurrency Control

Concurrency control is a way of applying atomicity to transactions on a specific data object. Critical section mutual exclusion is needed because of conflicting accesses to the same data, and the known solutions to this problem are based on controlling concurrent access to certain data objects. Such a control may be applied in some cases prior to execution (see [Taylor 83]), and in other cases it must be applied at run time.

Many systems provide primitives for run time concurrency control.

Hardware support for such primitives is essential, since they must be atomic actions. In the following we review briefly some of these primitives, which are

all atomic operations, such that other processes cannot access their operands at the same time. We present our concurrency control primitives in chapter 6.

#### 1.3.3.1. Test and Set

The test and set instruction provides a means for implementing binary semaphores. It tests its Boolean operand. If the operand is zero - it sets it and proceeds. Otherwise - the instruction branches to a specified location. This is a most primitive mechanism that is sufficient for concurrency control. Implementing higher level mechanisms using test and set introduces a lot of overhead. Yet, it is cheap and easy to implement in hardware.

#### 1.3.3.2. Exchange

The exchange instruction is another mean for implementing semaphores. It exchanges the contents of a local variable (or register) with that of a global variable. It has the advantage that the contents may have any value.

#### 1.3.3.3. Decrement and Skip On Zero

This instruction may be used to implement general semaphores, and it is useful for loop control as well. For that reason and because of its simplicity, it is found in many machines. Note that if the counter is required to reside in a processor-local register, the instruction is not useful for implementing semaphores. The fact that the decrement is not conditioned by the operand value causes some problems.

#### 1.3.3.4. Replace-Add

The replace-add mechanism suggested by Gottlieb, Lubachevsky and Rudolph in [Gottlieb1 83] and the fetch-and-add mechanism that was used by Gottlieb et al in the NYU Ultracomputer [Gottlieb 83] has several advantages over the test and set primitive. It is easy to implement in hardware by augmenting the memory controller with an adder, and may be executed concurrently by smart switches in an hierarchical interconnect network. Yet, it has the disadvantage of not testing its operand's value prior to adding, which complicates the implementation of some classic algorithms. On the other hand, the above papers show some interesting algorithms where the power of the replace-add instruction can be exploited for concurrent execution.

#### 1.3.3.5. The HEP System

In the former mechanisms we needed to assign a special object, Boolean or integer, for the special instructions to act upon. Furthermore, the use of these mechanisms was voluntary and anyone could get around them, erroneously or intentionally. In the HEP system [HEP 82] each memory word has its own flag which may be set to FULL or EMPTY. A store operation can be forced to wait until the word is empty before writing it and setting it full, and a read operation can be forced to wait until the word is full before reading it and setting it empty. This mechanism has the nice property that the flag is connected to the data itself, and that its setting, clearing and testing is done automatically and not voluntarily by the user.

### PART I: DESIGN

# Chapter 2

# System's Structure

The system is built of a decoupled access/execute processor, as in [Pleszkum 83] and [Smith 82]. Unlike what is suggested in [Giloi 83], the E-processor is the slave of the A-processor. The A-processor controls all accesses to memory and performs the functions of addressing, protection and concurrency control of objects. The E-processor executes the instructions whose opcodes and operand values are sent to it by the A-processor, and returns the results. Some of the instructions (control and organizational) are executed by the A-processor, sometimes with the help of the E-processor, when arithmetic is needed. Though most computations will be done by the E-processor, the A-processor has the ability to perform address calculations by itself.

# 2.1 System's Block Diagram

Figure 2-1 shows the block diagram of the system.

The main blocks of the A-processor are:

AGV

Address Generator and access Verifier. This unit does all the processing related to object accessing, as will be explained in the next chapters. It will send read-addresses to RAQ, write address to WAQ and will read and write into the addressing tables through the AGV cache.

Figure 2-1: System's Block Diagram

**ISP**

Instruction Preprocessor. It will get instructions from RC, separate them into instruction-code and operands selectors and access-methods, send the instruction-code to ISQ and the rest to AGV.

CC

Communication Control. An interface to the communication network. Controlled by AGV through the channel instructions, used by the channel hardware type manager. Has a DMA to memory, that allows data to go only to or from a port object (by reading its tag first).

MB

Memory Bus. Has address lines, data lines and control lines for controlling read/write etc. The memory control acts as an arbitrator to resolve conflicts.

#### 2.2 Fast Memories

Fast intermediate memories are used at several points in the access processor to accelerate execution. They are connected to the read and write controllers on one hand, and to the different units of the A-processor on the other hand. Their address spaces are disjoint, so there is no problem of updates from one cache to the other. Follows is their description.

The Address Generator (AGV) Cache

This cache is connected to the AGV and is used for accessing the process stack, APT and AOT for address calculation.

#### The Operands Cache

Is part of the operands path to/from main memory. Beside the cache it includes an internal control unit that matches a value from EAQ with the address in WA and send them to the cache, or gets a read address from RA, reads the data from the cache and sends it to OPQ. (see description of WA and RA in section 2.4).

The Instruction Look Ahead

Is part of the instruction path from main memory. Accepts addresses from ISP and sends data (i.e. parts of instructions) back. When necessary, it asks for more data from RC.

# 2.3 Queues

Following are the queues used in the A-processor between its internal blocks and between the A and E processors.

ISQ Instructions Queue for the instructions sent to the E-processor.

OPQ Operands Queue. Holds the operands values fetched from the operands cache (or memory) before they are processed by the E-processor.

EAQ E to A queue. Holds the results received from the E-processor before they are stored in the operands cache and main memory.

EABQ E to A boolean queue. Holds the results of boolean calculations in the E-processor, that are used for decision making in the A-processor.

OWQ Operands Write Queue. Contains write-through values and their addresses, from the operands cache.

# 2.4 The AGV Registers

The AGV has several internal registers for holding the program status variables. Each register contains three parts. The first part holds the virtual address of some object and the second the third parts hold the relative limits of some active part of the object (like an activation record of a stack). The registers are:

| LCR | Local code register. Points to the local code segment of the protected procedure. |

|-----|-----------------------------------------------------------------------------------|

| LS  | Local stack register. Points to the local stack.                                  |

| DFD | Default data segment.                                                             |

| SNR | Static NNT register. Points to the beginning of the static NNT.                   |

| DNR | Dynamic NNT register. Points to the beginning of the dynamic NNT.                 |

| LDR | Local data register. Points to the local data segment of the domain.              |

| PDR | Process' data register. Points to the process' data segment.                      |

| DTR | Domain's tag register. Contains an O-pointer to the current domain tag.           |

| PS  | Active process' stack.                                                            |

| PQU | Active process' system communication port.                                        |

Beside these registers, the A-processor has the following internal registers that are not related to the process status:

fetched. Size is not applicable.

PC

The program counter. Points to the next instruction to be

WA Write-Address register. Holds the next write address generated by the AGV, before it goes to the operands cache.

WA has a flag that tells whether it has valid contents or not. If not - the AGV cache control will not use it. Before loading WA, AGV looks at RA. If its contents is valid and is the same as the intended WA contents, AGV will wait until RA is emptied.

Note that a queue instead of a register is not beneficial assuming the cache speed is high relative to the AGV and E-processor (that is - assuming negligible cache cycle time). It may only contribute to the queuing space of the corresponding path, and that may be achieved by extending the EAQ. On the other hand, a queue must be searched for conflicts each time a read address is generated, and that is much harder to do compared to a register.

RA

Read-Address register. Holds the next operand's address generated by the AGV, before it goes to the operands cache. Like WA, RA has a valid flag. Before loading RA, AGV looks at WA. If its contents is valid and is the same as the intended RA contents, AGV will wait until WA is emptied.

See note in WA description.

Scratch Pad Scratch registers for temporary use.

# 2.5 Deadlock Recovery

The communication between the two processors presents the possibility of deadlocks. That may happen when both are waiting on each other while the relevant queues are empty. To detect and recover from such situations, the A-processor will employ a timeout mechanism that is activated after it waits for a time longer than the maximal processing time of any instruction, while the ISQ is not accessed by the E-processor. The timeout procedure will check the queues and send the necessary data to reset the E-processor. Then it will activate a processor error recovery procedure.

# Chapter 3

# Model of Computation

In the following we describe the model of computation for the TOBS system. We start with the general description of objects, then continue with the bigger execution units and the relations between them, and go down to the elementary data units and the instructions. Some of the more primitive concepts are used before they are defined. In such cases we make a reference to the definition. The reader is advised to look ahead when the definition of such concepts is required.

# 3.1 Objects

A TOBS's object is defined as in [Wulf 81], to be an instance of a type. An object may stand for an abstract concept, but it must have a physical representation in memory and a name. Objects are divided into different kinds according to where they physically reside and how their representations are structured.

# 3.1.1 Local Objects

Local objects are objects that are accessible only to a certain protected domain (see Section 3.3) and reside in its local addressing space, or to a certain process. Their names, which are context dependent, are shorter and their addressing is simpler. They are not accessible from outside the domain, which is linked at one time, therefore their access control is managed

by the compiler and linker and not by the run-time system. The only access that needs a special access right in order to be exercised on a local object at run time is the "unseal" right.

Local objects are not internal objects of the domain, but are special external objects (that may have internal objects of their own). The space they occupy is allocated by the system from a local segment, which is an internal object of the domain, or from the the process' segment of the executing process. The local segments include the local stack, the local data segment and the local code segment (where data may be embedded as literals). Local objects are created by the compiler and loader, or dynamically by the use of the CREATE instruction. If they reside in the local data segment, there is no control on which process may use them (which may be the intention). If they reside in the process' data segment, they may be used by any procedure called by that process, but not by other processes that use the same procedure. If they reside on the local stack, they can be used only by the current activation of the domain.

Local objects access control is handled by the compiler and linker. The programmer specifies the access rights to an object together with its declaration and the compiler and linker enforce them. This is possible since a protected domain is always linked to one module before it is run. Concurrency in accessing local objects may occur when different activations of the same domain try to access the same static object. Such concurrency is not handled by the system.

Local objects do not differ in their structure from other objects of the same type.

#### 3.1.2 Global Objects

Global objects (sometimes called remote objects) are objects that are accessible to anyone who has their name and the proper access rights for them. They reside in the public domain (that is in no specific protected domain), are named by their UID and accessed from inside a protected domain by their local nicknames (see Section 4.1.3). Note that a code segment can never be a global object by its own, but it is always internal to a protected domain.

### 3.1.3 Segments

A segment is an object which groups together objects that are local to a domain or a process. The segment is protected from unauthorized access, but once a procedure has access to a segment it is allowed to access the objects it contains in any way except for unsealing them. The addressing in such case is relatively simple, and is done by pointers that contain physical displacement.

Segment size may change dynamically in certain cases. In such cases, the segment size that appears in its tag is the maximum size it may have. Entries that appear in the segment's OPT but are not used, are marked as empty. Segment size is limited by the size of the pointers.

Segments may be of one of three types - data segments, code segments and NNT. The segments that are used as part of the execution

environment of a procedure are the local stack segment, the local data segment and the process' data segment which are of the data type, the local code segment which is of the code type, and the static NNT, dynamic NNT and dynamic NNT skeleton, which are of the NNT type.

Data segments are used as pools for allocating space for local objects. This is done both statically and dynamically. The segment contains for that purpose a bit map and a list of partly filled pages.

# 3.1.4 Object Cluster

An object cluster is a page that contains several small global objects, in order to make their paging more efficient. The objects contained in an object cluster may be of different types. Their connection to the cluster is loose and the system may move an element out of the cluster when it is convenient. The difference between a cluster and a segment is the amount of independence they provide to the objects they contain, and their sizes. Unlike in a segment, each object in a cluster has its own GOT entry and its own protection.

The user will not deal with clustering, since the cluster has nothing to do with the logical characteristics of the objects involved. Clustering will be done by the compiler, linker and the run time system, based on locality properties. The problem of when and how objects will be connected to a cluster is outside the scope of this research. We assume though that the compiler and the loader cluster static objects.

#### 3.1.5 Object Structure

Objects may be structured or not. A structured object is an object whose internal representation is defined by means of other object types.

A structured object has two parallel structures, the physical structure and the logical structure. By the physical structure we mean the way physical space is allocated for the object. By logical structure we mean the way the object is built from its logical components. Both structures are defined by the object's tag, that includes its type, its length, a pointer to its page table (OPT) and its logical description (OLD) that depends upon its type. Objects that are shorter than a page size will have null OPT pointer. Objects whose type implies that they are shorter than a single page, will not have an OPT pointer at all.

OPT is a system object that contain a list of the page frame addresses where the pages of the object reside. It defines a mapping of the object's page numbers to physical page frame addresses. OPT itself may occupy more than one page, in which case it will have its own OPT. An internal object's OPT may be the same as the OPT of the external object that includes it. An OPT entry includes the permanent page frame number (PPF) of a page in the encompassing segment, or the physical page frame if the object is global. If the page has a copy in main memory, the page pointed by PPF may not be updated. Yet, it may serve as a backup of the page on the auxiliary memory, which is usually more stable.

An object's OLD is an object of OLD type whose entries point to the elements of the object. An OLD entry format is:

PN Page number in the external object, where the element begins.

D Displacement in page to the beginning of the element.

Ptag The offset of the element's tag in the external object tag.

OLD is a one dimensional array of P-pointers. It is either included in the object's tag or has a category 2 O-pointer in there. It provides an efficient mean for finding the offset of the object's elements from its beginning.

# 3.1.6 Segmented Objects

A segmented object is an object that is divided into several independent segments (that have their own names). These segments may be dynamically allocated to the object, and may change size.

The tag of such object contains an OST - Object Segment Table, which contains O-pointers of the segments. The object size field in the tag refers to the size of the tag itself, which usually is contained in a single page. If the tag is too big, it is paged and the object has an OPT. The segments have their own OPTs, if necessary.

Beside the OST, the object tag may contain an OLD, but in this case its entries are of the form <S,PN,D>, where S is the segment number. The PVA of the pages is related to the segments to which they belong.

#### 3.1.7 Distributed Objects

The elements of a distributed object may reside at different sites. We will describe such an object as a collection of independent objects that have something in common. That something is the possibility of defining them as elements of the same object (besides the possibility of accessing each of them independently, by its own name). We implement a distributed object by giving each of its elements a UID and a GOT entry at the site where it resides, and creating an object's root which is of OBD type and contains a table of descriptors for all the elements, which have the same format as GOT entries. This object's root stands for the distributed object as a whole, and resides at one of the sites. The preceding structure may be nested to any depth.

# 3.2 Addresses

Object addresses are expressed in two ways - as pointers by the user, or as O-pointers for the system's use.

#### 3.2.1 Pointers

A pointer (or a local pointer) is an object of special type, that points to another object, or contains the other object. Pointers are used inside a protected domain (though the may point to remote objects). They can also be used as parameters for remote procedure calls. Pointers, unlike O-pointers, are seen by the programmer. The difference between pointers and capabilities is that they are context dependent. That means they depend upon specific NNT or local segments. Therefore they have no meaning outside this context. Some of them that refer to dynamic NNT entries that may have different meanings at different activations, should be reevaluated at each activation.

Besides its tag, a pointer contains an addressing mode M and an address A. The addressing mode M tells the address section where the address A is to be interpreted, and whether it is direct, indirect or immediate.

Pointers, like capabilities, may be manipulated only by the use of certain instructions.

See Figure 3-1 for pointer format.

# 8 C M A

# Where:

8 - is the pointer type code.

C - is the class: short, medium or long.

M - is the addressing mode.

A - is the offset.

Figure 3-1: Pointer

# 3.2.1.1. The Addressing Mode

In order to avoid complex addressing and validation when they are not needed, we divide the address space of a protected module into several sections, that are distinguished by an addressing mode that accompanies each operand in an instruction. The addressing mode also determines the pointer size and the use of indirection.

The pointer class is determined by its first one or two bits. 0 means short pointer, 10 means medium size pointer and 11 means long pointer. Besides the pointer length, the interpretation of the rest of the addressing mode bits also depends on the pointer's class.

Following the class bits are 3 bits that specify the addressing mode in the class, as follows:

# Short pointer:

- 0 local code segment.

- 1 immediate data(#).

Size depends on the data object.

- 2 local stack segment.

- 3 indirect through local stack (@).

- 4 data segment (own, static).

- 5 indirect through data segment (@).

- 6 direct nickname (EN of the selector).

- 7 nickname (static or dynamic according to the

# MSB of the A-field) (external)

# Medium size pointer:

- 0 local code segment.

- 1 immediate.

- 2 local stack segment.

- 3 indirect through local stack.

- 4 data segment.

- 5 indirect through data segment.

- 6 direct nickname.

- 7 nickname.

# Long pointer:

- 0 local code segment.

- 1 immediate.

- 2 local stack segment.

- 3 indirect through local stack.

- 4 data segment.

- 5 indirect through data segment.

- 6,7 null pointer (last bit immaterial).

#### Notes:

• The short data mode is always related to the default data segment.

In the medium and long data modes, the first two bits of the A-field are used for selecting the data segment, as follows:

Ox - default segment. The second bit x is part of the displacement.

- local data segment.

- process' data segment.

Indirection is applicable only when the pointed object is itself a pointer.

- Each of the address sections will have an internal register pointing to its beginning. The data segment may be local or process' global (see Section 3.1.3). The contents of these registers is part of the process status.

- The direct nickname mode deals with the EN field of the selector. This is regarded as integer and may be used with all the integer operators.

#### 3.2.1.2. The A-field

The A-field of a pointer is interpreted according to the addressing mode. It may be a physical offset in tokens from the beginning of the appropriate segment or NNT, or the object's representation itself in the case of immediate mode.

In general, the actual offset is the value of the A-field, except for the following cases:

- The A-field of a nickname is multiplied by the NNT entry size in tokens, to give the offset in tokens from the NNT beginning.

- For stack and data modes we define the lower part of the segments as a virtual "register" pad, and the actual offset OFFSET in tokens becomes:

A Lshift RS if  $A < 2^{**}RN$

OFFSET=

A Rclear RS if  $2^{**}RN \le A < 2^{**}(RN + RS)$

Where

"X Lshift N" shifts X N bits to the left

"X Rclear N" clears X's N right bits

2\*\*RS is the "register" size

2\*\*RN is the number of "registers"

and RN and RS are parameters of the architecture (see chapter 7).

This arrangement allows the effective use of short addresses for objects larger than a token, at the cost of some memory waste in certain cases. Use of a cache make these locations equivalent to general registers, to a certain extent.

# 3.2.2 O-pointers

An O-pointer is a system's object which is a pointer to an object. That means that it may be resolved to a certain degree to a physical address. Access to O-pointers is not granted directly to a user. O-pointers are created and used internally by certain instructions. O-pointers belong to one of the following categories:

- <0,EID>: An unresolved pointer.

- <1,PVA,d>: A resolved in-site pointer. PVA is the page virtual address (PVA see Section 4.2.1). d is displacement in page.

- <2,PVA,d,P>: A resolved in-site pointer. P is a pointer to APT or RPT entry (see Section 4.2.5, 4.2.4). d is displacement in page.

- <3,EID,site>: A resolved out-of-site pointer. Site is host hint found in the local GOT. It may be wrong but in most cases will lead to the right site.

An O-pointer is context independent. Unlike pointer or capability, it is internal to the system and the user cannot copy it or use it in instructions.

# 3.2.3 P-pointers

P-pointers are physical addresses. Like O-pointers they are not directly accessible to users but are used internally by the system. They have two forms:

- <0,PF,d>: Object's physical address.

- <1,PF>: Page physical address.

where PF is a page frame number and d is a displacement in the page.

# 3.3 Protected Domain

A protected domain is an object whose internal objects share the same address space and are protected against external interference. The address space of the domain is defined by its nickname table (NNT) (see Section 4.1.3.1) that contains references to all the objects that are outside the domain and are directly accessible from inside the domain. References to internal objects of the domain from outside the domain must be done by a procedure call using parameters, or through the interprocess communication mechanism (see Section 3.6.7), using a capability with the appropriate access rights. Local objects cannot be directly accessed from outside the domain.

An important property of a protected domain is that it is linked at one time. That means that local objects name resolution, access control and concurrency control may be done at compile and link time, using information supplied by the programmer through language constructs.

A protected domain usually contains several procedures and data

objects that are used to implement certain abstractions. Yet, the programmer may draw the lines of the protected module wherever he likes (as long as it contains whole objects), and for efficiency reasons may choose to combine several such abstraction into one domain.

The NNT has two active parts - static and dynamic. A third part, the dynamic NNT skeleton, is used for building the dynamic NNT at activation time. All the NNT parts are protected external objects (see Section 4.1.3.1).

#### 3.3.1 Physical Structure

Protected domain is a segmented object. Therefore its tag contains an OST that contains pointers to the dynamic NNT skeleton, the static NNT, the local data segment and the code segment. Its tag also contains an OLD that contains entries for its internal objects. These internal objects are the procedures that are accessible from outside the domain.

See Figure 3-2.

#### 3.3.2 Execution Environment

The address space of a protected domain is divided into six sections:

- A local code section.

- A local stack section.

- Two data sections.

- Two remote addressing sections, static and dynamic.

The local sections of the address space consist of names that are called local

Figure 3-2: Protected Domain

names and are comprised of a segment identifier and a physical offset. Objects addressed by local names are not protected. The remote addressing sections consist of names that are called *nicknames* and are comprised of the NNT identifier and an index into the static or dynamic NNT.

# 3.3.3 Internal Registers

The access processor has several internal register pairs for holding the program status variables, as described in section 2.4. At context switching, these registers together with some working registers that are used by the microprogram are stored on the process stack and the process stack pointer is stored in a system queue. At domain entry, the above registers are also stored on the process stack, then the same process executes some procedure of the domain, as is explained in the following section. Beside these registers, each of the processors has a set of internal scratch registers.

# 3.4 Procedure

A procedure is an object that is represented by a code segment and a data segment. It is always an internal object of some protected domain. There may be several procedures in a protected domain, some that are accessible from outside the domain and are regarded as its internal objects, and some are local.

#### 3.4.1 Call

A procedure call will have two operands, given by pointers. The first operand is a pointer to the called procedure and the second is a pointer to an actual parameter table (ACP).

The ACP contains a list of pairs <ARO,pointer>, where the pointer (see Section 3.2.1) points to the actual parameter, while ARO is an access rights object that contains the access rights that the caller wants to grant the procedure. The ARO of certain entries may be missing, which is interpreted

by the CALL instruction as a request to grant to the procedure the maximum access rights that the caller has to the parameter. If the ACP entries are static, the compiler builds it and take the parameter's access rights into account in the module's required access rights (see Section 5.1) of the caller. It also compares the parameter's possessed access rights to the caller's required access rights (see Section 5.1), which in the case of a local object are assumed to be unlimited, to make sure that ARO does not include more access rights that the caller has. The compiler or the linker also compare the ARO to the object's required access rights of the parameter in the called module and decide whether to abort execution immediately, temporarily disable access rights verification for that parameter or delay action for the actual access time. In many cases the access rights to the parameter can be verified when the caller is entered, but in some cases they need to be verified at the time of the call, or may be even at access time.

If the called procedure is addressed by a local addressing mode, it means a local procedure call. In that case no access rights checking and no address domain change will take place. The procedure will be executed with the NNT of the caller.

If the called procedure is addressed by a nickname, it means a remote procedure call. The NNT entry indexed by the nickname is a selector for a procedure in a protected domain which is pointed to by the selector's father. The selector contains the procedure number as its element number (EN). The procedure entry process is started if the access rights include the *enter* right.

#### 3.4.2 Entry

During a procedure entry process initiated by a local procedure call, the PC, stack registers and the local parameters are stored on the active local stack. Then a new activation record is opened on it, the stack registers are adjusted to it, the number of actual parameters is put in its first entry, pointers to the actual parameters (which may be immediate, direct or indirect) are put on the following stack entries, the effective value of the first operand is put into PC and execution proceeds.

During the procedure entry process initiated by a remote procedure call, the internal registers (not including the scratch) are pushed on the process stack, and a new dynamic NNT is built from the dynamic NNT skeleton and the ACP. The dynamic NNT skeleton contains a formal parameter table (templates in [Wulf 74]). The hardware will copy the actual parameters from the ACP to the dynamic NNT while substituting parameter nickname by the actual caller NNT entry. If this entry is not a parameter entry (in the caller's NNT), the calling domain's UID is entered into the NNT entry as the father's If the entry is already a parameter entry, it is copied as is (see sec4.1.3.1). If the parameter is given by a local pointer, it is assigned an NNT entry (in the new domain's NNT) in which the parameter's O-pointer (in terms of the segment's UID and PN) is included, instead of the father's NNT and OBP. Type consistency with the formal parameters types is checked and access rights are verified. The result is a parameter entry being put in the dynamic NNT for each parameter, and its nickname being put on the local stack.

Access rights verification for the parameters is done as follows. The access rights of the actual parameter are merged with those of the corresponding formal parameter, thus may be amplified. Then they are compared to the required access rights of that NNT entry, as compiled by the compiler. Entry to the procedure is denied if any parameter has less access rights than the minimum required access rights. If a parameter has more access rights then the maximum required access rights, the access rights checking for it is disabled for the current activation of NNT. Amplification of access rights may take place only if the procedure has a special capability for the parameter's type manager (see Section 5.4.3).

After building the dynamic NNT, the hardware generates a new active local stack, opens an activation record on it and puts the number of parameters and a local/remote flag in its first entry. Then the internal registers are set to their new values, the effective value of the first operand is put into PC and execution proceeds.

local/remote

n

Pn

.

.

.

.

P1

Figure 3-3: Local stack after call

# 3.4.3 Parameters Accessing

After a procedure call, the local stack contains the number of local parameters n at stack location 0 (see Figure 3-3). That means that there are n parameter pointers stored in the n stack locations -1 to -n, where parameter Pk's pointer is stored at stack location k-n-1. Therefore parameter Pk is addressed by using stack addressing mode with a negative displacement k-n-1. The hardware checks that  $k \le n$ .

If n=0 it means that there are no actual parameters.

Remote calls generate parameter entries in the dynamic NNT, with nicknames in the local stack.

Parameters may be called by value, using the immediate mode in the ACP entries, or called by reference, using the other addressing modes.

#### 3.4.4 return