# A GENERAL APPROACH TO MULTIPROCESSOR SCHEDULING

Sung Jo Kim

Department of Computer Sciences The University of Texas at Austin Austin, Texas 78712-1188

TR-88-04

February 1988

#### A GENERAL APPROACH TO MULTIPROCESSOR SCHEDULING

#### **ABSTRACT**

As a variety of general-purpose multiprocessor systems have been recently designed and built, multiprocessor scheduling is becoming increasingly important. Multiprocessor scheduling is a technique to exploit the underlying hardware in a multiprocessor system so that parallelism existing in an application program can be fully utilized and interprocessor communication time can be minimized. Traditionally, most research on multiprocessor scheduling has focused on the development of specific scheduling strategies to take advantage of unique characteristics of a specific multiprocessor system or application program. In this thesis, we define and characterize scheduling techniques and related heuristic mapping algorithms which are applicable to a spectrum of multiprocessor systems and a broad class of application programs.

The fundamental idea we use is that multiprocessor scheduling can be regarded as a series of mappings from a computation graph (representing an application program) to a virtual architecture graph (representing an optimal architecture for the program) and eventually to a physical architecture graph (representing a target multiprocessor system). We propose linear clustering and linear cluster merging as effectual heuristics. After linear clustering and merging, the computation graph is transformed into a virtual architecture graph. This graph represents an optimal architecture which compromises between two conflicting goals, minimization of interprocessor communication and maximization of potential parallelism, and satisfies the other goals, throughput enhancement and workload balance, relatively well. Then we develop two efficient scheduling algorithms which map the optimal architecture graph onto a physical architecture graph which may represent either a homogeneous or a heterogeneous multiprocessor system. These algorithms

rely not only on local information but also on limited global information. Finally, we present the result of performance evaluation of the mapping algorithms on an Intel iPSC with 32 processors and a Sequent Balance with 10 processors.

## **Table of Contents**

| Abstract   |                                                       | i  |

|------------|-------------------------------------------------------|----|

| Chapter 1. | Introduction                                          | 1  |

| 1.1. An    | Overview of the Thesis                                | 2  |

| 1.1.1.     | Problem Statement                                     | 2  |

| 1.1.2.     | Approach                                              | 6  |

| 1.1.3.     | Results: Theoretical and Practical                    | 8  |

| 1.2. Org   | ganization of the Thesis                              | 9  |

| Chapter 2. | Multiprocessor Scheduling Problem                     | 11 |

| 2.1. Mu    | Itiprocessor Scheduling Strategies                    | 12 |

| 2.2. Rev   | view of Previous Multiprocessor Scheduling Strategies | 14 |

| 2.2.1.     | Scheduling Strategies for Loosely-Coupled Systems     | 14 |

| 2.2.2.     | Scheduling Strategies for Tightly-Coupled Systems     | 16 |

| 2.2.3.     | Cost Functions in Previous Approaches                 | 19 |

| 2.2.4.     | Discussion on Previous Strategies                     | 20 |

| 2.3. Cor   | mplexity Issues of Multiprocessor Scheduling Problems | 21 |

| Chapter 3. | The Models for Multiprocessor Scheduling              | 25 |

| 3.1. The   | Graph Models for Multiprocessor Scheduling            | 25 |

| 3.1.1.     | The Model for Computation Graphs                      | 26 |

| 3.1.2.     | The Model for Architecture Graphs                     | 31 |

| 3.2. The   | Conceptual Model for Generalized Multiprocessor       |    |

| Sch        | neduling                                              | 33 |

| 3.2.1.     | Generalized Multiprocessor Scheduling Model           | 34 |

| 3.2.2.     | Logical and Physical Mappings                         | 37 |

| Chapter 4. Multiprocessor Scheduling Based on Linear Clustering and |    |

|---------------------------------------------------------------------|----|

| Merging                                                             | 38 |

| 4.1. Linear Clustering                                              | 38 |

| 4.1.1. Characterization of Linear Cluster                           | 38 |

| 4.1.2. Justification of Linear Clustering                           | 41 |

| 4.2. Linear Cluster Merging and Its Optimality                      | 46 |

| 4.2.1. Level Number and Related Definitions                         | 46 |

| 4.2.2. Linear Cluster Merging                                       | 50 |

| 4.2.3. Merging Conditions                                           | 51 |

| 4.2.4. Properties of Linear Clustering and Merging                  | 55 |

| 4.3. Iterative Refinement of Linear Cluster                         | 59 |

| 4.4. More Clarification on Linear Clustering                        | 63 |

| 4.4.1. Definitions                                                  | 64 |

| 4.4.2. Hierarchical Expansion                                       | 65 |

| 4.4.3. Overlapped Nodes and Overlapped Computation Graph            | 70 |

| 4.4.4. Preclustering                                                | 74 |

| 4.4.5. Linear Clustering of Cyclic Computation Graphs               | 76 |

| Chapter 5. Physical Mapping                                         | 78 |

| 5.1. Dominant Request Tree                                          | 79 |

| 5.2. Homogeneous Mapping                                            | 82 |

| 5.2.1. Homogeneous Mapping Algorithms                               | 83 |

| 5.2.2. Discussion                                                   | 93 |

| 5.3. Heterogeneous Mapping                                          | 95 |

| 5.3.1. Characterization of Resources                                | 95 |

| 5.3.2. Dominant Service Tree                                        | 97 |

| 5.3.3. Overview of Heterogeneous Manning                            | 98 |

| 5.3.4. Issues on Heterogeneous Mappings       | 101 |  |

|-----------------------------------------------|-----|--|

| 5.3.4.1. Mapping Order                        | 101 |  |

| 5.3.4.2. Node Information                     | 103 |  |

| 5.3.4.3. Scheduling with Resource Constraints | 105 |  |

| 5.3.5. Heterogeneous Mapping Algorithms       | 106 |  |

| 5.3.6. Discussion                             | 117 |  |

| Chapter 6. Performance Evaluation             | 118 |  |

| 6.1. Experimental Environments                | 119 |  |

| 6.2. Performance Metrics                      | 120 |  |

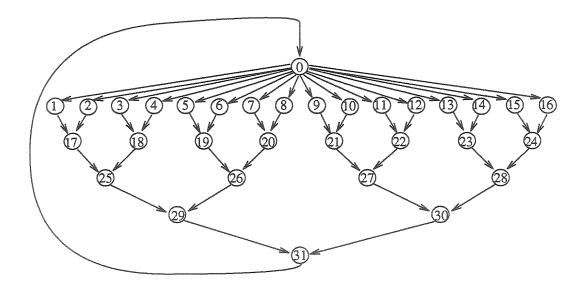

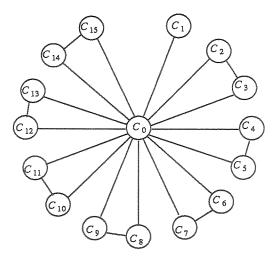

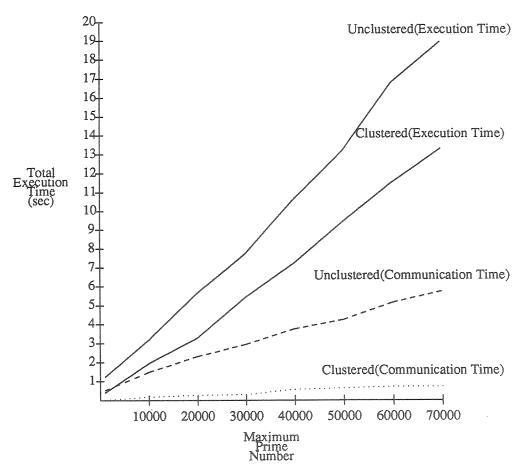

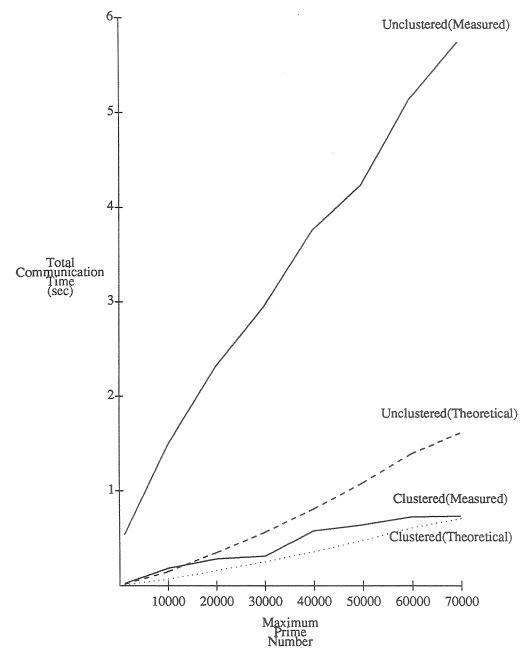

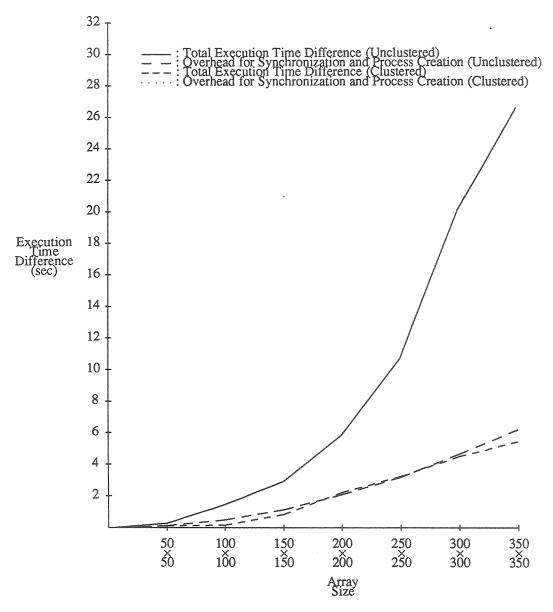

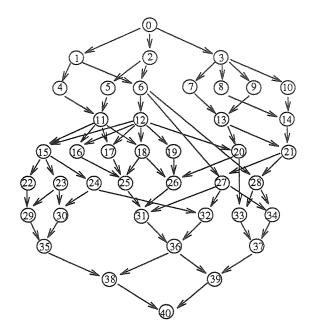

| 6.3. Calculation of Prime Numbers             | 121 |  |

| 6.4. Forward Elimination of Matrices          | 127 |  |

| 6.5. Synthetic Program                        | 133 |  |

| Chapter 7. Concluding Remarks                 |     |  |

| Bibliography                                  |     |  |

#### CHAPTER 1

#### INTRODUCTION

For the past several years, we have witnessed a surge of new general-purpose multiprocessor systems unequaled since the first generation multiprocessors like the CMU C.mmp [MAS82] and the BBN Pluribus [KAT78] were built around the early 1970's. This is a natural approach to solve computationally intensive problems as hardware technologies approach physical limitations.

Depending on the degree of coupling among processors (i.e., the amount of time it takes to move data from one processor to another or to initiate an action on one processor from another), there is a spectrum of multiprocessor systems from loosely-coupled to tightly-coupled systems. On one extreme, a shared-memory architecture like the Sequent Balance [SEQ86] is an example of a tightly-coupled multiprocessor system. On the other extreme, a wide area network like the ARPANET [HEA70] can be regarded as a loosely-coupled multiprocessor system. Between these two extremes lie most architectures like the IBM RP3 [PFI85], the BBN Butterfly [BBN85a], the NYU Ultra [GOT83a], the Flex/32 [MAT85], the Intel iPSC [INT87], the Ncube/ten [NCU85], and the Connection Machine [HIL85]. Note that general-purpose multiprocessor systems we deal with are assumed to employ MIMD (multiple-instruction and multiple-data stream) type architectures. Consequently, an array processor like the Illiac IV [BOU72] will not be considered as a multiprocessor system by itself, but as a processor component of a multiprocessor system.

Even though an enormous amount of theoretical work has been done to find optimal solutions of multiprocessor scheduling problems, no practical, generally applicable polynomial-time algorithm has yet been found. The obvious approach then is to concentrate on the development of polynomial-time algorithms that provide sub-optimal solutions in many cases. This thesis reports research on the

development of scheduling techniques and related scheduling algorithms based on heuristics which are applicable to a spectrum of general-purpose multiprocessor systems mentioned above.

In this chapter, we overview and outline this thesis. From here on we use the term *task* and *schedulable unit of computation*, which corresponds to a node in a computation graph, interchangeably.

#### 1.1. An Overview of the Thesis

In this section, we address the problem we tackle and our approach to the problem, and summarize our results and contributions.

#### 1.1.1. Problem Statement

Optimal scheduling of parallel computations to multiprocessor systems requires the optimal assignments of processors to computations and communication resources to the implementations of dependency relations between the schedulable units of computation in order to minimize total execution time for the computations. The assignment of computational work to processors must take into account both balancing the workload assigned to processors and minimizing the communication cost among processors.

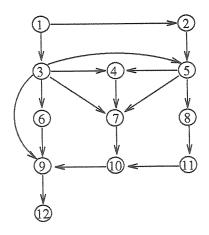

A parallel computation can be represented by a direct acyclic graph  $G_C = (N_C, E_C)$ , where  $N_C = \{n_1, n_2, \dots, n_l\}$  is a set of schedulable units of computation to be executed, and  $E_C$  specifies scheduling constraints defined on  $N_C$ . A multiprocessor system can be represented by an undirected graph  $G_P = (N_P, E_P)$ , where  $N_P = \{p_1, p_2, \dots, p_m\}$  is a set of processors, and  $E_P$  specifies interconnection network among the processors. The basic problem that we are attempting to solve is to find a mapping of  $G_C$  onto  $G_P$  which minimizes the schedule length (or makespan) defined as:

$$\max_{1 \le k \le s} \sum_{i,j \in \phi_k} (comp_i + comm_{ij}),$$

where  $\phi = \{\phi_1, \phi_2, \dots, \phi_s\}$  represents a set of paths from the root node to the leaf node in  $G_C$ , node  $n_j$  (assigned to processor  $p_y \in N_P$   $(1 \le y \le m)$ ) is a direct descendant of node  $n_i$  (assigned to processor  $p_x \in N_P$   $(1 \le x \le m)$ ) in  $G_C$ ,  $comp_i$  is computation time of  $n_i$ , and  $comm_{ij}$  is communication time from  $n_i$  to  $n_j$  ( $comm_{ij} = 0$  if  $p_x = p_y$  or  $n_i$  has no direct descendants).

An optimal schedule is one which meets the criteria of the minimum schedule length for a single parallel computation structure or the maximum total throughput for a set of simultaneously executing parallel computation structures. It must integrate scheduling of computations and dependency relations to resources. An approach which integrates consideration of all the interacting factors is one which maps a computation graph defining the computation structure (including the resource requirements for execution of each element of the computation structure) onto an architecture graph which defines the capability and capacity of the resource set of the execution environment.

This integrated approach is a substantial advancement in scope over the current state-of-the-art. Some research in multiprocessor scheduling dealt with only one of the interacting factors, usually the computation time [GOT83a, BBN85a], the workload balance [STA84, VAN84, WAN85, EAG86] or the implementation cost of dependency relations between the schedulable units of computation [HAE80, BIA85]. Other research which has considered integrated scheduling was primarily concerned with the development of the concepts rather than applicable methodologies or else were applicable only to specific configurations of resources or specific problems [FOR78, LIU78, SOL79, WIT80, BRY81, CHO82, DEG81, GOT83a, BER84, SHE85, BBN85a, LEE87].

The integrated approach defined and characterized herein requires three elements:

- A graph representation of a computation structure which integrates the specification of dependency relations and resource requirements of each schedulable unit of computation;

- A graph representation of an execution environment which includes the specification of the capabilities and capacities of the resource set;

• Algorithms for mapping from a computation graph to an architecture graph.

The research defined and described in this thesis is a first attempt at such an integrated and generally applicable approach to scheduling of parallel computation structures on multiprocessor systems. The difficulty of attainment of a fully integrated, broadly applicable and truly optimal scheduling methodology is not underestimated. In this research, we attempt to extend the state-of-the-art to include simultaneous consideration of the important elements of the multiprocessor scheduling problem. The critical element of this approach is the establishment of a general framework in which to evaluate integrated scheduling methodologies rather than the development of individual mapping algorithms which are suitable for individual applications and a specific multiprocessor system. We develop a generalized multiprocessor scheduling methodology which is applicable to a spectrum of multiprocessor systems and a broad class of application programs.

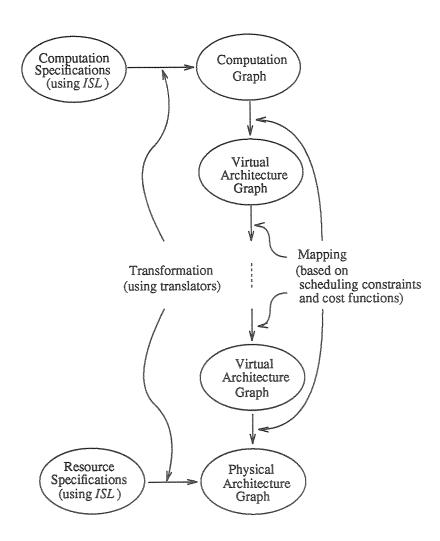

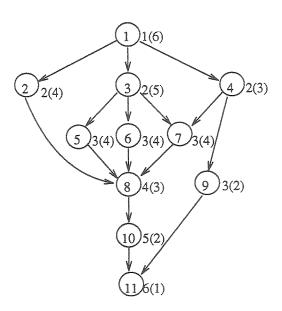

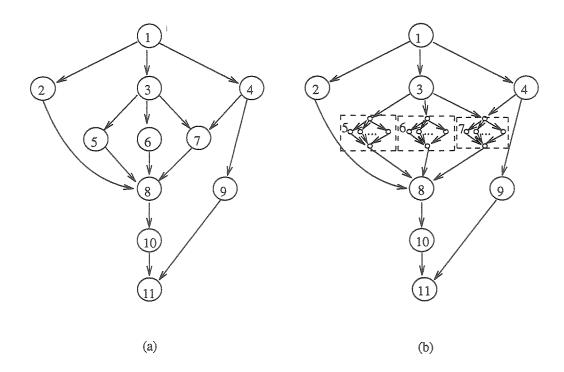

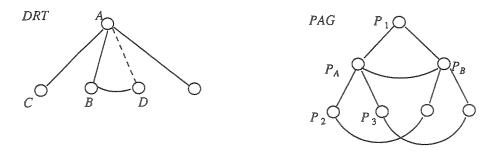

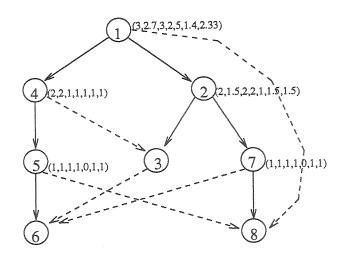

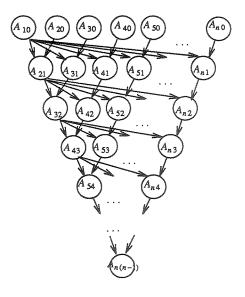

The fundamental idea on which this research is based is that multiprocessor scheduling can be regarded as a mapping between graphs. To be specific, one will take a representation of a computation as a computation graph and a representation of a multiprocessor system as an architecture graph and then formulate the problem of scheduling as the mapping of one graph onto another graph subject to specific scheduling constraints [BRO86]. In fact, we consider a series of mappings between a computation graph and an architecture graph including a direct mapping of the former onto the latter as illustrated in Fig. 1-1.

As can be seen in Fig. 1-1, a computation specification of a parallel computation structure and a resource specification of a target multiprocessor system are transformed into a computation graph and a physical architecture graph, respectively. We have designed two interface specification languages (ISL's) [KIM86a]: one for computation graph generation and the other for physical architecture graph generation. The most important motivation for designing an interface specification language for computation graphs is to create a language which defines the interface specification of the computation structures and dependency relations, including resource requirements of the structures and the relations. The nodes and directed edges in a computation graph (restructured to acyclic direct graphs, if necessary) represent respectively the bindings of operations to data and the dependency

relations between the computations executed at the nodes [BRO85]. Since in general the bindings can occur dynamically at runtime, a computation graph can be dynamic as well. In this research, however, we assume that all the bindings are fixed prior to runtime in the sense that there are no runtime bindings of operations to data objects which modify the structure of the computation graph. Consequently, a computation graph is *static*.

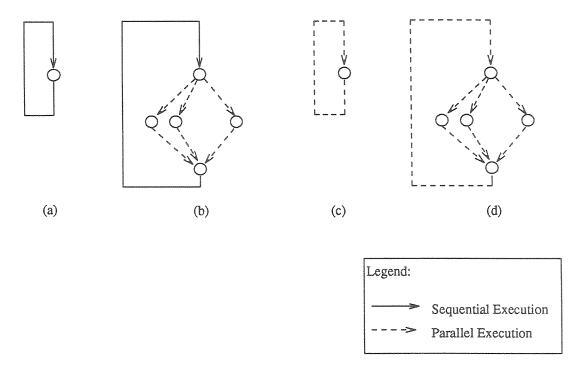

Figure 1-1 General Overview of Our Approach

There are two types of architecture graphs: virtual architecture graphs and physical architecture graphs. Both architecture graphs are undirected. A physical architecture graph represents a real multiprocessor system, and a virtual architecture graph represents an abstract multiprocessor system which is regarded as an optimal architecture for a given computation. Except in the case of direct mapping of a computation graph onto a physical architecture graph, scheduling algorithms make use of virtual architecture graphs for the initial mapping as well as the intermediate mappings. The intermediate mappings, including the initial mapping, are called logical mappings. At the final stage of the mapping, one of the virtual architecture graphs is mapped onto the physical architecture graph. This mapping is called physical mapping.

A restricted case of the general graph mapping problem is the graph isomorphism problem. It has been shown [BOK81] that the general mapping problem is computationally equivalent to the graph isomorphism problem. Unfortunately, there is no known polynomial time algorithm for solving even this restricted problem [GAR79]. Furthermore, precedence constrained scheduling problem which is a subproblem of the general scheduling problem has been proved to be *NP -complete* [ULL75]. As a result, it is clear that in order to stay in the realm of practicality, we should either rely on efficient heuristics as in [KER70, BAR81] or develop algorithms which give optimal solutions only for restricted cases [KER71, RAM72, LUK75, LLO80, CHI84, LO85]. We concentrate on the development of multiprocessor scheduling techniques and related heuristic algorithms based on graph mapping that supply efficient approximate and computationally feasible solutions. Most importantly, they are applicable to a spectrum of multiprocessor systems from loosely-coupled to tightly-coupled systems.

#### 1.1.2. Approach

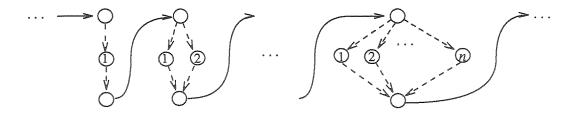

One of the contributions of this thesis is to propose new multiprocessor scheduling techniques based on *linear clustering*. A linear cluster is a connected subgraph of a computation graph which is in the form of a linear list of schedulable units of computation. Linear clustering is an effectual heuristic to compromise

between two conflicting goals of multiprocessor scheduling, minimization of interprocessor communication and maximization of potential parallelism, and to satisfy the other goals, throughput enhancement and workload balance, relatively well. The underlying idea of linear clustering is that the schedulable units of computation that are sequentially dependent on each other are to be assigned to one processor, while those that are mutually independent are to be allocated to separate processors. The critical restriction of linear clustering is that it expects a computation graph to be acyclic. In order to relieve this restriction, we identify cases in which cyclic computation graphs can be transformed into acyclic graphs in a straightforward manner.

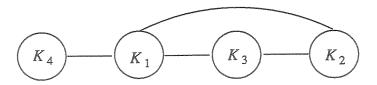

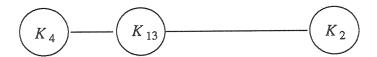

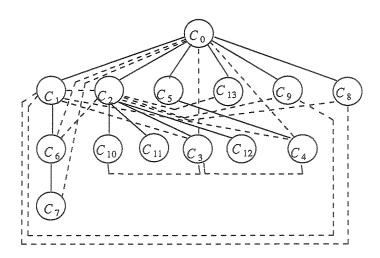

A computation graph is transformed into a virtual architecture graph by linear clustering. The virtual architecture graph in fact represents an optimal multiprocessor system for the computation graph. The optimal multiprocessor system may provide one processor to every linear cluster so that mutually independent tasks belonging to different linear clusters can be executed in parallel as long as possible. Furthermore, direct communication links are always available for any adjacent linear clusters in the optimal multiprocessor system. The virtual architecture graph may be transformed into another virtual architecture graph by *merging* two or more linear clusters into one cluster. Two linear clusters  $K_1$  and  $K_2$  are combined into one if  $K_2$  may start only after  $K_1$  finishes or may be executed only while  $K_1$  is idle. It contributes to further balancing the workload of processors, and further reducing the amount of resources to be utilized and interprocessor communication overhead.

Virtual architecture graphs can be constructed independently of the target multiprocessor system. As a result, the characteristics of the target system matter only during physical mappings. After constructing a virtual architecture graph which represents the optimal multiprocessor system for a given computation graph, we just need an optimal mapping of the virtual architecture graph onto a physical architecture graph which represents the target multiprocessor system. We develop homogeneous and heterogeneous mapping algorithms for homogeneous and heterogeneous multiprocessor systems, respectively.

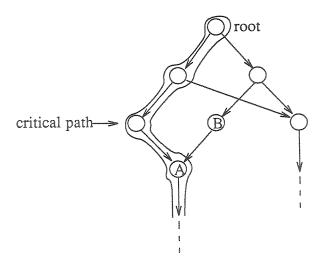

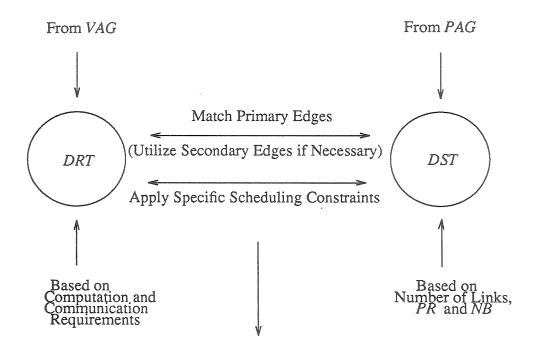

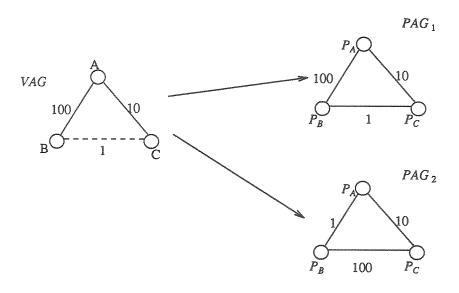

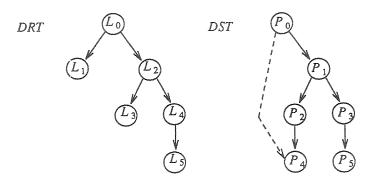

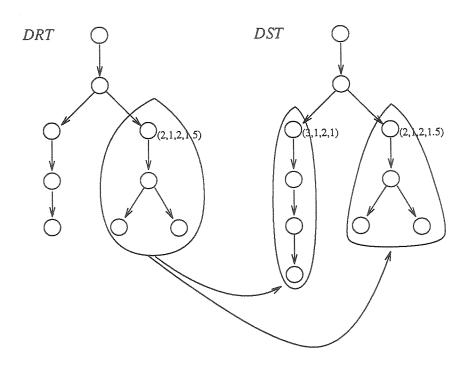

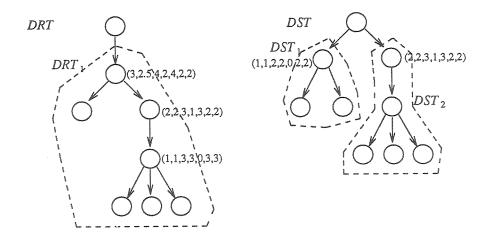

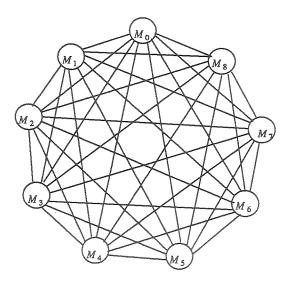

These algorithms rely on not only local information but also on limited global information. The key issue is then how to reduce the mapping complexity while sacrificing the optimality as little as possible. A dominant request tree is a maximal spanning tree of a virtual architecture graph. It provides limited global information on the virtual architecture graph such as the mapping order of the nodes and the edges whose adjacency should be maintained. Both mapping algorithms utilize dominant request trees, but take quite different approaches to mapping the trees onto physical architecture graphs. Most importantly, in the case of homogeneous mappings, the trees are directly mapped onto physical architecture graphs. On the other hand, in the case of heterogeneous mappings, they are mapped onto dominant service trees. A dominant service tree is a maximal spanning tree of a physical architecture graph. For heterogeneous mappings, one of the important issues is how to identify and utilize resources with high performance as much as possible. A dominant service tree provides such information.

#### 1.1.3. Results: Theoretical and Practical

The problem of scheduling of general static computation graphs to general multiprocessor architectures is expressed as a sequence of transformations on computation graphs and architecture graphs, and a series of mappings among the graphs. Explicit consideration is given to both homogeneous and heterogeneous multiprocessor architectures. Algorithms for these transformations and mappings are given and are characterized by their computational complexity. Bounds on the number of processors needed to attain maximum parallelism at a given level of task granularity are derived. It is shown by analysis and by experimental demonstration that the scheduling methodology developed, while known in general to produce sub-optimal schedules, does produce effective schedules with reasonable effort.

New schemes for transformation of the computation graphs of a large class of loop structured programs into a form to which the general scheduling methodology applies are defined and described. In addition, they are integrated into the transformation process.

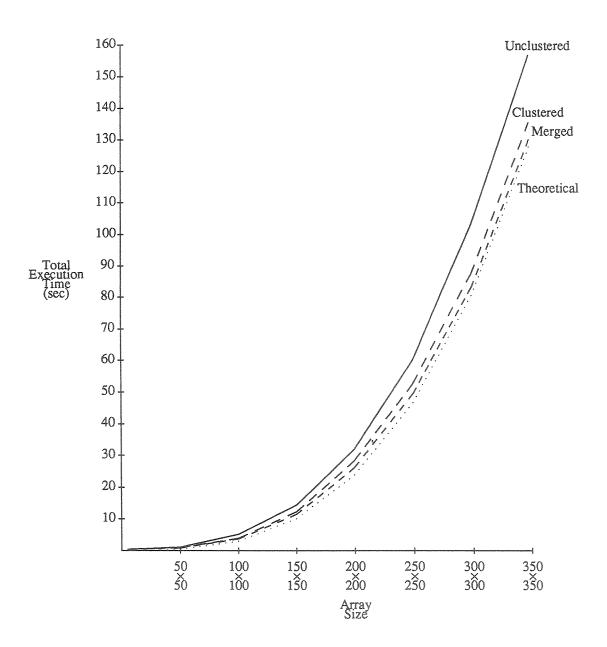

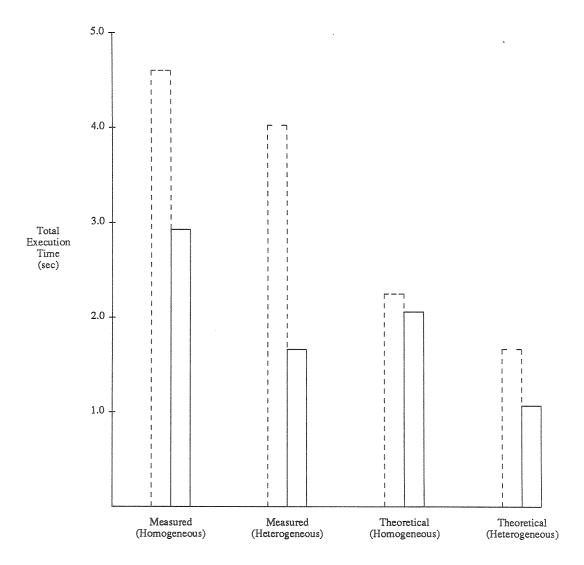

Experiments are conducted on both a distributed memory architecture, an Intel iPSC with 32 processors and a shared memory architecture, a Sequent Balance with 10 processors. The computation graphs used in the experiments include a regular graph with a cycle, a regular graph without a cycle and an irregular graph. The Intel Hypercube is turned into a heterogeneous multiprocessor system by deliberate manipulation of the computation times and communication times of the nodes and edges of the irregular computation graph, respectively. The results of the experiments reveal substantial performance enhancement after linear clustering and linear cluster merging of the computation graphs through application of the general scheduling methodology and sub-optimal results in some cases where optimal execution times can be derived.

## 1.2. Organization of the Thesis

We begin in Chapter 2 by taxonomizing general-purpose multiprocessor systems. Next, we discuss various multiprocessor scheduling strategies: *ad-hoc, manual, automatic* and *restricted* schedulings. Traditionally, depending on the degree of coupling among processors, there have been two main multiprocessor scheduling: one for loosely-coupled systems and the other for tightly-coupled systems. After reviewing the previous strategies and cost functions, we discuss their weaknesses.

The graph models described in Chapter 3 are concerned with the properties of graphs we deal with for multiprocessor scheduling. This chapter introduces two types of graphs: computation graphs and architecture graphs. In fact, we make use of the same graph model to represent two different types of architecture graphs: virtual and physical architecture graphs. This chapter also introduces the conceptual model for a generalized multiprocessor scheduling. We use this model to realize the different scheduling strategies mentioned in Chapter 2.

In Chapter 4, we propose a new multiprocessor scheduling technique based on *linear clustering* and *linear cluster merging*. The ideas of linear clustering and merging are explained and justified. Then we identify the cases that cyclic computation graphs may be transformed into acyclic graphs in a straightforward manner.

In this chapter, we also establish some interesting properties of linear clustering and merging.

The main subject of Chapter 5 is to describe efficient heuristic, polynomialtime mapping algorithms for the different types of multiprocessor systems: homogeneous and heterogeneous systems. We explain each mapping algorithm and discuss the time complexity of each. We also propose and justify transformations of virtual architecture graphs and physical architecture graphs into dominant request trees and dominant service trees, respectively.

In Chapter 6, the performance of the proposed mapping algorithms is measured and analyzed. After summarizing our experimental environments, we enumerate the performance metrics being considered in the experiments. Then, we discuss the implementations and the results of performance evaluation in order to show how the proposed mapping algorithms behave on the different types of multiprocessor systems and computation graphs.

Finally, concluding remarks are contained in Chapter 7. In this chapter, we summarize our research and suggest the future research directions.

#### **CHAPTER 2**

#### MULTIPROCESSOR SCHEDULING PROBLEM

General-purpose multiprocessor systems can be classified into four categories based on the level of couplings among processors and memory modules as follows:

- very tightly-coupled systems;

- · tightly-coupled systems;

- loosely-coupled systems;

- very loosely-coupled systems.

The first category includes systems like the Sequent Balance 21000 [SEQ86]. It has one global memory shared by all the identical processors, all of which are connected by one global bus. The second category includes the IBM RP3 [PFI85], the NYU Ultracomputer [EDL85a, EDL85b] and the BBN Butterfly [BBN85a]. Each processor in these systems has a local memory which can be shared efficiently by the other processors through a switching network. In particular, the RP3 also supports software-controllable shared-memory. As a result, a single system like the RP3 may realize a spectrum of the coupling among its processors. This category also includes the Flex/32 [MAT85] in which each processor has its own local memory, and all processors can share a global memory through a global bus. The Intel iPSC [INT87] belongs to the third category. The processors, each of which has local memory, are connected by asynchronous communication links. Since there is no shared memory in the iPSC, the processors communicate with one another by message passing. Finally, a wide area network like the ARPANET [HEA70] or a local area network based on the Ethernet [MET76] can be regarded as a very loosely-coupled system.

Scheduling strategies for multiprocessor systems can be discussed in terms of the following factors:

- The time (hardware design time, compile time, load time and runtime) at which mappings are fixed and elements of the computations are bound to resources;

- The degree of automation of mappings and bindings;

- The degree of coupling among resource sets;

- The cost metrics or cost functions used as decision variables.

In this section, we first discuss multiprocessor scheduling strategies in terms of the four factors. After reviewing previous approaches to multiprocessor scheduling and cost functions, we discuss their weaknesses. Finally, we discuss the complexity of multiprocessor scheduling problems being investigated in this thesis.

## 2.1. Multiprocessor Scheduling Strategies

For a given multiprocessor system having a certain degree of coupling, depending on the degree of automation of mappings and bindings provided for the user, there is a spectrum of multiprocessor scheduling strategies. These range from leaving the user the entire burden of managing processors in the system to simply requiring the user to define tasks and specify dependency relations among tasks. The degree of automation in fact depends on the level of visibility of multiprocessor systems exposed to the user. There are four classes of multiprocessor scheduling strategies in the spectrum:

- Ad-hoc multiprocessor scheduling: This is suitable for multiprocessor systems like systolic arrays [KUN82] whose configurations and operational characteristics should be unfolded as low as the hardware gate level to the user. As a matter of fact, there is virtually no resource scheduling by the operating system, because the user is fully responsible for allocation of processors in the system and synchronization between them; it is even required to specify the complete timing of all instructions for all the processors in the system. The binding of processors to tasks is fixed at hardware design time or possibly at compile time [KUN84].

- Manual multiprocessor scheduling: This strategy aims at handling multiprocessor systems whose physical configuration of resources and status are partially

visible to the user (e.g., the number of active processors, the connectivity of processors, the communication costs, the characteristics of resources, etc.). The user can make use of such visibility for the actual resource scheduling. For example, he may specify statically process working sets or may designate a specific processor to execute a particular task as in the Medusa operating system [OUS80, OUS82] for Cm\* [JON80]. The processors are bound to tasks at compile time or possibly at load time.

- Automatic multiprocessor scheduling: The actual allocation of resources is hidden from the user and is done by the operating system of a multiprocessor system. Nothing related to physical resources is visible to the user; however, he is responsible for the specification of dependency relations among tasks as in the Uniform System [BBN85b] for the Butterfly system [BBN85a] or as in Dynix for the Sequent Balance [SEQ86]. In the Uniform System, the binding of processors to the tasks can be done either before or at runtime. Because of the flexible binding time, the tasks may be migrated dynamically to other processors to balance the workload of each processor or to bypass failed processors. The Dynix system allows both static and dynamic schedulings. The latter is useful for workload balancing among processors.

- Restricted multiprocessor scheduling: This is a variation of the preceding two strategies. It may restrict utilization of full resources available in a multiprocessor system or the way they can be used. For example, the Cedar system [GAJ83] and the IBM RP3 [PFI85] may be partitioned into subsystems so that each subsystem can be assigned to a different application program to improve the total throughput.

Depending on scheduling objectives, we can define a variety of cost functions which may be expressed in terms of various cost metrics. In fact, those functions are utilized as decision variables for reducing the solution space during mapping. As a result, multiprocessor scheduling strategies (more specifically, mappings) are significantly influenced by the cost functions. The most important and frequently used cost metrics are the computation cost and the interprocessor communication cost. We will discuss them in detail in the following section.

## 2.2. Review of Previous Multiprocessor Scheduling Strategies

Basically, there have been two main streams of research on multiprocessor scheduling strategies: one for loosely-coupled systems and the other for tightly-coupled systems. In this section, we discuss scheduling strategies for each system. We also discuss cost functions and metrics considered in the previous research. Note that the visibility of a multiprocessor system exposed to the user (which determines the degree of automation of scheduling) has not been considered explicitly in any previous study of multiprocessor scheduling strategies.

## 2.2.1. Scheduling Strategies for Loosely-Coupled Systems

Several approaches to scheduling strategies in loosely-coupled systems have been suggested in the past. They can be roughly classified into three categories, namely, graph theoretic [STO77, STO78], mathematical programming [LEE77, CHU80, MA82], and heuristic methods [GYL76, BOK81, EFE82, MA82, KAS84, PAT84, STA84, VAN84, CAM85, SHE85, LEE87, SAD87].

The graph theoretic approach uses a computation graph to represent an application program and applies the minimal-cut algorithm [STO77] to the graph. The goal of this scheduling is to minimize the total execution cost, defined as the sum of the computation cost and the interprocessor communication cost. In this approach, in order to minimize the total cost, a computation graph is modified so that each cutset in the modified graph corresponds in a one-to-one fashion to a task allocation, and the weight of the cutset is the total execution cost for that allocation. With this modification, a maximum flow problem [FOR64] is solved on the modified graph. The minimum weight cutset obtained from this determines the task scheduling which is optimal in terms of the total cost.

Even though the min-cut max-flow algorithm adopted by this approach guarantees an optimal solution, it is only practical for finding a minimum cost allocation between two or three processors. Moreover, it does not deal with such issues as workload balancing, resource constraints (e.g., memory size), and dependency relations among tasks. Rao et al. [RAO79], however, have tried to find a

minimum feasible allocation of tasks to two processors, one of which has limited memory, as an attempt to include limited scheduling constraints.

In the mathematical programming approach, the scheduling problem is formulated as an optimization problem and solved with linear programming techniques. This approach has been applied with some success to the file allocation problem [CHU69] in a loosely-coupled multiprocessor system. For multiprocessor scheduling purposes, it can be used to minimize the total execution cost subject to some given scheduling constraints. The objective function is the total cost which is also a sum of the computation cost and the interprocessor communication cost. The constraints might be a memory size restriction on each processor or response time, for example.

As in the previous approach, this approach gives us an optimal solution. It is more flexible than the previous one, however, since it allows various scheduling constraints to be introduced into the model. This is difficult or impossible with the graph theoretic approach. Since this approach suffers the problem of increased complexity as the dimension of the problem becomes larger, it is not suitable for time-critical applications. It was reported in [CHU80] that it typically took a CDC 6000 series computer two to three minutes to schedule 25 modules onto 15 processors. As a result, it is not practical to specify more than a couple of constraints. Furthermore, there is no provision for specifying dependency relations.

The heuristic approach, in general, provides an approximate solution for multiprocessor scheduling. Even though the two previous approaches provide us with optimal solutions, it is unlikely to find efficient exact algorithms based on them for the general mapping problem within the reasonable time constraints. The heuristic approach is very useful when an optimal solution is not required, not obtainable, or can not be obtained within time limits. Note that heuristic approaches may be based on a combination of the previously described approaches.

As a result, for more flexible multiprocessor scheduling, it is imperative to rely on heuristic algorithms which are computationally tractable. In general, heuristics will not guarantee optimal solutions, but may allow the specification of much more scheduling constraints than the previous two approaches, since they are

less sensitive to the magnitude of the scheduling problem.

## 2.2.2. Scheduling Strategies for Tightly-Coupled Systems

There are not as many distinct scheduling approaches for tightly-coupled systems as for loosely-coupled systems. Scheduling strategies for tightly-coupled systems may be categorized based on the degree of visibility of underlying multiprocessor architectures; the more visible the architectures are, the more responsible the user is for resource scheduling.

Ousterhout [OUS82] proposes a multiprocessor scheduling strategy for Cm\* which is appropriate for a tightly-coupled environment in which some characteristics of the architecture are known to the user. That is, the configuration of the multiprocessor system is partially exposed to the user. As a result, processor scheduling may rely on the user's ingenuity. For example, the user can designate a processor to which he prefers to allocate a task. He also should know the number of active processors in the system (more preferably, in the same cluster) so that all of the tasks contained in a *task force* if are guaranteed to be coscheduled (i.e., executed concurrently on different processors). Coscheduling is based on the observation that the duration of a busy-waiting time is usually less than two context switching times. It may prevent the possibility of process thrashing and deadlock.

Recently, several multiprocessor scheduling strategies have been proposed under the assumption that the configurations of multiprocessor systems are almost concealed from the user. Those are the Uniform System approach [BBN85b] in the Butterfly system [BBN85a], the self-scheduling approach [LUS85, TAN85] in the Cedar system [GAJ83], the self-service approach [EDL85b] in the Ultracomputer [GOT83a], and the Dynix approach in the Balance [SEQ86]. The Uniform System treats each processor as able to execute any task. The user is required to supply task generators which generate the next tasks that will be allocated to any available

<sup>†</sup> Even though Cm\* has no central, shared memory in the sense of C.mmp [FUL73], local memory of each processor can be shared by other processors with some degraded performance. See [HAY82] for the cost ratio for different types of memory references. †† A task force can be defined as a set of heavily interacting tasks.

processor. Self-scheduling is a non-preemptive, distributed scheduling strategy that allows processors to schedule themselves without intervention from the operating system. Self-service is a centralized strategy, in which a single central queue of ready tasks is shared by all processors. Depending on scheduling purposes, Dynix provides three different strategies: prescheduling, static scheduling and dynamic scheduling. In order to run a different task on each processor, we should rely on the first one. On the other hand, the others are useful if we have identical tasks to execute. If a program can be partitioned into tasks in such a way that each has the same computation time, static scheduling is better than dynamic scheduling. No matter which type is chosen, it is not necessary to perceive the underlying architecture. It will be informative (but not imperative) to know the maximum number of available processors. Since scheduling strategies in these systems are basically identical and have similar problems, we will discuss only the Uniform System in detail.

The Butterfly parallel processor is a tightly-coupled, shared-memory, homogeneous system. The Uniform System implements a methodology for task scheduling in the Butterfly system. It achieves parallel processing by utilizing any active processor as soon as it becomes available. A similar approach has been adopted by the HYDRA for C.mmp [MAS82], by Dynix's dynamic scheduling scheme for the Balance [SEQ86] and by the operating system for the Pluribus [KAT78]. While the system automatically allocates tasks to processors, the user is responsible for supplying a task generator procedure to generate next tasks to run. Since the details of machine configuration are hidden from the user, he is not burdened with dynamic machine reconfiguration. Consequently, its configuration can be changed dynamically according to the availability of its processors without interfering with execution of the user's programs.

There are several drawbacks to the approach taken by the Uniform System. In fact, the other approaches also have similar problems. First of all, task generators contain any number of *internal* critical regions through which processors must proceed one by one. For example, the regions usually include the following operation:

$index = Atomic\_add(p_1, 1).$

This operation  $^{\dagger}$  atomically fetches and adds 1 to the location pointed to by  $p_1$  to generate the next index value. Since processors must proceed through the critical region in a certain serial order, the region will limit the maximum number of processors that can be utilized simultaneously, no matter how small the region is [BBN85b]. Furthermore, it may force the user not to choose a smaller size of task, because the size may increase the overhead of the critical region in inverse proportion to the task size. In order to reduce the overhead, the notion of chunking [EDL85b] may be useful.

Secondly, the Uniform System approach may increase computation overhead (e.g., the amount of interprocessor communication) unnecessarily. For a given computation, because of data dependencies among tasks, there is always a minimum time span to complete the computation even if an unlimited number of processors is available. Therefore, there is an optimal number of processors required to complete the computation in the minimum time. The Uniform System may utilize more processors than optimal whenever there are available processors and one or more tasks waiting for the processors. This use of additional processors may not increase the performance of the system at all. Instead, it may increase overhead such as amount of interprocessor communication, remote memory access time and task creation time, because of unnecessary (or excessive) creation/distribution of tasks.

The next problem of the Uniform System is that for parallel processing it does not allow multiprogramming; in other words, it allows only a single user program to execute and only one task per processor in the system. This is a serious restriction, since it prevents the user from parallel processing more than one task or application program simultaneously. In spite of the potential for waste in busy-waiting, what we gain from this simple restricted scheduling is that unnecessary context switchings can be eradicated.

<sup>†</sup> The NYU Ultracomputer and the Cedar multiprocessor system have similar synchronization primitives. The former provides *Fetch-and-Add* [GOT83b] and the latter provides more general primitives such as {variable, test condition, operation on key, operation on data} [TAN85].

The final problem of the Uniform System is that each processor may be forced to be idle longer than necessary. As soon as a processor becomes available and as long as there are tasks yet to be executed, the task generator residing on the processor generates a next task and executes it. Even after a task is allocated to the processor, however, it may be forced to remain idle further until some sequencing constraints are satisfied. Since the Butterfly system allows each processor to run no more than one task for parallel processing, the power of the processor may be wasted. On the other hand, if we consider a multiprocessor system which allows multiprogramming, we need more coordinated scheduling to prevent premature occupation of a processor and waste of its processing power. For example, allocation of a task which prematurely occupies the processor may be deliberately delayed until all the necessary sequencing constraints are satisfied. During that time, the processor may execute another task which can be executed immediately, rather than being idle.

## 2.2.3. Cost Functions in Previous Approaches

In the previous research, many cost functions using a variety of cost metrics have been proposed especially for loosely-coupled multiprocessor systems. The most basic cost metrics are the computation cost and the interprocessor communication cost. Assuming that A is an allocation matrix  $(a_{ij})$  of t tasks to p processors, a cost function to evaluate the total execution cost can be formulated as the sum of the two cost metrics [CHU80, MA82, SHE85]:

$$\sum_{i=1}^{t} \sum_{k=1}^{p} (\omega \cdot a_{ik} \cdot T_{comp_{ik}} + \sum_{j>i}^{t} \sum_{l>k}^{p} a_{ik} \cdot a_{jl} \cdot T_{comm_{ij}}).$$

Allocation matrix A is defined as follows:

$$a_{ik} = \begin{cases} 1, & \text{if task } i \text{ is assigned to processor } k; \\ 0, & \text{otherwise.} \end{cases}$$

$T_{comp_{ik}}$  is the computation cost for task i on processor k. Similarly,  $T_{comm_{ij}}$  is the communication cost between task i and task j. The scale factor  $\omega$  is used to nor-

malize different cost metrics. Because the time complexity to find an optimal allocation, A, increases rapidly as the number of processors increases, either various scheduling constraints or heuristic information has typically been employed to reduce complexity. For example, Ma et al. [MA82] proposed a branch and bound technique using allocation constraints; Shen and Tsai [SHE85] made use of the  $A^*$  algorithm to reduce the feasible solution space.

Another interesting cost metric proposed in [BOK81] is cardinality, which is the number of edges connecting tasks which are mapped onto adjacent processors. In this case, the optimal scheduling is one that maximizes cardinality. Stankovic and Sidhu's adaptive bidding algorithm [STA84] takes into account various parameters. They propose interesting cost metrics based on memory utilization, processor workload, task distribution/cluster, and others. The wave scheduling strategy proposed by van Tilborg and Wittie [VAN84] makes use of a unique cost metric: total CPU time to schedule a task group of size S successively. Efe [EFE82] proposed a cost metric to measure processor workload: assuming p is the number of processors in a multiprocessor system, the workload  $q_i$  is represented by  $\frac{l_i}{l_{avg}}$ , where  $l_i$  is the queue length in processor i and  $l_{avg}$  is defined as  $\sum_{i=1}^p \frac{l_i}{p}$ . The other cost metrics proposed include speedup [AE82], turnaround time [NI81] and scheduling length [KAS84].

## 2.2.4. Discussion on Previous Strategies

Previous approaches have focused mainly on the development of specific scheduling strategies based on the coupling factors of processors in multiprocessor systems. Some of them also attempt to take advantage of the unique hardware characteristics such as interconnection topologies of multiprocessor systems under consideration. Since each strategy is usually an ad-hoc scheme, it is in most cases applicable to some limited class of multiprocessor architectures (e.g., tightly-coupled homogeneous systems [GOT83a, BBN85a], loosely-coupled homogeneous systems [SOL79, WIT80], loosely-coupled heterogeneous systems [FOR78,

CHO82], and multicomputers connected in point-to-point fashion [BRY81]).

Moreover, various simplifying assumptions are common. For example, Bokhari [BOK81] studies the assignment of tasks to processors with the restriction that the number of tasks should be less than or equal to the number of processors. Shen and Tsai [SHE85] propose a graph matching approach for solving task assignment to processors, but ignore dependency relations among tasks. Some approaches have limited scheduling objectives; they find the best schedule with respect to either the total computation time [GOT83a, BBN85a] or interprocessor communication time [HAE80, BIA85]. Other approaches are interested in balancing the workload of the total multiprocessor system [STA84, VAN84, WAN85, EAG86].

In most scheduling strategies for tightly-coupled systems, specific interconnection networks are assumed such as the Butterfly switch, the Omega network, the SW-Banyan network or even a composition of them [PFI85]. On the other hand, most of them do not take into account scheduling constraints, resource limitations, and the current workloads of processors in the system. It is also assumed that each processor is identical (i.e., all have the same processing speed and memory capacity). Furthermore, some multiprocessor systems such as the Butterfly allow allocation and execution of only one task on a processor at a time; each task is nonpreemptive and occupies the processor until its execution is completed. Finally, while most scheduling strategies make heavy use of busy-waiting as a synchronization mechanism, there is little attempt to reduce or avoid using it.

All in all, there are a myriad of multiprocessor scheduling strategies which can be applied to specific multiprocessor systems. On the other hand, there is little research which attempts an integrated approach to multiprocessor scheduling which could be applicable to various multiprocessor systems regardless of underlying architectural characteristics.

## 2.3. Complexity Issues of Multiprocessor Scheduling Problems

In this section, in order to justify the development of heuristic algorithms, we

discuss the complexities of three multiprocessor scheduling problems to be investigated in this thesis:

- SP1) Given a minimum schedule length L, what is the minimum number of fully-connected identical processors in order to finish a parallel computation within L, which consists of a set  $S = \{s_1, s_2, \dots, s_m\}$  of mutually independent schedulable units of computation with arbitrary computation times?

- SP2) What is the minimum schedule length of a parallel computation consisting of a set of  $S = \{s_1, s_2, \dots, s_m\}$  of mutually dependent schedulable units of computation with arbitrary computation times and zero communication times on the fixed number of  $p \geq 2$  fully-connected identical processors?

- SP3) What is the minimum schedule length in SP2, if the unlimited number of fully-connected identical processors are available?

We first prove that the decision problems DP1 and DP2 corresponding to the first two optimization problems SP1 and SP2, respectively, are *NP -complete*. We then discuss the complexity of the third problem.

#### Theorem 2.1: DP1 is NP -complete.

**Proof**: In order to get a "yes-no" answer for DP1, we just need a nondeterministic Turing machine which makes a guess at a set of partitions of schedulable units of computations in S and checks in polynomial time whether that the length of each partition and the number of the partitions in the set satisfy the given bounds, respectively. So, this problem is in NP.

We now show that DP1 is polynomially reducible from Bin-Packing problem. For a finite set  $U = \{u_1, u_2, \dots, u_m\}$  of items, a size  $\sigma(u) \in Z^+$  (where  $Z^+$  represents the positive integers) for each  $u \in U$ , a bin capacity  $C \in Z^+$ , and  $k \in Z^+$ ,  $B = \{U_1, U_2, \dots, U_k, C\}$  is a given instance of bin packing of U such that  $\max_{1 \le i \le k} |U_i| \le C$ , where  $|U_i| = \sum_{u \in U_i} \sigma(u)$ . An instance of DP1 can be trivially con-

structed in polynomial time from the instance of bin packing as follows: Given U =

$\{u_1, u_2, \cdots, u_m\}$ , we construct a set  $S = \{s_1, s_2, \cdots, s_m\}$  of mutually independent schedulable units of computation by replacing each  $u_i \in U$  with a schedulable unit of computation  $s_i$  with a length  $l(s_i) = \sigma(u_i)$  for  $1 \le i \le m$ , and create a (dummy) schedulable unit of computation  $s_{m+1}$  such as  $l(s_{m+1}) = C$ , where C is the bin capacity.

We now need to show that there exists a partitioning  $\{U_1, U_2, \dots, U_k\}$  of Uinto minimum possible k disjoint subsets such that  $\max_{1 \le i \le k} (|U_i|) \le C$  if and only if there exits a partitioning  $\{S_1, S_2, \dots, S_k, S_{k+1}\}$  of  $S \cup \{s_{m+1}\}$  into minimum possible k+1 disjoint subsets such that  $\max_{1 \le i \le k} (|S_i|) \le l(s_{m+1}) = L$ , where  $|S_i| = 1$  $\sum_{s \in S_1} l(s) \text{ and } S_{k+1} = \{s_{m+1}\}. \text{ First, suppose that } \{U_1, U_2, \dots, U_k\} \text{ is a partitioning}$ of U with the minimum possible k such that  $\max_{1 \le i \le k} (|U_i|) \le C$  Since  $l(s_i) = \sigma(u_i)$ for  $1 \le i \le m$  and  $l(s_{m+1}) = C$ ,  $\{s_1, s_2, \dots, s_m, s_{m+1}\}$  can be partitioned into  $\{S_1, \dots, S_m, s_m\}$  $S_2, \dots, S_k, S_{k+1}$  such that  $S_i = \bigcup_i \{s_j\}$  for  $1 \le i \le k$  and  $S_{k+1} = \{s_{m+1}\}$ , where  $U_i = \bigcup_i \{s_j\}$  $\bigcup_{i} \{u_j\}$  and  $l(s_j) = \sigma(u_j)$ , Therefore,  $\{S_1, S_2, \dots, S_{k+1}\}$  is a partitioning of  $S \cup \{u_j\}$  $\{s_{m+1}\}\$  with the minimum possible k such that  $\max_{1 \le i \le k} (|s_i|) \le l(s_{m+1})$ . Conversely, suppose that  $\{S_1, S_2, \dots, S_k, S_{k+1}\}$  is a partitioning with the minimum possible k such that  $\max_{1 \le i \le k+1} (|S_i|) \le L$ . Since all  $s_i$   $(1 \le i \le m)$  are mutually independent, a minimum schedule length L becomes  $\max_{1 \le i \le m+1} (l(s_i)) = C$ . Without loss of generality, let  $S_{k+1} = \{s_{m+1}\}$ . Since  $l(s_i) = \sigma(u_i)$  for  $1 \le i \le m$  and L = C,  $\{u_1, u_2, \dots, u_m\}$  $u_m$ } can be partitioned into  $\{U_1, U_2, \cdots, U_k\}$  such that  $U_i = \bigcup_i \{u_j\}$  for  $1 \le i \le k$ , where  $S_i = \bigcup_j \{s_j\}$  and  $\sigma(u_j) = l(s_j)$ . Therefore,  $\{U_1, U_2, \dots, U_k\}$  is a partition of U with the minimum possible k such that  $\max_{1 \le i \le k} (|U_i|) \le C$ .

## **Theorem 2.2**: DP2 is *NP -complete*.

**Proof**: First, it is trivial to see that this problem is in NP, since we just need a non-deterministic Turing machine, which makes a guess at a set of partitions of

schedulable units of computation in S and checks in polynomial time whether that the length of each partition and the number of the partitions in the set satisfy the given bounds, respectively.

We can easily show the *NP*-completeness of DP2 by showing that DP2 contains as a special case *Precedence Constrained Scheduling* (PCS) which has been known an *NP*-complete problem [ULL75]. To be specific, if we allow only instances of DP2 in which all the schedulable units of computation in *S* happen to have the unit computation time, then we obtain a problem identical to the PCS problem. As a result, DP2 is an *NP*-complete problem.

We now consider a slightly general version of SP2, which allows a nonzero communication time on each edge. Since this is another general case of PCS problem as long as the sum of the communication times does not exceed the unit time, this problem is also *NP* –complete.

Finally, we discuss the complexity of SP3. General Scheduling Problem (GSP) is to identify a schedule which minimizes schedule length of a parallel computation of schedulable units of computation with arbitrary computation times and arbitrary scheduling constraints under the assumption that a variable (but limited) number of identical processors are available. It is well know that GSP is NP-complete in the strong sense [KAR72, KAS84]. Even in the case that each schedulable unit of computation has the unit time, finding the minimum schedule is an NP-compete problem [ULL73, LLO80]. Since SP3 is more general version of GSP, it also appears to be an intractable problem.

#### **CHAPTER 3**

#### THE MODELS FOR MULTIPROCESSOR SCHEDULING

The fundamental idea of our approach is that multiprocessor scheduling is equivalent to mapping of a computation graph onto an architecture graph. In this chapter, we first present the models of computation graph and architecture graph, and we then discuss the conceptual model of a generalized multiprocessor scheduling strategy based on a series of graph mappings.

## 3.1. The Graph Models for Multiprocessor Scheduling

This section presents the models for computation graphs and architecture graphs. Computation graphs are directed and acyclic, while architecture graphs are undirected. The former describe parallel computation structures, and the latter specify multiprocessor computer systems.

The computation graph model described provides a framework within which various classes of parallel computation structures can be represented. A computation graph itself contains all necessary information to define the sequences of events of a modeled computation. This leads to determinism in computation graph execution. The computation graph is also labeled with information necessary for scheduling the graph on a target multiprocessor system. Finally, we consider only static computation graphs.

On the other hand, an architecture graph represents a target multiprocessor computer system onto which a computation graph is to be mapped. There are two types of architecture graphs: virtual architecture graphs (VAG's) and physical architecture graphs (PAG's). A VAG depicts a desirable abstract multiprocessor system for the execution of a computation graph; A PAG depicts a real multiprocessor system on which the computation graph is to be scheduled.

## 3.1.1. The Model for Computation Graphs

Karp and Miller [KAR66] first proposed a computation graph as the graphical model to specify parallelism existing in computations. Browne [BRO86] also proposed a directed graph as a representation basis of a parallel computation, in which the nodes represent the bindings of operations to data and the edges represent dependency relations between schedulable units of computation executed at the nodes.

Our computation graph model is a triple  $(G_c, f_c^{comp}, f_c^{comm})$ , whose first component  $G_c = (N_c, E_c)$  specifies a parallel computation. Computation graph  $G_c$  is a directed acyclic graph and defined as follows:

- (i) A node set  $N_c = \{n_1, n_2, \dots, n_l\};$

- (ii) An edge set  $E_c = \{e_1, e_2, \dots, e_t\}$ , where any given edge  $e_p = (n_i, n_j)$  is directed from node  $n_i$  to node  $n_j$ .

To be specific, graph  $G_c$  defines computation steps by the nodes and sequencing among the steps by the edges. The remaining components provide information necessary for mapping the computation graph onto a target system. The second component  $f_c^{comp}$  is a function which maps each node in  $N_c$  onto a positive integer which is the expected computation time used by the schedulable unit of computation corresponding to the node. The next function  $f_c^{comm}$  maps each edge  $(n_i, n_j)$  in  $E_c$  onto a nonnegative integer which is the expected amount of interprocessor communication from node  $n_i$  to node  $n_j$ . For example, if  $f_c^{comm}(e_p) = N_{bytes}$  for  $e_p = (n_i, n_j)$ , then the total length of messages sent from node  $n_i$  to node  $n_j$  is  $N_{bytes}$  bytes. We denote  $n_i < n_j$  if  $f_c^{comm}(e_p) \neq 0$  where  $e_p = (n_i, n_j)$ . We call  $n_i$  and  $n_j$  a source node and a destination node, respectively.

In general, a computation can be specified in terms of schedulable units of computation which may be realized as arithmetic expressions, arbitrary collections of statements or procedures in a higher-level programming language such as Fortran, ADA or Pascal, and in terms of dependency relations between these schedulable units. The amount of computation at any node represents the granularity of a

computation graph which, in turn, determines the structure of the graph. Note that since each schedulable unit of computation is assigned to a unique node we will use the terms node, task and schedulable unit of computation interchangeably.

In order to implement a meaningful computation, units of computation should be executed in some coordinated order. Sequencing establishes the ordering relationships between primitive units of computation to form schedulable units and between schedulable units of computation to form parallel computation graphs [BRO86]. In our model, sequencing inside a schedulable unit of computation is of any form. For example, it may be nondeterministic, and even back edges may be embedded. On the other hand, sequencing between schedulable units of computation is fixed and deterministic. Furthermore, each schedulable unit of computation is not allowed to be embedded in any do-loops. This can be achieved by unrolling every do-loop existing in a computation graph. In this case, we need to adjust the computation and communication times of the unrolled nodes and edges accordingly.

An edge is an abstract representation of a dependency relation between schedulable units of computation; synchronization and communication are realizations of such dependency relations. A directed edge between a pair of nodes not only represents the transfer of information but also carries the sequencing information between the nodes. In our model, however, sequencing is assumed to be subsumed by communication primitives as in a data flow model of computation.

communication Interprocessor based the asynchronous is on send/synchronous-receive communication model. Whenever needed, a node may send messages to its destination nodes in the order specified by its outgoing edges. A send primitive will not be blocked whether its destination node actually receives the messages or not. Each time a node sends a message to another node, the message is assumed to be placed in a queue on the edge between the two nodes. On the other hand, when a node requests a message from the other node, it is blocked from further execution until the message actually arrives at the appropriate input channel. The node also expects input messages to arrive in the order specified by its incoming edges.

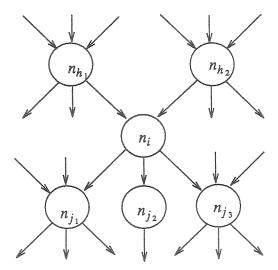

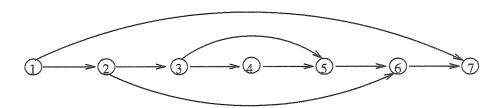

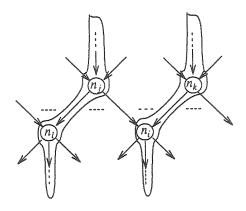

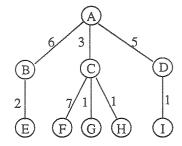

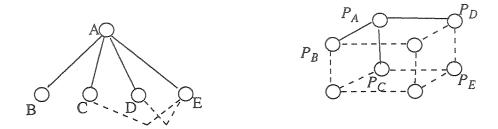

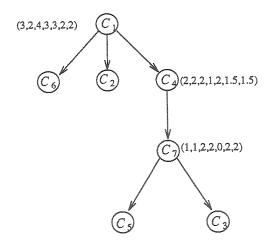

As alluded to in the preceding paragraph, our graph model provides more flexible interpretation of dependency relationships than the precedence graph model. For two nodes  $n_i$  and  $n_j$  in a precedence graph, if  $n_i < n_j$ ,  $n_j$  can not begin until  $n_i$  has been completed. On the other hand, in our model, once  $n_i$  sends a message requested by  $n_j$  and has no outstanding requests for messages from the other source nodes,  $n_j$  may begin execution. For example, node  $n_i$  in the computation (sub)graph shown in Fig. 3-1 functions as follows. Upon being assigned to a processor, a schedulable unit of computation represented by  $n_i$  may be triggered and be executed until it needs a message from its first input message from  $n_{h_1}$ . As soon as it receives the requested message, it immediately resumes its execution (whether or not  $n_{h_1}$  has been completed) until it runs into the next receive primitive from  $n_{h_2}$ . The input edges may be also considered as synchronization points during execution of node  $n_i$ . The output edges from  $n_i$  to  $n_{j_1}$ ,  $n_{j_2}$ , and  $n_{j_3}$  simply specify the fact that there are three send primitives from  $n_i$  in the order of the outgoing edges.

Figure 3-1 A Subgraph of Computation Graph

The exact order of communication primitives (i.e., the *send* and *receive*) issued by a node can not be determined uniquely from a computation graph. As a matter of fact, a given graph may have many feasible orders. More specifically, when a node receives messages from more than one direct ancestor, it expects the messages to arrive in the relative order of its incoming edges (i.e., from left to right). Similarly, when the node sends messages to more than one direct descendant, it sends the messages in the relative order of the outgoing edges (again, from left to right). Any interleaving of the *send/receive* primitives for a node may be regarded as correct as long as the relative orders within the *send* and *receive* primitives are maintained. For example, any number of the *send* primitives may precede any number of *receive* primitives. Table 3-1 shows examples of the *send/receive* orderings which may and may not be represented by node  $n_i$  and by its two incoming and three outgoing edges shown in Fig. 3-1. Note that the *send* and *receive* primitives are defined as follows:

- $send(n_i, message)$   $send a message to node <math>n_i$ ;

- $receive(n_h, message)$   $receive a message from node <math>n_h$ .

The incorrect order in Table 3-1 can not be an issue order specified by node  $n_j$ , since it fails to maintain the relative order between the *receive* primitives of node  $n_i$ . If only  $receive(n_{h_1}, message)$  precedes  $receive(n_{h_2}, message)$ , the order becomes one of 10 correct orders represented by Fig. 3-1.

| A Correct Order             | An Incorrect Order                 |

|-----------------------------|------------------------------------|

| $receive(n_{h_1}, message)$ | $receive(n_{h_2}, message)$        |

| $send(n_{j_1}, message)$    | $send(n_{j_1}, message)$           |

| $send(n_{j_2}, message)$    | send (n <sub>j 2</sub> , message ) |

| $receive(n_{h_2}, message)$ | $receive(n_{h_1}, message)$        |

| $send(n_{j_3}, message)$    | $send(n_{j_3}, message)$           |

Table 3-1 Correct/Incorrect Orderings of Communication Primitives

Our computation graph is a restricted model in several ways, some of which have been briefly mentioned above. The critical restriction that makes the model inappropriate for representing some computations is that sets of edges entering and leaving a given node may not be joined by or conditions. This prevents us from embedding nondeterminism inside computation graphs. A second restriction is that computation graphs may not have any back edges. This forces us to unroll all the existing cycles so that computation graphs become cycle-free. Also, an edge represents one-way communication channel from one node to the other. That is, it is directed and associated with exactly two nodes, and, as such, there exists exactly one unidirectional channel between a pair of communicating nodes (if any). Finally, computation graphs are required to be static; neither new nodes nor new edges can be created during runtime. The main reason for these restrictions is to avoid ambiguity in determining the computation and communication requirements of the nodes and edges in a computation graph. It should be also mentioned here that we assume that a computation graph has one root node and one terminal node without loss of generality.

Some of the restrictions may be relaxed with a little difficulty. For example, the first restriction can be lifted if we enhance algorithm *LinearCluster* (cf. Section 4.1.1.) so that it is able to take into account dynamic information to select paths with the highest probabilities of execution as trace scheduling [FIS84]. From a practical point of view, it may not be always feasible to unroll every do-loop. We discuss how to avoid full expansion of do-loops by removing back edges in some special cases in Section 4.4.

The differences in parallel programming methodologies can be isolated to specifying dependency relations between schedulable units of computation. These methodologies differ mainly in their interprocess communication mechanisms and in the amount of internal parallelism allowed inside a schedulable unit of computation. The dependency relations may be resolved to message or shared memory synchronization operations depending on target multiprocessor systems. In spite of some restrictions, our model can represent a variety of communication model for parallel processing like the message-based communication model (e.g., Hoare's CSP model and ADA's rendezvous model), the shared-memory model and the data

flow model among others, if their nondeterminism may be ignored. To be specific, both CSP and rendezvous models establish precedence constraints by suspending either source or destination nodes until the other also executes the corresponding send/receive primitives. Our model may establish this kind of communication mode by blocking the sender until a message from the sender has been actually received by the receiver. Communication paradigms based on shared-memory allow communicating nodes to exchange messages through shared variables. A dependency relationship in the shared-memory model is nothing but a synchronization constraint that must be met in order to produce the correct results. Edges in our computation graph model, in fact, specify such synchronization constraints. A static, data-driven data flow model is also a special case of our model. It can be implemented by not triggering (or firing) the execution of a node until all the necessary messages have been received. Finally, it should be mentioned here that even though the model of communication allows sending of messages during execution, the algorithms for linear clustering treat computation graphs as pure precedence graphs for easy identification of linear clusters, where the messages are sent only at the completion of each node.

## 3.1.2. The Model for Architecture Graphs

The model for architecture graphs provides a representation basis for the structural description of multiprocessor systems. There are three types of resources which are currently considered: processor, communication link and memory. An architecture graph is an undirected graph in that each architecture edge is bidirectional. It is also assumed that an architecture graph is static; the resource configuration of a physical multiprocessor system will not be changed dynamically during runtime. Moreover, it maintains the exact current status of the system. The status includes the information on which processors are currently active/inactive, which communication links are currently available and what is the current memory capacity available in each processor.

Our architecture graph model is also a triple  $(G_a, f_a^{comp}, f_a^{comm})$ , whose first component  $G_a = (N_a, E_a)$  is an undirected graph defined as follows:

- (i) An architecture node set  $N_a = \{an_1, an_2, \dots, an_l\}$ ;

- (ii) An architecture edge set  $E_a = \{ae_1, ae_2, \cdots, ae_t\}$ , where any architecture edge  $ae_p = (an_i, an_j)$  is undirected.

In an architecture graph, an architecture node represents a processor as well as a memory module, and an architecture edge represents a communication link between two processors. The second component  $f_a^{comp}$  is a function which maps each architecture node in  $N_a$  onto a pair of positive integers which denote the level of computing power of a processor relative to the others in the system and the current local memory size. A common global memory may be specified by a dummy architecture node which is fully-connected with the other architecture nodes. The next function  $f_a^{comm}$  maps an architecture edge  $(an_i, an_j)$  in  $E_a$  onto a positive integer which represents the bandwidth of communication link from architecture node  $an_i$  to architecture node  $an_j$  and vice versa.

There are two types of architecture graphs: virtual architecture graphs (VAG's) and physical architecture graphs (PAG's). A VAG is an architecture graph which defines a desirable abstract multiprocessor system for the execution of a computation graph, regardless of the operational characteristics of the corresponding real multiprocessor system. A PAG is another type of architecture graph corresponding to a real target multiprocessor system on which the computation graph is to be executed.

It is the most desirable for a parallel computation structure if a multiprocessor system is available which has a sufficient number of processors with an unlimited amount of memory and enough communication links so that every schedulable unit of computation can be assigned to a separate processor, and the adjacency between schedulable units of computation can be maintained after the mapping. In fact, it is a goal of silicon compiler research to implement directly such abstract architectures on VLSI chips. While it may be possible to reach this goal, it would not be always feasible to pursue it for every computation graph. A virtual architecture graph representation provides a basis for specifying such an abstract multiprocessor system which is expected to be the best for a given computation graph in terms of performance. Depending on the information available on the target system in the

course of a series of mapping, a VAG may be transformed into another VAG.

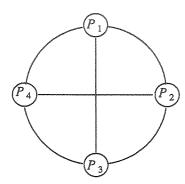

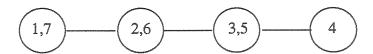

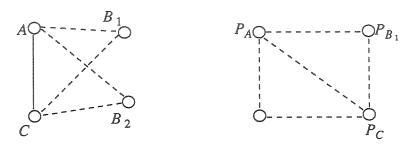

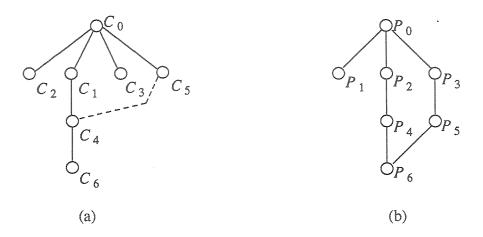

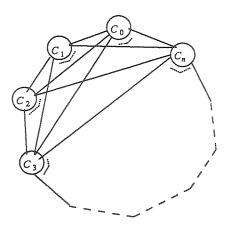

Figure 3-2 Physical Architecture Graph for the Butterfly System with 4 Processors

A physical architecture graph represents an operational view of the actual resource configuration of a multiprocessor system. It may or may not be exactly the same as the real resource configuration of a multiprocessor system. Fig. 3-2 depicts a physical architecture graph for the Butterfly system with four processors. In fact, the *PAG* does not depict exactly the Butterfly system which utilizes the Butterfly switch. The exact representation of physical resources is in fact not important for the scheduling itself as long as those two have the same operational behavior. For example, although the Butterfly switch does not provide dedicated paths between each pair of processor nodes, there is a path through the packet switching network from each processor node to other nodes. That is, the Butterfly switch operates as if there were fully-connected direct communication links between processors. The *PAG* in Fig. 3-2 describes such an operational behavior of the Butterfly system.

## 3.2. The Conceptual Model for Generalized Multiprocessor Scheduling

This section introduces the model for generalized multiprocessor scheduling and the mapping strategies based on this model. Also explained are logical and physical mappings and their differences.

#### 3.2.1. Generalized Multiprocessor Scheduling Model

We mentioned in Section 2.1 that the degree of automation of the mappings and bindings is determined by the level of visibility of a multiprocessor system exposed to the user. In this section, we introduce a model for generalized multiprocessor scheduling based on the level of visibility.

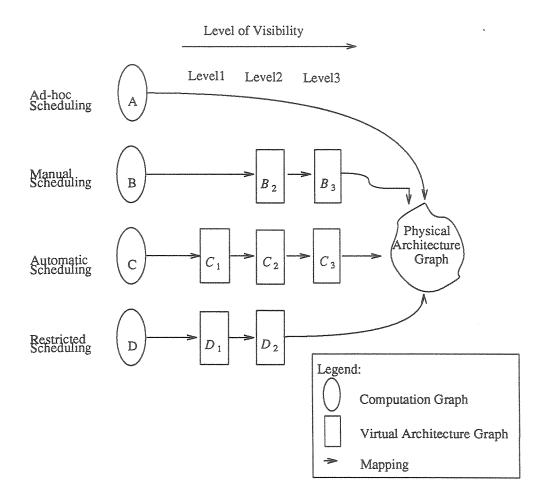

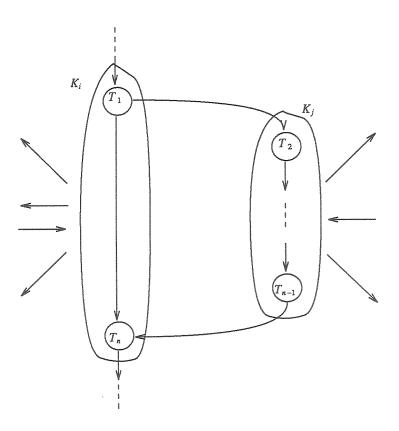

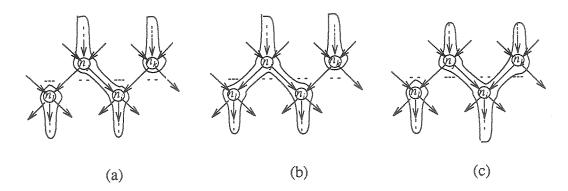

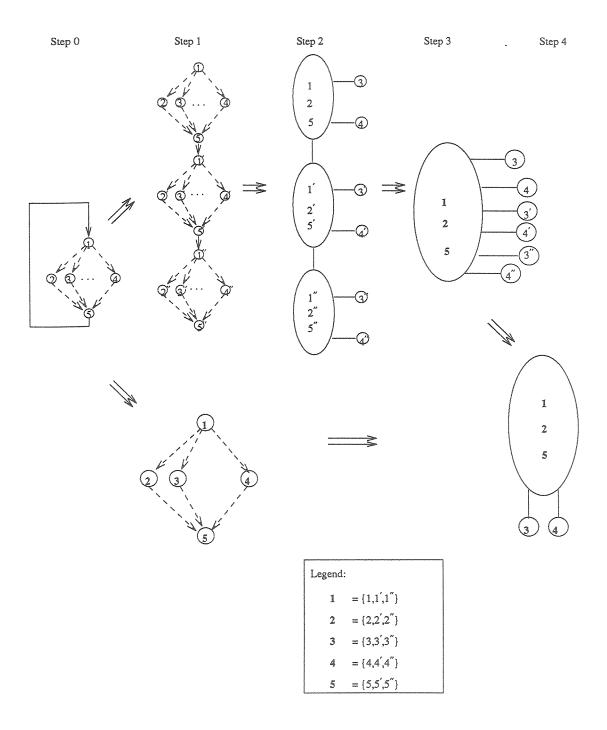

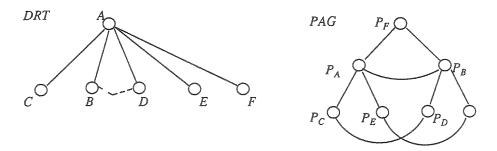

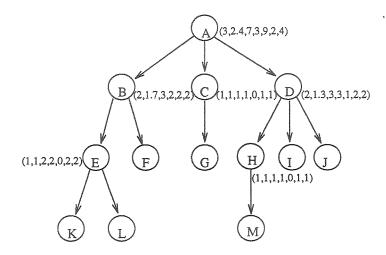

Various scheduling strategies (from ad-hoc to restricted) can be accomplished by utilizing virtual architecture graphs and the mappings between them. A VAG is mapped onto another VAG which represents the physical resource configuration of a multiprocessor system more accurately or gives more detailed resolution of the physical architecture. Given n levels of visibility, assume that a VAG graph at level 1 represents a multiprocessor system whose physical resource configuration is not visible to the user at all. Since nothing related to physical resources is visible, it is reasonable to assume that the VAG at level 1 represents a multiprocessor system with unlimited amounts of resources. Virtual architecture graphs at intermediate levels represent multiprocessor systems whose configurations are partially visible. At the other end, a VAG at the level n represents a multiprocessor system whose configuration is completely visible to the user. Fig. 3-3 describes the conceptual model of scheduling strategies for multiprocessor systems. Assumed here are three levels of visibility among VAG's. It makes it easy to illustrate the basic principles of our model; however, there is no reason to limit the number of levels of visibility.

A physical architecture graph represents a real multiprocessor system. Moreover, it maintains the exact current status of the system. The status includes the information on which processors are currently active/inactive, which communication links are currently available, the current workload of each processor and each communication link, the size of each memory module currently in use (conversely, not in use), and others. A VAG at level n and a PAG are common in that both of them represent a real multiprocessor system. While the former maintains a status of resources which is not necessarily up-to-date, the latter keeps the most up-to-date status of all the resources in the system.

Figure 3-3 Conceptual Model of Multiprocessor Scheduling Strategies

We now explain how different multiprocessor scheduling strategies can be realized in our model depicted in Fig. 3-3. First, in the case of ad-hoc multiprocessor scheduling, there is no intermediate mapping between computation graph A and the PAG; the computation graph can be directly mapped onto the PAG. This implies that the characteristics of physical resources are completely exposed to the user. Therefore, he can take advantage of this visibility to get the maximum performance out of the system. The operations to manipulate all processors in the system may be specified at every single time step. As a result, the user is left with the entire burden of deriving a schedule by which all data dependency constraints are

satisfied. The approach taken by systolic arrays [KUN82] is an example of this kind of model.