## Address Translation and Storage Management for Persistent Object Stores

$\mathbf{b}\mathbf{y}$

Sheetal Vinod Kakkad, B.E., M.S.C.S.

## Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

## **Doctor of Philosophy**

## The University of Texas at Austin

December 1997

Copyright

by

Sheetal Vinod Kakkad

1997

## Address Translation and Storage Management for Persistent Object Stores

Approved by Dissertation Committee:

To my wife Raji, for always being there when it mattered the most

## Acknowledgments

Getting a Ph.D. is incredibly hard, and I could not have done it without the help and support of many people. First and foremost, I would like to thank my advisor, Paul Wilson, who originally encouraged me to transfer from the master's program to the doctoral program. Over the last six years, I have learned many lessons—both academic and otherwise—from Paul as he helped me steer towards the right problems and issues. I would also like to thank all the members of my dissertation committee, particularly Don Batory, who has always been a source of constant encouragement and has helped with remmoving many administrative obstacles in my life as a graduate student.

I would like to thank the past and present members of OOPS research group, in particular Mark Johnstone and Scott Kaplan, who have directly or indirectly contributed to the work presented in this dissertation. I have also been fortunate to have Vivek Singhal and Jeff Thomas as close friends who have helped me in many different ways, including providing moral support when everything seemed too hard.

Over the years, several staff members in the Department of Computer Sciences have made life easier for me. In particular, Fletcher Mattox, the best systems administrator I have known, who has more than once gone out of his way to help me resolve the problem at hand so that I could continue making progress, and Gloria Ramirez, the most helpful and friendly graduate secretary that any lost student could ask for—thank you both for everything that you have done.

A special acknowledgment goes to Motorola for the financial support over the last year, and especially to my colleagues at the Somerset Design Center in Austin for being very understanding and patient with me as dissertation requirements conflicted with my work duties at times.

To my parents and in-laws, to my brother Darpan, and to Mona, Neela, Lakshmi and Bala—thank you for the trust and faith in my abilities, and for not giving up on me. I am deeply grateful to Geri for the love and positive energy that she showed, even when everything seemed so hard—thanks from the bottom of my heart! Thanks also to all my friends, particularly Sanjay and Rema, Aarthi, and Dave and Maria, for supporting my ambitions and always believing that I could achieve my goals. Finally, I owe an immense debt of gratitude to Raji, my wife and my best friend, for her unfledgling love and support over the last few years. She has put up with all my erratic and seemingly-crazy behavior, and has always been there when I needed a friendly shoulder or a warm hug. This dissertation would not have been possible without her efforts, and I dedicate it to her for the courage and calmness that she has shown through the years.

Sheetal Vinod Kakkad

The University of Texas at Austin December 1997

## Address Translation and Storage Management for Persistent Object Stores

Publication No. \_\_\_\_\_

Sheetal Vinod Kakkad, Ph.D. The University of Texas at Austin, 1997

Supervisor: Paul R. Wilson

A common problem in software engineering is efficiently saving the state of application data structures to non-volatile storage between program executions. If this is accomplished using normal file systems, the programmer is forced to explicitly save the data to files as a stream of uninterpreted bytes, thereby losing both pointer semantics and object identity. A better approach is to use *persistent object storage*, a natural extension to virtual memory that allows heap data to be saved automatically to disk while maintaining the topology of data structures without any explicit programmer intervention.

If persistent object stores are to replace the functionality of normal file systems, they must be able to address large volumes of data efficiently on standard hardware. High-performance address translation techniques are necessary and important for supporting large address spaces on stock hardware. We present *pointer swizzling at page fault time* (PS@PFT), a coarse-grained address translation scheme suitable for this purpose, and demonstrate it by building a persistent storage system for C++ called the Texas Persistent Store. We also discuss alternative approaches for portably incorporating fine-grained address translation in Texas for situations where coarse-grained swizzling alone is insufficient. As part of the performance results, we present a detailed analysis of various components of a coarse-grained address translation technique, including a comparison with overall I/O costs.

Pointer swizzling requires run-time knowledge of in-memory object layouts to locate pointers in objects. We have developed and implemented *Run-Time Type Description* (RTTD) for this purpose; our implementation strategy is portable because it is based on a novel use of compiler-generated debugging information for extracting the necessary type description. RTTD is also useful for other applications such as data structure browsing, and advanced profiling and tracing. Another part of this research is a study of the interaction between systems similar to PS@PFT and operating systems, particularly regarding virtual memory management issues. We suggest areas where operating system implementations can be made more open to improve their performance and extensibility. Finally, we briefly discuss storage management issues, specifically *log-structured storage*, *disk prefetching*, and *compressed in-memory storage*, and provide directions for future research in this area.

# Contents

| Ackno   | wledgr       | nents                                  | v   |

|---------|--------------|----------------------------------------|-----|

| Abstra  | ct           |                                        | vii |

| List of | <b>Table</b> | s                                      | xiv |

| List of | Figur        | es                                     | xv  |

| Chapte  | er 1 I       | Introduction                           | 1   |

| 1.1     | Scope        | of the Dissertation                    | 2   |

|         | 1.1.1        | Our Thesis                             | 3   |

|         | 1.1.2        | Motivation                             | 3   |

|         | 1.1.3        | Cost of Orthogonal Persistence         | 4   |

|         | 1.1.4        | Overview                               | 4   |

|         | 1.1.5        | Contributions                          | 5   |

| 1.2     | Advar        | nced Issues                            | 8   |

| 1.3     | Organ        | nization of the Dissertation           | 8   |

| Chapte  | er 2 I       | Design Issues for Persistence          | 11  |

| 2.1     | Introd       | luction                                | 11  |

| 2.2     | Backg        | ground                                 | 11  |

|         | 2.2.1        | Persistence                            | 12  |

|         | 2.2.2        | Types of Persistence                   | 12  |

|         | 2.2.3        | Our Approach                           | 13  |

| 2.3     | Addre        | ess Translation Taxonomies             | 14  |

|         | 2.3.1        | Eager vs. Lazy Swizzling               | 14  |

|         | 2.3.2        | Node Marking vs. Edge Marking Schemes  | 15  |

|         | 2.3.3        | General Classification for Persistence | 16  |

| 2.4     | Granu        | larity Choices for Persistence         | 17  |

|         | 2.4.1        | Address Translation                    | 17  |

|         | 2.4.2        | Address Mapping                        | 18  |

|         | 2.4.3        | Data Fetching                          | 18  |

|         | 2.4.4        | Data Caching                           | 19  |

|         | 2.4.5        | Checkpointing                          | 19  |

| 2.5     | Fine-g       | grained Address Translation            | 20  |

|    |       | 2.5.1 Basic Costs                                              | 20         |

|----|-------|----------------------------------------------------------------|------------|

|    |       | 2.5.2 Object Replacement                                       | 21         |

|    |       | 2.5.3 Discussion                                               | 22         |

|    | 2.6   | Survey of Related Work                                         | 24         |

|    |       | 2.6.1 Persistent Programming Languages                         | 24         |

|    |       | 2.6.2 External Libraries                                       | 27         |

|    |       | 2.6.3 Other Approaches                                         | 60         |

|    | 2.7   | Conclusions                                                    | 32         |

| Cł | napte | er 3 Pointer Swizzling at Page Fault Time 3                    | 3          |

|    | 3.1   | Introduction                                                   | 33         |

|    | 3.2   | Motivation                                                     | \$4        |

|    | 3.3   | Algorithm Description                                          | 5          |

|    | 3.4   | The Mistaken-Dirty-Pages "Problem"                             | 39         |

|    |       | 3.4.1 What it is                                               | 39         |

|    |       | 3.4.2 Is it a Bug or a Feature?                                | ŧ0         |

|    |       | 3.4.3 Observations $\ldots$ 4                                  | 1          |

|    |       | 3.4.4 Discussion                                               | 12         |

|    | 3.5   | Handling Large Objects                                         | 13         |

|    | 3.6   | Avoiding Address Space Exhaustion                              | <b>1</b> 4 |

|    |       | 3.6.1 Smaller Page Sizes                                       | <b>1</b> 4 |

|    |       | 3.6.2 Address Space Reuse                                      | 15         |

|    |       | 3.6.3 Fine-grained and Mixed-granularity Translation           | 16         |

|    | 3.7   | Sharing and Compatibility                                      | 16         |

|    |       | 3.7.1 Data Formats for Sharing across Machines                 | 17         |

|    |       | 3.7.2 Linking to Existing Code                                 | <u>1</u> 8 |

|    |       | 3.7.3 Interfacing with Languages and Compilers                 | <u>1</u> 8 |

|    | 3.8   | Fine-grained and Mixed-granularity Translation                 | <b>1</b> 9 |

|    |       | 3.8.1 Smart Pointers                                           | <u>1</u> 9 |

|    |       | 3.8.2 Fine-grained Address Translation                         | 0          |

|    |       | 3.8.3 Mixed-granularity Address Translation                    | 52         |

|    | 3.9   | Conclusions                                                    | 53         |

| Cł | napte | er 4 Design and Implementation of the Texas Persistent Store 5 | 64         |

|    | 4.1   |                                                                | 64         |

|    | 4.2   |                                                                | 55         |

|    | 4.3   | Basic Design                                                   | 66         |

|    | 4.4   |                                                                | 57         |

|    |       | 4.4.1 Heap Management                                          | 57         |

|    |       | 1 0                                                            | 50         |

|    |       |                                                                | 51         |

|    |       |                                                                | 51         |

|    |       |                                                                | 52         |

|    |       |                                                                | 52         |

| 4.5    | Conclu  | sions $\ldots \ldots 64$                                  |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapte | er 5 P  | erformance of the Texas Persistent Store 66                                                                                                                 |

| 5.1    | Introdu | action                                                                                                                                                      |

| 5.2    | Experi  | mental Design $\ldots \ldots 67$                   |

|        | 5.2.1   | Benchmarks                                                                                                                                                  |

|        | 5.2.2   | Methodology                                                                                                                                                 |

|        | 5.2.3   | Hardware and Operating Systems                                                                                                                              |

| 5.3    | Instruc | tion-Count Profiling Results                                                                                                                                |

| 5.4    | Perform | nance on Linux                                                                                                                                              |

|        | 5.4.1   | Large Database Results                                                                                                                                      |

|        | 5.4.2   | Small Database Results                                                                                                                                      |

|        | 5.4.3   | Analysis                                                                                                                                                    |

| 5.5    | Perform | nance on Solaris                                                                                                                                            |

|        | 5.5.1   | Large Database Results $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 91$                                                                         |

|        | 5.5.2   | Small Database Results                                                                                                                                      |

|        | 5.5.3   | Large Database Results Using Raw I/O $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ 99$                                                                    |

|        | 5.5.4   | Small Database Results Using Raw I/O $\ $                                                                                                                   |

|        | 5.5.5   | Large Database Results with Bigger Memory Size                                                                                                              |

|        | 5.5.6   | Analysis                                                                                                                                                    |

| 5.6    | Compa   | rison of Address Translation Granularities                                                                                                                  |

| 5.7    | Discuss | sion                                                                                                                                                        |

|        | 5.7.1   | Basic Argument                                                                                                                                              |

|        | 5.7.2   | Impact of Operating System Implementations                                                                                                                  |

|        | 5.7.3   | Indirect Costs of Pointer Swizzling                                                                                                                         |

| 5.8    | Benchr  | narking Limitations                                                                                                                                         |

|        | 5.8.1   | Synthetic Benchmarks $\ldots \ldots \ldots$ |

|        | 5.8.2   | Common Problems with the OO1 and OO7 Benchmarks $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                    |

|        | 5.8.3   | Summary                                                                                                                                                     |

| 5.9    | Conclu  | sions $\ldots \ldots \ldots$                |

| Chapte | er6R    | un-Time Type Description 118                                                                                                                                |

| 6.1    | Introdu | uction                                                                                                                                                      |

| 6.2    | RTTD    | Issues                                                                                                                                                      |

|        | 6.2.1   | Motivation                                                                                                                                                  |

|        | 6.2.2   | RTTD vs. RTTI                                                                                                                                               |

|        | 6.2.3   | Type Descriptor Records                                                                                                                                     |

|        | 6.2.4   | Preprocessors vs. Debugging Information                                                                                                                     |

|        | 6.2.5   | Adapting to Future Compiler Support                                                                                                                         |

| 6.3    | RTTD    | Generation and Manipulation $\ldots$                                                                                                                        |

|        | 6.3.1   | Generating Type Descriptor Records                                                                                                                          |

|        | 6.3.2   | Associating Type Descriptor Records with Objects $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                   |

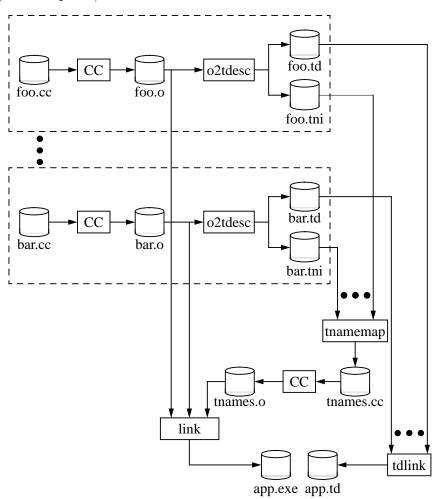

|        | 6.3.3   | Compilation and Linkage Model                                                                                                                               |

|        | 6.3.4   | RTTD Across Multiple Compilation Units $\hdots$                                                                                                             |

| 6.4    | RTTD for C++ $\dots \dots $                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 6.4.1 Overview                                                                                                                                                 |

|        | 6.4.2 Implementation Details                                                                                                                                   |

|        | 6.4.3 Handling Multiple Compilation Units                                                                                                                      |

|        | 6.4.4 Using Type Names for Added Flexibility                                                                                                                   |

|        | 6.4.5 Complications and Enhancements                                                                                                                           |

| 6.5    | Storage Model                                                                                                                                                  |

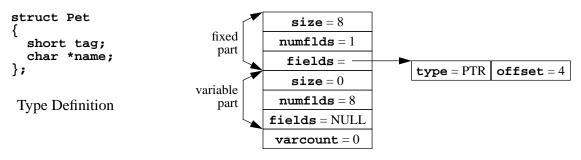

|        | 6.5.1 Hierarchical Format                                                                                                                                      |

|        | 6.5.2 Flat Format                                                                                                                                              |

| 6.6    | Performance Characteristics                                                                                                                                    |

|        | 6.6.1 Compile-Time Costs                                                                                                                                       |

|        | 6.6.2 Run-Time Costs                                                                                                                                           |

|        | 6.6.3 Making Decoding Costs Negligible                                                                                                                         |

| 6.7    | Current Status and Future Work                                                                                                                                 |

| 6.8    | Related Work                                                                                                                                                   |

| 6.9    | Conclusions                                                                                                                                                    |

| Chapte | er 7 Interactions with Operating Systems 151                                                                                                                   |

| 7.1    | Introduction                                                                                                                                                   |

|        | 7.1.1 Background: Virtual Memory                                                                                                                               |

|        | 7.1.2 Basic Terminology $\ldots \ldots \ldots$ |

| 7.2    | Virtual Memory Allocation                                                                                                                                      |

|        | 7.2.1 Storage Space vs. Address Space Allocation                                                                                                               |

|        | 7.2.2 Virtual Memory Primitives                                                                                                                                |

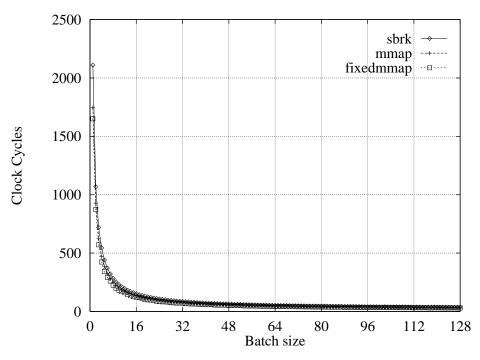

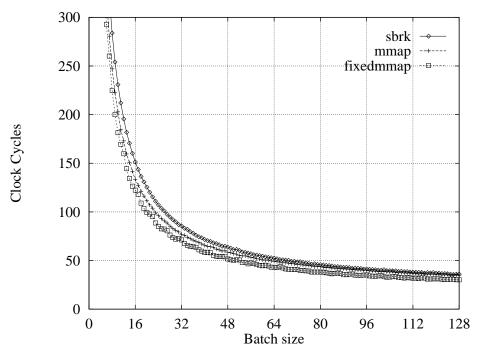

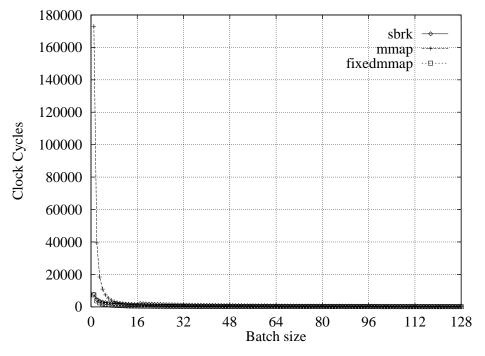

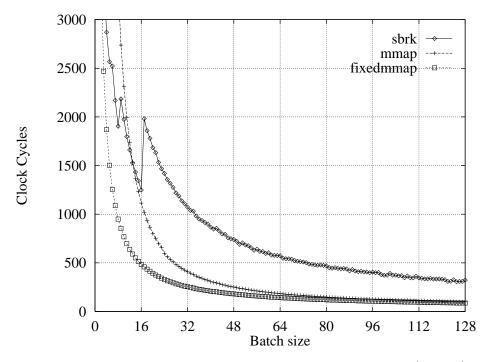

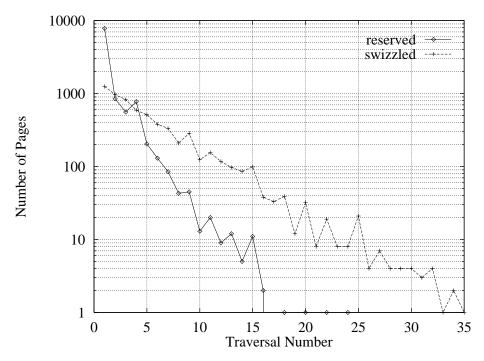

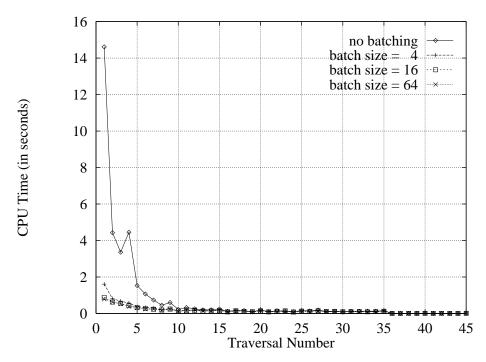

|        | 7.2.3 Performance of Virtual Memory Primitives                                                                                                                 |

| 7.3    | Issues in Swap Space Allocation                                                                                                                                |

|        | 7.3.1 PS@PFT and Swap Space Allocation                                                                                                                         |

|        | 7.3.2 Survey of Existing Implementations                                                                                                                       |

|        | 7.3.3 Discussion                                                                                                                                               |

| 7.4    | Pointer Swizzling and Virtual Memory Management                                                                                                                |

|        | 7.4.1 Control over Memory Management                                                                                                                           |

|        | 7.4.2 Discussion                                                                                                                                               |

| 7.5    | Other Operating System Features                                                                                                                                |

|        | 7.5.1 Exception Handling                                                                                                                                       |

|        | 7.5.2 Virtual Memory Page Size and Sub-page Protections                                                                                                        |

|        | 7.5.3 Support for Raw I/O                                                                                                                                      |

| 7.6    | Conclusions                                                                                                                                                    |

| Chapte | er 8 Future Work 181                                                                                                                                           |

| 8.1    | Introduction                                                                                                                                                   |

| 8.2    | Storage Management                                                                                                                                             |

|        | 8.2.1 Log-structured Storage System                                                                                                                            |

|        | 8.2.2 Adaptive Prefetching                                                                                                                                     |

|        | 8.2.3 Compressed In-memory Storage                                                                                                                             |

| 8.3     | Advanced Issues                     | 185 |

|---------|-------------------------------------|-----|

| Chapte  | er 9 Conclusions                    | 186 |

| 9.1     | Address Translation                 | 186 |

| 9.2     | Granularity Choices for Persistence | 187 |

| 9.3     | Run-Time Type Description           | 187 |

| 9.4     | Operating System Interactions       | 188 |

| 9.5     | Storage Management Issues           | 188 |

| 9.6     | Final Words                         | 189 |

| Appen   | dix A Hierarchical Type Graph       | 190 |

| Bibliog | graphy                              | 193 |

| Vita    |                                     | 203 |

# List of Tables

| 5.1 | Estimated instruction counts                    | 75  |

|-----|-------------------------------------------------|-----|

| 7.1 | Cost of handling an access-protection violation | 177 |

# List of Figures

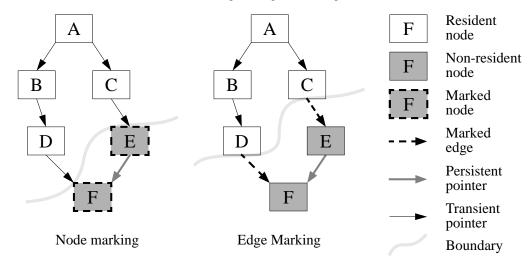

| 2.1  | Node marking and edge marking schemes                                                |

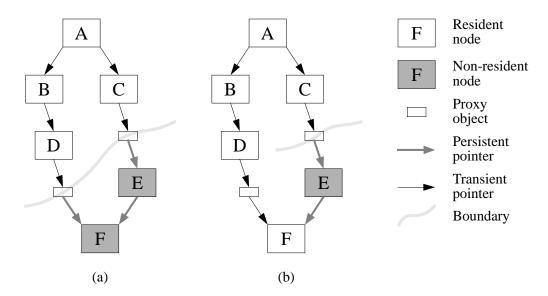

|------|--------------------------------------------------------------------------------------|

| 2.2  | Node marking using proxy objects                                                     |

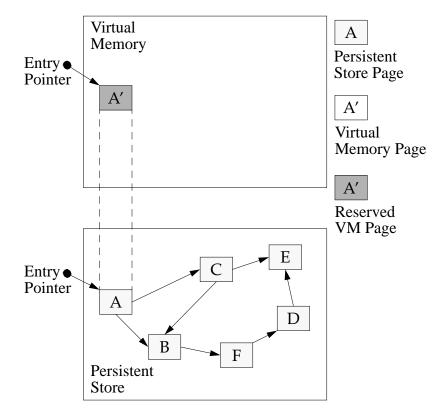

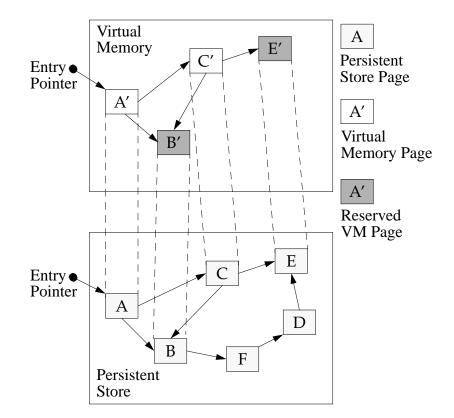

| 3.1  | Bootstrap state for swizzling                                                        |

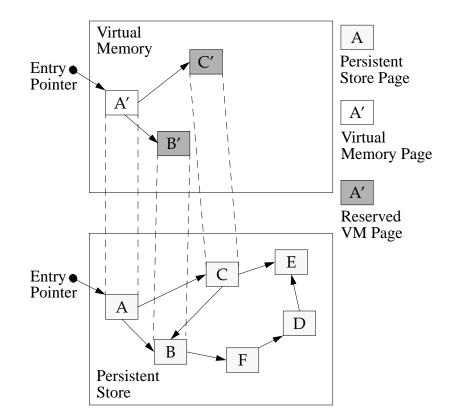

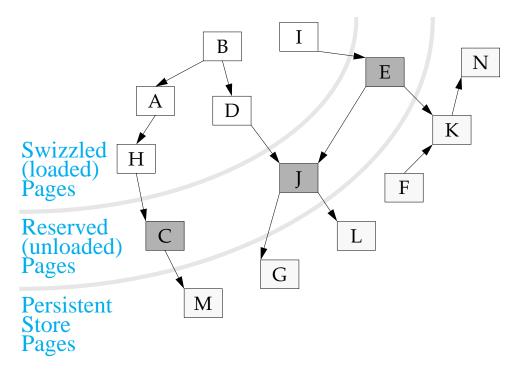

| 3.2  | Incremental faulting and swizzling                                                   |

| 3.3  | Incremental faulting and swizzling (cont'd.)                                         |

| 3.4  | "Wavefront" of address space reservation                                             |

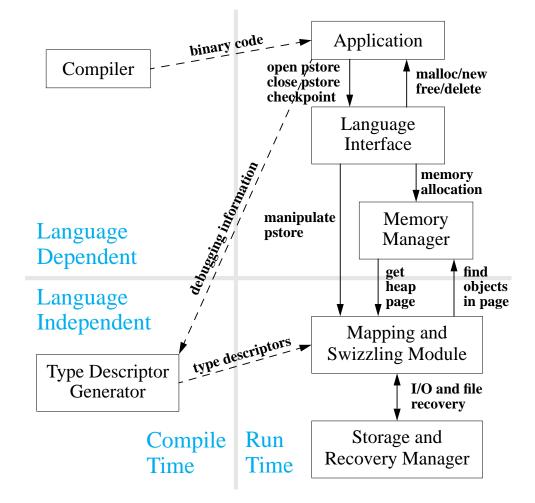

| 4.1  | Basic design of Texas                                                                |

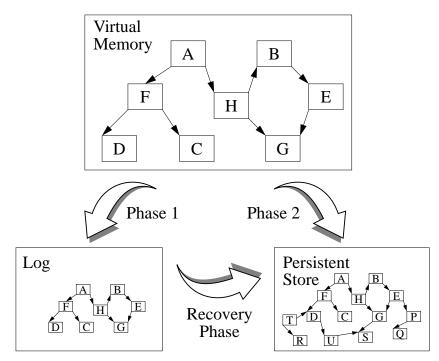

| 4.2  | Logging mechanism                                                                    |

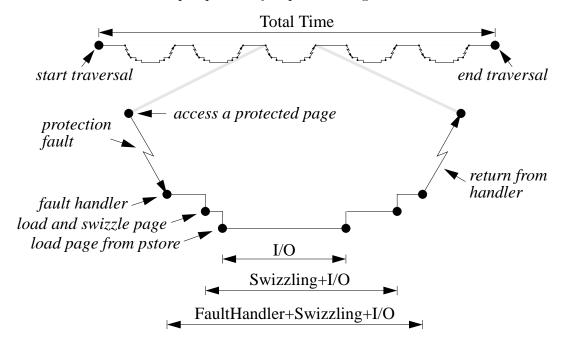

| 5.1  | Timer placements for run-time measurements                                           |

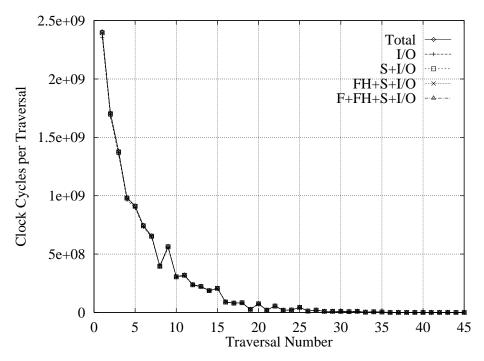

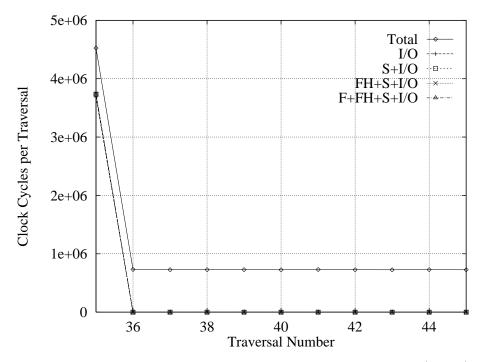

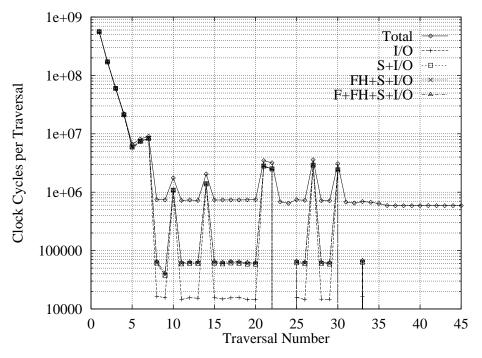

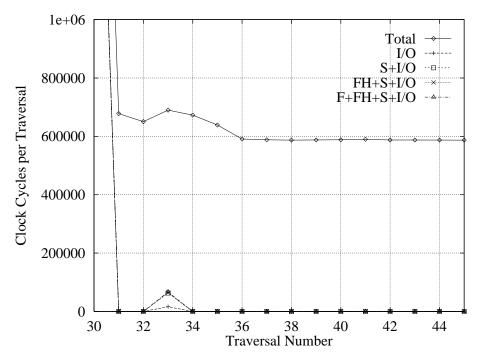

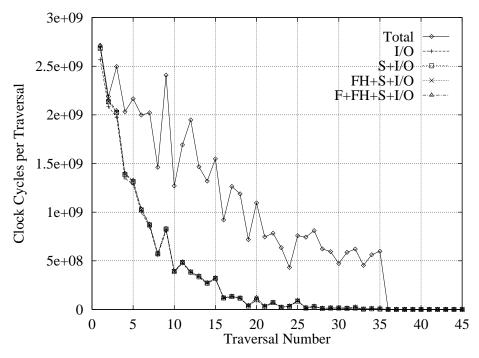

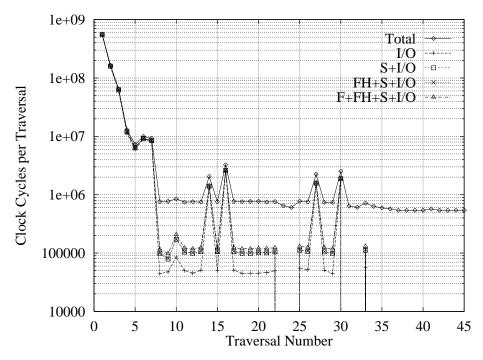

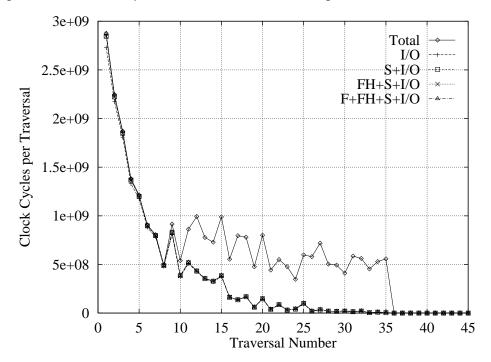

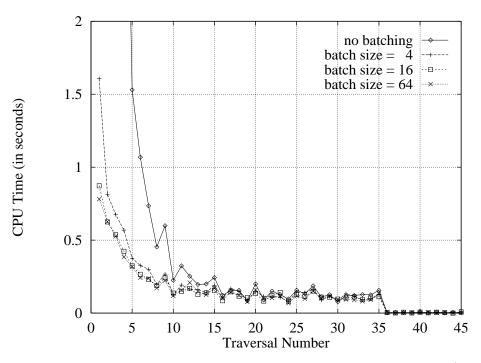

| 5.2  | Times for all traversals, large database (Linux)                                     |

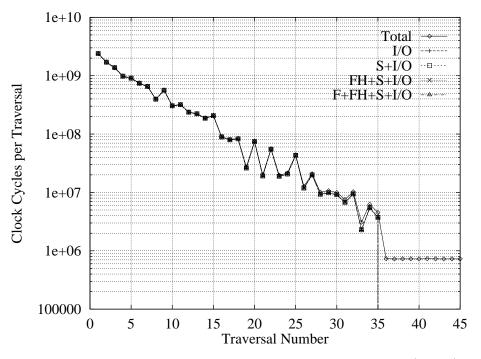

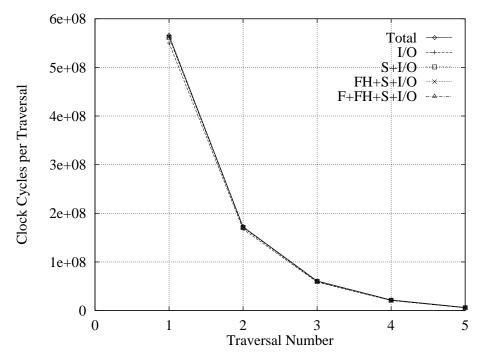

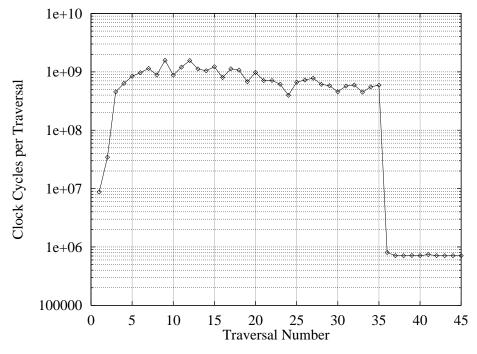

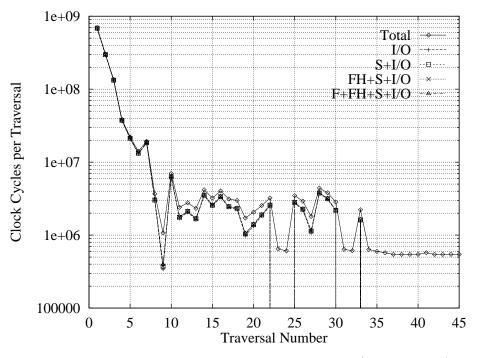

| 5.3  | Times for all traversals, large database, log scale (Linux)                          |

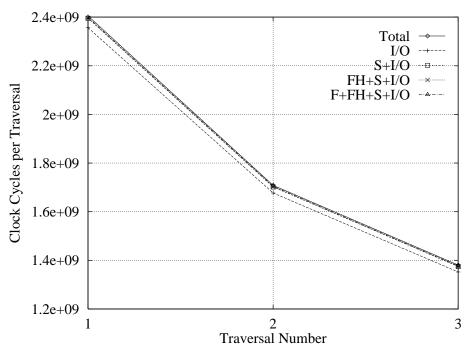

| 5.4  | Times for traversals 1 through 3, large database (Linux)                             |

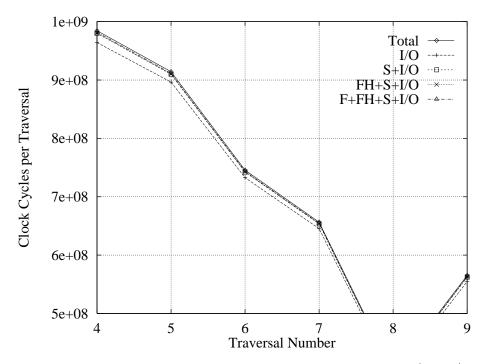

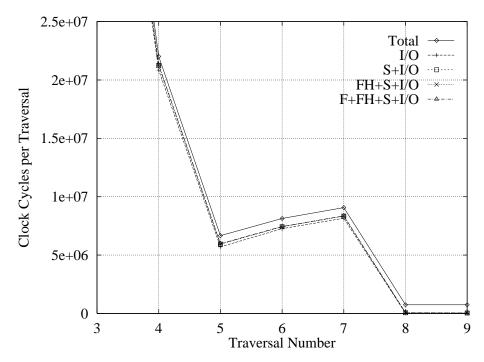

| 5.5  | Times for traversals 4 through 9, large database (Linux)                             |

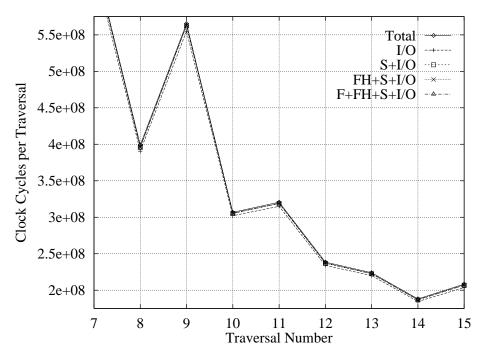

| 5.6  | Times for traversals 7 through 15, large database (Linux) 80                         |

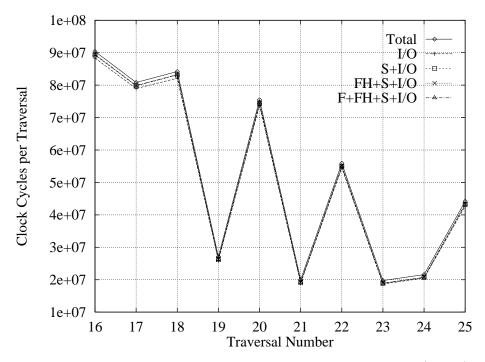

| 5.7  | Times for traversals 16 through 25, large database (Linux) 80                        |

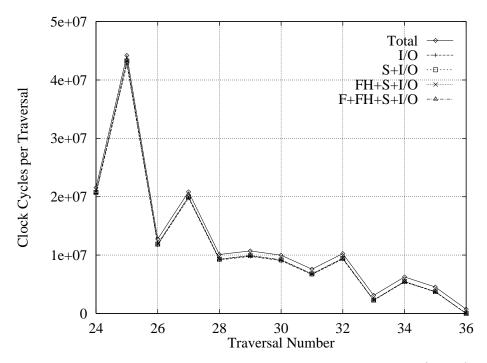

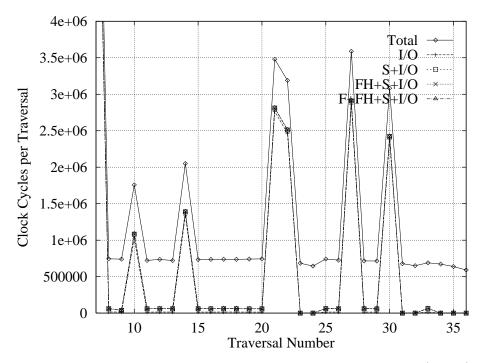

| 5.8  | Times for traversals 24 through 36, large database (Linux)                           |

| 5.9  | Times for traversals 35 through 45, large database (Linux) 81                        |

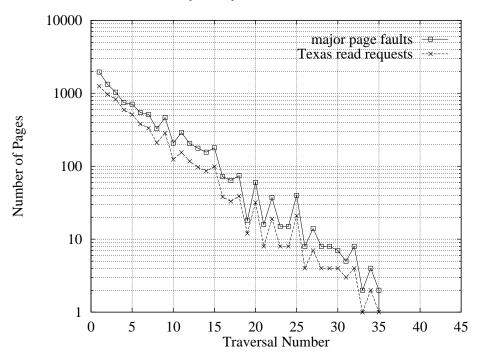

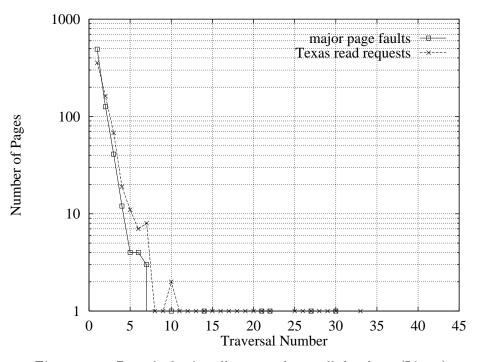

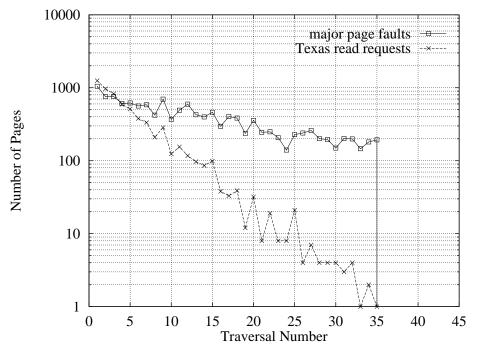

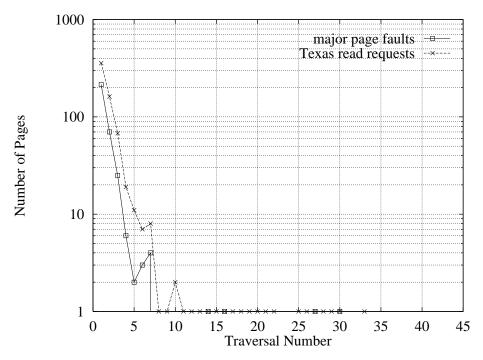

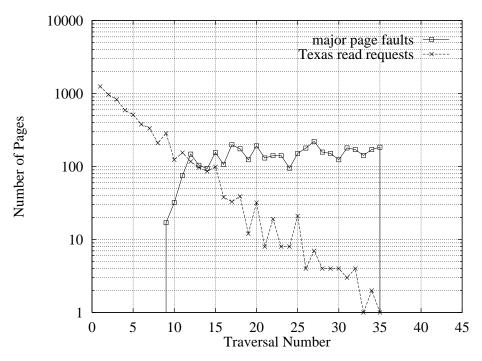

| 5.10 | Page faults for all traversals, large database (Linux)                               |

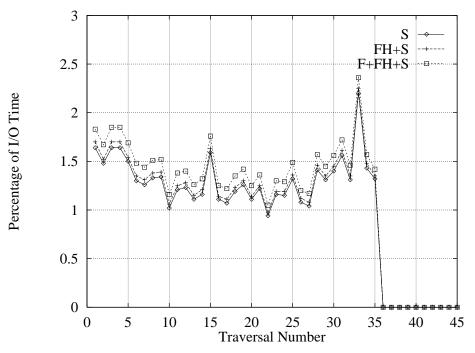

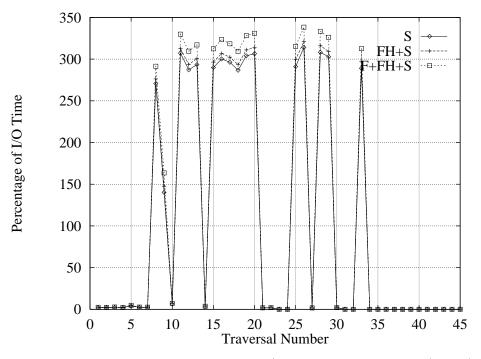

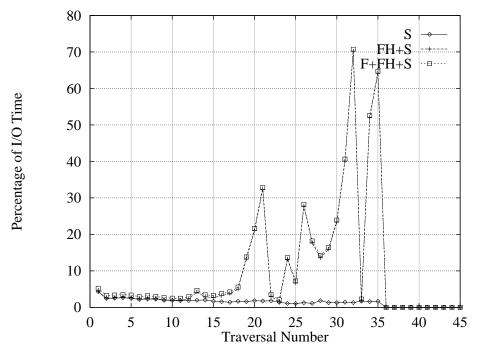

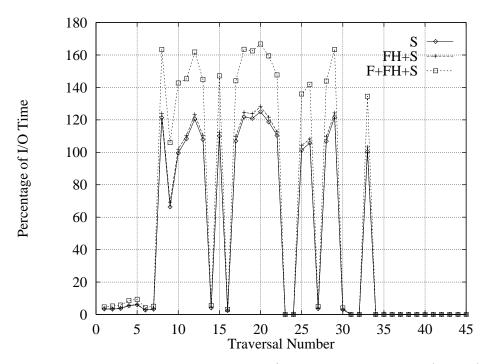

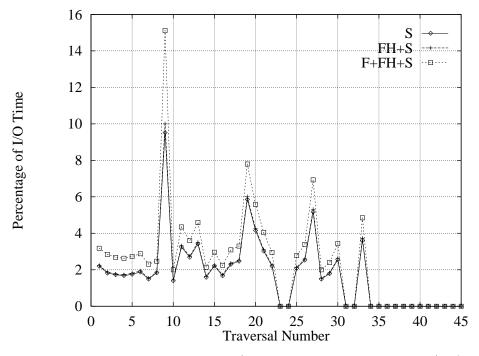

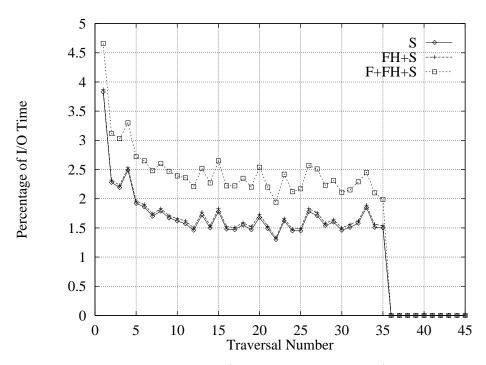

| 5.11 | Overhead as percentage of I/O time, large database (Linux)                           |

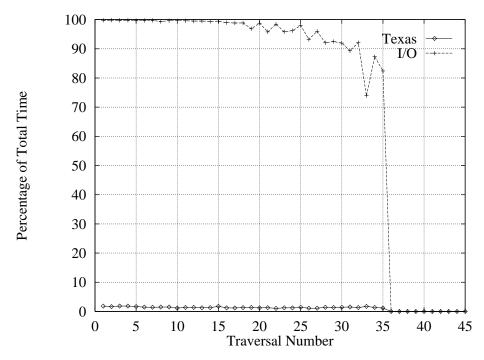

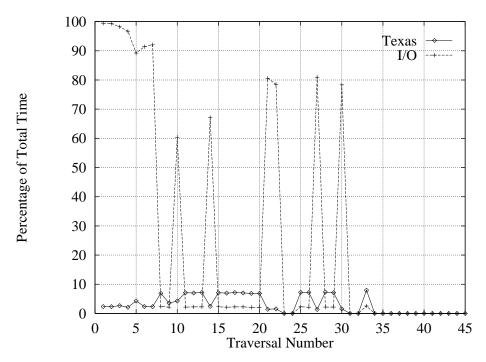

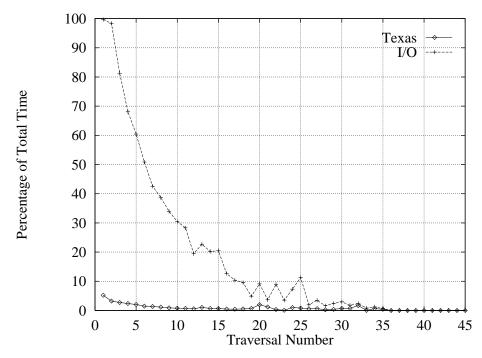

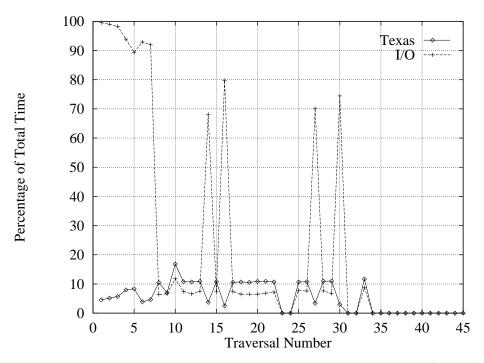

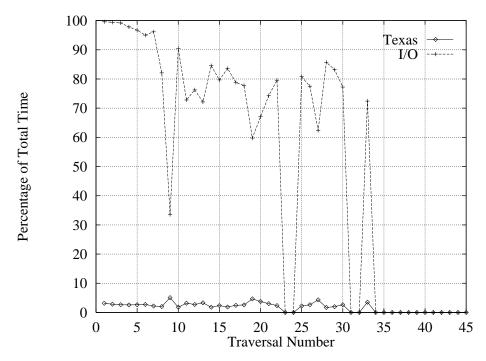

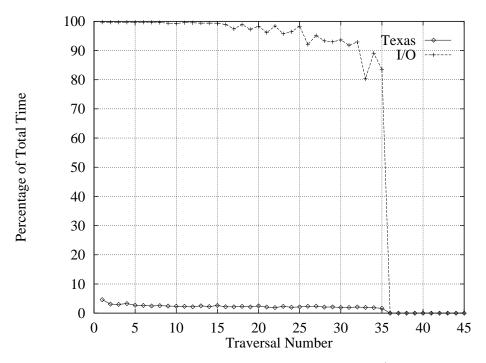

| 5.12 | Overhead as percentage of total time, large database (Linux)                         |

| 5.13 | Times for all traversals, small database, log scale (Linux)                          |

|      | Times for traversals 1 through 5, small database (Linux)                             |

|      | Times for traversals 3 through 9, small database (Linux)                             |

|      | Times for traversals 8 through 36, small database (Linux)                            |

|      | Times for traversals 30 through 45, small database (Linux)                           |

|      | Page faults for all traversals, small database (Linux)                               |

|      | Overhead as percentage of I/O time, small database (Linux) $\ldots \ldots \ldots 89$ |

|      | Overhead as percentage of total time, small database (Linux)                         |

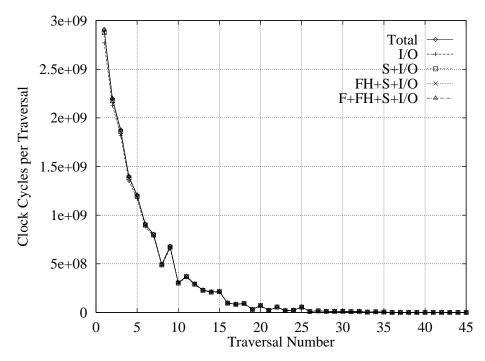

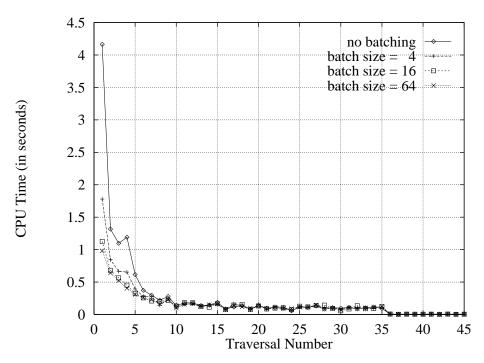

|      | Times for all traversals, large database (Solaris)                                   |

|      | Page faults for all traversals, large database (Solaris)                             |

| 5.23 | Benchmark-only time for all traversals, large database (Solaris)                     |

| 5.24                                             | Overhead as percentage of I/O time, large database (Solaris)                                      |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 5.25                                             | Overhead as percentage of total time, large database (Solaris)                                    |

| 5.26                                             | Times for all traversals, small database, log scale (Solaris)                                     |

| 5.27                                             | Page faults for all traversals, small database (Solaris)                                          |

| 5.28                                             | Overhead as percentage of I/O time, small database (Solaris) $\ldots \ldots \ldots 98$            |

| 5.29                                             | Overhead as percentage of total time, small database (Solaris)                                    |

| 5.30                                             | Times for all traversals, large database, raw I/O (Solaris)                                       |

| 5.31                                             | Page faults for all traversals, large database, raw I/O (Solaris) 100 $$                          |

| 5.32                                             | Benchmark-only time for all traversals, large database, raw I/O (Solaris) $\ . \ . \ . \ 100$     |

| 5.33                                             | Times for all traversals, small database, raw I/O, log scale (Solaris) $\ldots \ldots \ldots 101$ |

| 5.34                                             | Overhead as percentage of I/O time, small database, raw I/O (Solaris) $\ldots$ . 102              |

| 5.35                                             | Overhead as percentage of total time, small database, raw I/O (Solaris) 103 $$                    |

| 5.36                                             | Times for all traversals, large database (Solaris, large memory)                                  |

| 5.37                                             | Overhead as percentage of I/O time, large database (Solaris, large memory) $~$ 105 $$             |

| 5.38                                             | Overhead as percentage of total time, large database (Solaris, large memory) $105$                |

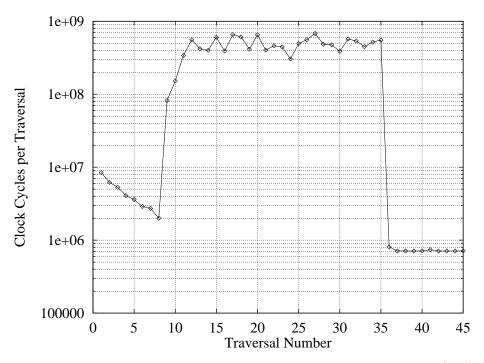

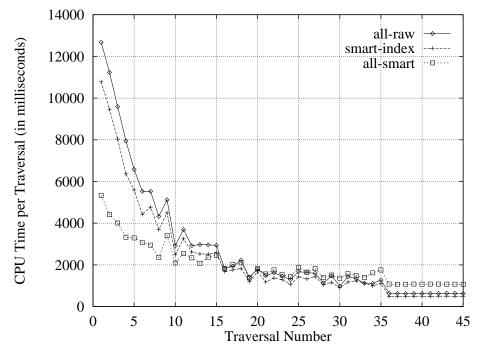

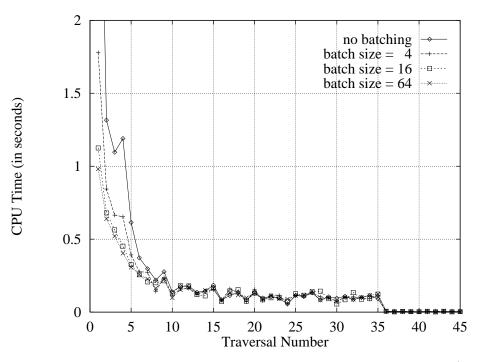

| 5.39                                             | CPU time for translation granularities, large database (Solaris, SPARC ELC) $$ . 108 $$           |

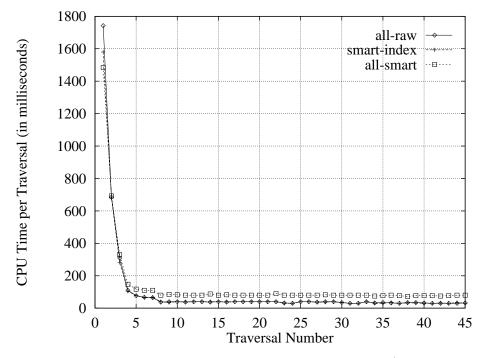

| 5.40                                             | CPU time for translation granularities, small database (Solaris, SPARC ELC) $$ . 109 $$           |

| 6.1                                              | Compilation and linkage process                                                                   |

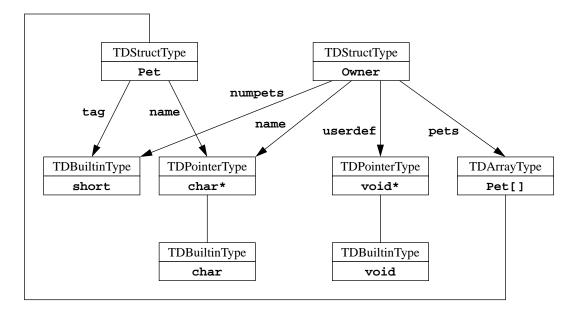

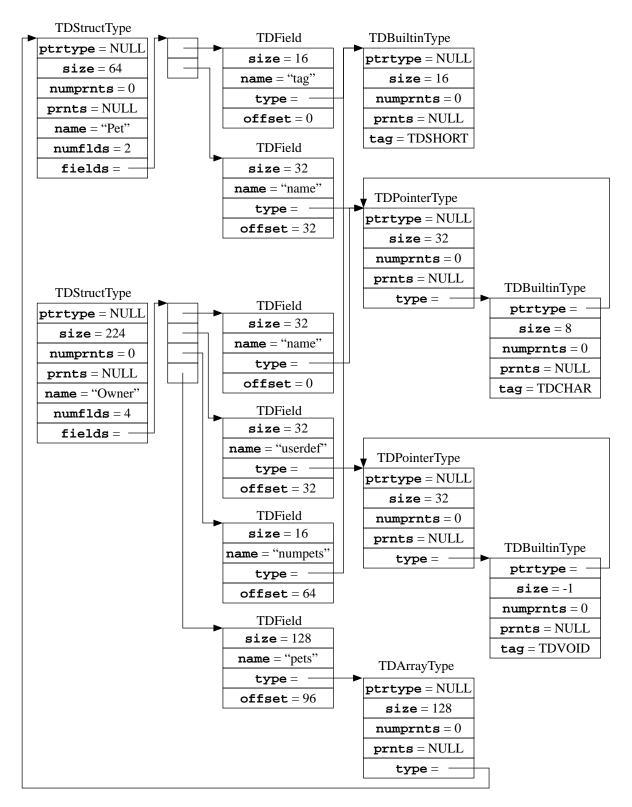

| 6.2                                              | Type graph                                                                                        |

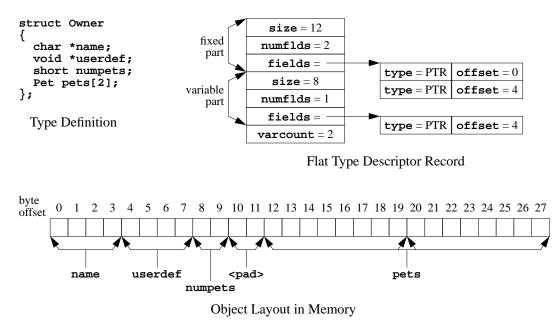

| 6.3                                              | Flat format type descriptor records (simple)                                                      |

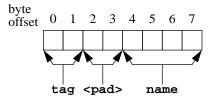

| 6.4                                              | Flat format type descriptor records (complex)                                                     |

| 7.1                                              |                                                                                                   |

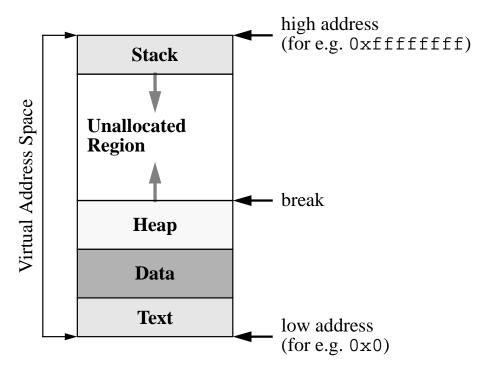

| 1.1                                              | Address space of a process                                                                        |

| 7.2                                              |                                                                                                   |

|                                                  | Address space of a process                                                                        |

| 7.2                                              | Address space of a process                                                                        |

| $7.2 \\ 7.3$                                     | Address space of a process                                                                        |

| $7.2 \\ 7.3 \\ 7.4$                              | Address space of a process                                                                        |

| 7.2<br>7.3<br>7.4<br>7.5                         | Address space of a process                                                                        |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6                  | Address space of a process                                                                        |

| $7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 $        | Address space of a process                                                                        |

| $7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 \\ 7.8 $ | Address space of a process                                                                        |

## Chapter 1

## Introduction

It is often desirable to support a virtual address space that is larger than what can be specified directly by the word size of the available hardware. Applications such as persistent object stores (e.g., [ABC+83a, SKW92, DSZ90, AM92]), operating systems with a single shared address space (e.g., [CLLBH92]), distributed shared memories (e.g., [Li86]), etc. can benefit from large address spaces. For example, persistent object stores provide sharable, recoverable heap storage to eliminate the use of files for most purposes, operating systems with single shared address spaces provide a common addressing model for all processes on one or more machines, and distributed shared memory models provide a single address space for applications that span multiple machines.

All these systems typically emphasize simplified programming by preserving pointer semantics in data structures. In other words, they inherently support the notion of *object identity* by maintaining the programmer's default view of data, which is a heap of objects interconnected by pointers. Object identity is defined as the property by virtue of which an object can be *uniquely* identified among a collection of objects, such that any two object references can be compared to determine whether they identify the same object. By this definition, an object identifier is *never* reused, even after the object is deleted. A detailed study of various forms of object identity is available in [KC86].

It is often necessary to send data from one host to another, or to save application data structures to stable storage so that they can be either operated on later (possibly by other applications) or used for recovering the application state in case of a crash. In systems that do not support large shared address spaces, it is usually necessary to write routines that flatten data structures into a low-level linear bytestream and manually reconstruct them later. In general, this procedure tends to be tedious and error-prone because programmer intervention and coding is required for the appropriate data structure conversions. In addition, the linear representations bypass type systems, lose all pointer semantics and object identity, and leave the burden of maintaining data structure consistency up to the programmer.

Persistent objects have the ability to outlive the execution of the program that creates them; in contrast, transient objects disappear with the termination of the program in which they were created. A persistent object store is a repository for persistent objects; it is typically used to allow programmers to save complex pointer-linked data structures directly and automatically to non-volatile storage, without requiring additional code or further intervention to convert between representations. A persistent object store strongly supports the notion of object identity because all type information, as well as the topology of the data structures, is preserved when objects are saved to stable storage, allowing each object to be uniquely identified.

In this dissertation, we propose and implement a persistent storage mechanism based on a coarse-grained address translation technique that exploits existing virtual memory hardware and operating system facilities to achieve high performance and increased portability. The basic idea is to load (one or more) pages from the persistent storage into memory on demand, and "fix up" (i.e., translate) all persistent pointers into local hardware-supported virtual memory pointers, guaranteeing that a running program will never see any untranslated pointer values. Once the data has been loaded into memory and various pointers have been translated, there is absolutely no overhead for future accesses to that data. Any referents corresponding to newly-translated pointers that are not in memory are marked as such using the operating system's virtual memory protection facilities; any attempt to access protected data will raise an exception that is handled by loading the data from the persistent store and translating pointers as necessary.

An address translation mechanism such as ours has several advantages over other traditional approaches, in terms of both performance and portability. As we will show in later chapters of the dissertation, the performance overhead of our system is *zero* when the application is operating on data that has already been loaded into memory and there is no faulting. For other situations, that is, when new data is being loaded into memory from the persistent store, the overhead of our system is very low, usually between 1 and 5 percent of the overall run time. We will show that this is much smaller than the I/O costs incurred for loading the data into memory. There are also some indirect costs of our approach because of an inadvertent interaction with the underlying virtual memory system; these costs, however, can be avoided by improving the operating system implementations to provide a better memory management interface. Regarding improved portability, our persistent storage system is compatible with standard off-the-shelf compilers and has been ported to a variety of modern operating systems such as SunOS, Solaris, Linux, Mach, Ultrix, OS/2, etc. It should also be relatively easy to port to other modern operating systems such as Windows NT.

## 1.1 Scope of the Dissertation

This dissertation is about high-performance address translation techniques for implementing orthogonal persistence. Orthogonal persistent systems require that any arbitrary object can be made persistent without regard to its type. That is, persistence is a storage class of an object, and is orthogonal to its type. Our basic approach relies on the use of coarse-grained address translation for performance and portability reasons. In order to support this claim, we analyze the various costs of both coarse-grained and fine-grained techniques and present a cost model which shows that page-wise address translation can be implemented efficiently and can achieve good performance on standard hardware.

## 1.1.1 Our Thesis

Address translation is the most important issue that must be considered when implementing orthogonal persistence. Once this has been resolved effectively, all other related issues can be resolved independently without affecting address translation. Our thesis can be stated as follows:

High-performance address translation for orthogonal persistence can be effectively realized through coarse-grained translation schemes. Pointer swizzling at page fault time is one such coarse-grained scheme that can be implemented efficiently on stock hardware by exploiting the existing virtual memory hardware and protection facilities offered by most modern operating systems, without requiring special system privileges.

Since pointer swizzling at page fault time uses only standard capabilities of an operating system, it is easily ported to other modern operating systems which also support the same functionality. The basic approach exploits user-level virtual memory protection facilities to avoid (more expensive) software checks for pointer formats, and works with standard off-the-shelf compilers.

## 1.1.2 Motivation

There are a variety of factors that motivate the need for a flexible and efficient persistence mechanism. Many applications operate on large amounts of data represented using complex data structures. Before such an application terminates execution, the data in volatile memory must be saved to stable storage for future use. A persistent storage system is designed to save and restore data reliably, efficiently and automatically, and is therefore preferable to an *ad hoc* mechanism implemented by the application itself. The underlying persistent object store must be able to support large volumes of data, essentially acting as an eventual replacement for the normal file system.

However, it is important to realize that for most applications, a persistent programming language is still a programming language, and raw speed of computation is usually very important. In fact, orthogonally persistent programming languages (and object-oriented database systems) are largely motivated by a combination of performance and expressiveness considerations relative to traditional database systems. They are intended for use in applications with *rich heap-allocated data structures* and *efficient algorithms* to manipulate those data structures. Where traditional database systems are designed largely to optimize I/O for I/O-intensive applications, persistent programming languages allow programmers to optimize computation for CPU-intensive applications such as CAD tools and simulation programs. Although it is desirable for such programs to be able to transparently traverse pointers through large amounts of disk-resident data, the majority of their execution time is usually spent operating on persistent data previously loaded into memory.

Furthermore, many such applications usually also operate extensively on transient data. Typically, a large majority of these transient objects constitute temporary data that die fairly "young" [Wil97, WJNB95]. Thus the total execution costs in a CPU-intensive application are dominated by operations on transient objects and in-memory persistent objects. A highperformance persistent system should allow these operations to be executed as fast as possible, while imposing minimal overheads on the overall performance.

Thus there is a need for an address translation mechanism that incurs extremely low overheads during CPU-bound operations, low overheads during I/O-bound operations, and no overhead for operations on transient data. Ideally, the mechanism should also work with the best available high-performance compilers without requiring any significant changes or special support from these compilers.

#### **1.1.3** Cost of Orthogonal Persistence

The cost of using orthogonal persistence in an application can be divided into two major components: the cost incurred when accessing data on disk, and the cost incurred when *not* referencing any data on disk (i.e., when not using persistence). The former is the normallyexpected cost associated with loading persistent data from secondary storage into memory. The latter, however, represents costs incurred while performing normal CPU-bound operations on data that is already in memory. This is important because although reducing I/O cost is beneficial for most CPU-intensive applications, maintaining computation performance almost always has higher priority. In general, we define the *cost of orthogonal persistence* as the "cost" of making the distinction between transient and persistent data access transparent to the programmer, that is, it is the cost incurred when *not using* the persistence mechanism.

Traditional fine-grained address translation mechanisms implemented by persistent programming languages incur significant overhead and have fundamental performance limitations for normal CPU-intensive applications. Such schemes typically incur *continual overhead* for checking pointer formats—even if a pointer references in-memory data, a validity check is still necessary before it can be dereferenced because compiled code does not "know" that the pointer is already in an appropriate format.<sup>1</sup> Furthermore, these techniques require sophisticated custom compilers to generate additional code for checking and translating pointer values as necessary. This can be a major downside of such approaches because there are few resources to extensively develop, distribute, and support custom compilers. In fact, the cost of using compilers with poor code generation is typically higher than the cost of address translation itself, defeating the original purpose of building a high-performance implementation. Even if resources were available for compiler development, the continual costs of validity checks make the approach less attractive.

### 1.1.4 Overview

Pointer swizzling at page fault time satisfies all of the requirements outlined earlier for a highperformance address translation scheme. It incurs *zero* overhead during normal CPU-bound operations on data that has already been loaded into memory, and a *small* overhead—roughly 1 to 5 percent depending on the underlying hardware and operating system—when data is

<sup>&</sup>lt;sup>1</sup>It is possible to use compiler optimizations (similar to the Self system [Cha92]) to infer information about the data and reduce the excessive checking overhead. However, such optimizations are fairly hard to implement because of inherent distinctions between object types and object residency.

being faulted into virtual memory from persistent storage on disk. This technique does incur a small space overhead for storing meta-data that is necessary for facilitating address translation, but this is very small compared to the amount of persistent data that can be supported. We expect that the overheads incurred when loading data from disk will be reduced further as CPU speeds improve faster relative to disk speeds.

Pointer swizzling at page fault time also works with existing high-performance offthe-shelf compilers without requiring any additional support from these compilers. This is possible because the approach does not require extending the language syntax or relying on the run-time system for implementing necessary checks and translation. In addition, the basic approach is portable to different operating systems because it requires only minimal support from the underlying virtual memory system.

We can also support a larger (e.g., 64-bit or more) address space on a 32-bit machine using pointer swizzling at page fault time as a general-purpose address reconciliation layer. At the same time, it still has advantages on hardware where address reconciliation may not be necessary. In such cases, it can be used for sharing data across multiple machines with different native formats. Persistent data can be maintained in a common data format that is independent of the hardware word size of the different machines operating on that data, and can be translated into appropriate local addresses as necessary.

The key idea behind our approach is a novel layering of mechanisms. We rely on the operating system and the compiler to do their "jobs" mostly as usual, but strategically intervene at appropriate points for mapping one level of abstraction onto another with techniques such as non-traditional use of virtual memory hardware (in particular, the translation lookaside buffer, or the TLB) and extraction of object layout information from compiler-generated debugging information. We believe that approaching the problem at the right level of abstraction helps in resolving various issues independent of each other.

As part of this dissertation, we have implemented coarse-grained address translation using pointer swizzling at page fault time to provide an efficient persistence mechanism for C++. In doing so, we have essentially implemented a form of *reflection* [KdRB91]<sup>2</sup> for C++via a "back door" because the language itself does not provide builtin support for it.<sup>3</sup> Although our approach is simple and elegant, there are still some complexities—albeit hidden from the average user—in the implementation, due to a lack of language features. The mechanism can be made more general, and easier to implement, with improved language support for reflection.

#### 1.1.5 Contributions

This dissertation makes several useful contributions:

• a novel address translation technique that is mostly independent of the underlying operating system implementation, and can be implemented efficiently on stock hardware;

<sup>&</sup>lt;sup>2</sup>Reflection can be loosely defined as the ability to manipulate or change the internal behavior of a system without actually modifying its implementation (i.e., from the "outside").

$<sup>{}^{3}</sup>C++$  does provide some support for reflection, most notably via the operator overloading capability for normal classes. However, it falls short of complete support because builtin types (including pointers) are treated differently than user-defined classes.

- a new classification scheme based on granularity of several important design choices for implementing orthogonal persistence;

- a detailed performance analysis of various components of a coarse-grained address translation mechanism;

- notion of run-time type description for providing implementation-level information about object layouts at run time;

- a persistent storage system for C++;

- a technique for dynamically resolving C++ method dispatch tables (virtual function tables) in applications against those in persistent storage; and finally,

- an analysis of interactions with operating system implementations and recommendations for improving these implementations to provide better support for system extensions such as persistence, garbage collection, etc.

## Novel Address Translation Technique

Pointer swizzling at page fault time is a novel address translation mechanism that exploits existing virtual memory hardware and operating system features to efficiently implement orthogonal persistence. The approach is highly portable because it uses only standard features provided by modern operating system, and is also compatible with existing high-performance compilers for languages such as C and C++. Pointer swizzling at page fault time is classified as a coarse-grained address translation technique because the granularity of translation is a virtual memory page.

## New Classification Scheme

Various researchers have put forth different taxonomies for address translation approaches based on differences in the pointer swizzling techniques used [Mos92, KK95, MS95, Whi94]. Unfortunately, some of these classifications are unclear, and sometimes even contradictory to each other. Instead of attempting to clarify these taxonomies, we present a new classification scheme using several design choices that we consider important for implementing orthogonal persistence. The classification is presented in terms of the granularity of design choices because we believe that granularity selection is the fundamental issue for implementing persistence.

## **Performance Analysis**

We present detailed performance analysis for various components of a coarse-grained address translation technique, and evaluate the overhead of page-wise address translation against the I/O costs incurred during benchmark operation. As part of the performance results, we also describe our benchmarking philosophy which contends that standard database benchmarks do not accurately model real-world applications, and are not very flexible or configurable. As such, these benchmarks are appropriate only for controlled use in measuring performance of individual components of a persistence mechanism and deriving qualitative conclusions about the system rather than for comparative analysis across multiple systems.

## **Run-Time Type Description**

All address translation techniques require knowledge about the structural layouts of data objects in-memory at run time. This is necessary in order to locate and translate all addresses (pointer fields) in each object that is loaded into memory. We introduce the term *Run-Time Type Description (RTTD)* to describe such implementation-level type information about data objects that is made available to the address translation mechanism at run time. Since C++ is not sophisticated enough to provide builtin support for RTTD, we have implemented our own RTTD mechanism for C++ using compiler-generated debugging information.

## A Persistent Storage System for C++

We have implemented the pointer swizzling at page fault time scheme in the Texas persistent storage system to provide persistence for C++. Texas has been ported to several modern operating systems and is highly suitable as a prototype framework for further research. The system comprises of less than 10,000 lines of C++ source, and the design is modularized such that the code for distinct functionalities (for example, address translation mechanism or operating system interaction) has been separated into individual modules. The system is available via anonymous ftp in source form under the GNU Library General Public License.

## A Technique for Dynamically Resolving C++ Method Dispatch Tables

C++ implements dynamic binding by using virtual functions [Lip91], and pointers to these functions are stored in virtual function tables (VFTs). When an object of a particular class is instantiated, a pointer to the corresponding VFT is (automatically) inserted in that object— dynamic method dispatch is implemented by indexing into the virtual function table of the object on which the method is originally invoked. Unfortunately, unlike data pointers, the VFT pointer in the object points into the *code segment*, and is therefore tightly coupled with the application. Further, the actual value of the pointer usually varies across applications (or even different versions of the same application). This is obviously a problem for persistent objects which are not related to any specific application. Therefore we dynamically resolve VFT pointers specially by "unswizzling" them into special token values that can later be identified and "swizzled" into actual values valid in the *current* application. In effect, this is equivalent to an *extremely simplified* dynamic linker that resolves VFT pointers in persistent objects against the appropriate values in the current application. Further details about the exact mechanism are described in Chapter 4.

## Analysis of Operating System Interactions

Finally, we describe various issues that are related to the interaction of low-level systems (e.g., persistent stores and garbage collectors) with the underlying operating system implementations. We present an analysis of different aspects of virtual memory management and provide recommendations for changes in operating system implementations to improve their coupling with low-level system extensions, and contribute towards making them more portable. We

also discuss a few other relevant operating system features such as virtual memory protection, fault handling, etc.

## 1.2 Advanced Issues

In addition to the various contributions described above, there are many other advanced issues that are beyond the scope of this dissertation and are therefore not addressed here. Some of these issues are:

- *schema evolution*: Currently, there is no support for schema evolution in Texas, although this is independent of address translation and can be implemented on top if necessary. Of course, language support for reflective techniques would be very helpful in such an implementation;

- *security*: We also do not address security issues for access to data in the persistent object store, but it is easy to imagine an implementation along the lines of protection domains in Opal [CLLBH92] or "areas" as in ObjectStore [LLOW91], or just Unix-style owner and group privileges (also supported by Opal); and

- distribution and fault tolerance: These issues need to be carefully designed and architected, and must be implemented to interface well with the basic address translation mechanism. However, it is not an impossible task—we are aware of at least one project where the Texas persistent store has been ported to a Fujitsu AP1000 multicomputer [BS96].

## 1.3 Organization of the Dissertation

The rest of this dissertation is organized as follows.

Chapter 2 describes several important design issues for implementing an orthogonal persistence mechanism. We present a new classification scheme for persistence mechanisms that is based on the granularity choices for different issues, namely, *address translation*, *address mapping*, *data fetching*, *data caching*, and *checkpointing*. For any persistent system, each issue can be resolved at a granularity that is independent of the granularity choice for any other issue. In addition, we also discuss the granularity choices that we have made for each design issue in our implementation of the pointer swizzling at page fault time mechanism in the Texas persistent store.

Chapter 3 contains a detailed description of the pointer swizzling at page fault mechanism. We describe the basic algorithm as well as discuss various related issues such as address space management, and sharing and compatibility with existing systems and code. Although our coarse-grained approach works well for most cases, there are situations where the lack of locality of reference in an application's data structures requires a less coarse-grained approach for address translation. To this end, we discuss fine-grained and mixed-granularity address translation techniques that can also be portably implemented along with the basic coarse-grained technique. We present a competitive argument that pointer swizzling at page fault time incurs zero overhead when the data is already loaded into memory (CPU-bound operations) and a very small overhead during the loading of data from the persistent storage (I/O-bound operations).

Chapter 4 describes the design and implementation of the Texas persistent store, an efficient persistent storage system for C++ that uses the pointer swizzling at page fault time mechanism as a key component for high-performance address translation. We describe the basic design and implementation of Texas; the implementation details also include information about virtual memory and file system abstraction layers designed to make interactions with the underlying operating system easy to implement. It should be noted that although Texas relies on virtual memory caching, it is simply an implementation choice that is completely orthogonal to the address translation mechanism. We intend for Texas to be used as a research platform for further studies in issues related to efficient orthogonal persistence implementation. In the current context, we use it for gathering detailed performance results of the pointer swizzling at page fault time technique.

Chapter 5 presents detailed results for the performance of Texas and pointer swizzling at page fault time using the OO1 database benchmark traversal operations. The performance results presented in this chapter empirically validate our basic competitive argument for pointer swizzling at page fault time. We have measured the performance on Linux and Solaris, two of the most popular operating systems, and show that the total overhead of Texas is usually between 1 and 5 percent for most situations on both platforms. In addition to the empirical results, we also describe our philosophy for benchmarking; specifically, we argue that some of the widely-used standard benchmarks are inappropriate for quantitative performance comparison across different persistent systems, and are acceptable only for controlled measurements and qualitative analysis of a single system. These benchmarks do not represent real applications which are most likely to take advantage of a persistent storage system. We believe that such applications typically have sophisticated data structures and perform significant CPU-bound computations over these data structures, unlike the benchmarks which do not offer rich data structures and include minimal computation behavior.

Chapter 6 tackles the issue of providing implementation-level information for types at run time. We call this Run-Time Type Description (RTTD) to distinguish it from the recently-introduced Run-Time Type Identification (RTTI) feature for C++. RTTD constitutes information about types and in-memory layouts of data objects, and is necessary for the correct operation of pointer swizzling at page fault time. In contrast, RTTI supports only languagelevel information such as run-time type equivalence checks, which is obviously insufficient for object layout information. RTTD may also be useful for other systems such as garbage collectors, advanced profiling and tracing tools, etc. which also benefit from detailed object layout information. We describe our basic strategy which uses compiler-generated debugging information instead of special-purpose preprocessors, and present arguments about why our approach is preferable. The chapter also presents details about our RTTD implementation for C++ which is currently used for Texas and a real-time garbage collector. We also describe expected performance characteristics of our approach based on some preliminary measurements and show that the additional overhead is negligible compared to the typical compilation and linkage costs. Chapter 7 is devoted to a discussion of various issues that are important for portability and interaction with various operating system implementations. It also suggests directions for improving operating system implementations to make it easy for integrating low-level system extensions such as persistence mechanisms, garbage collectors, etc. We are mainly interested in interaction with the virtual memory system because pointer swizzling at page fault time is primarily dependent on existing virtual memory hardware and protection facilities supported by the operating system. An important point that is highlighted during the discussion is that unlike some other systems, pointer swizzling at page fault time does *not* require advanced capabilities from the operating system although it is designed to exploit such capabilities, if they exist, for improved performance. We also briefly describe other operating system features, particularly virtual memory protection violation handling, that can be improved for overall performance gains.

Chapter 8 contains a brief sketch of some future research directions that appear promising for further study of high-performance address translation techniques and other extensions to the Texas persistent storage system. Many of these issues are related to the development of a competitive storage management technique for efficient checkpointing and stable storage capabilities. We also reiterate the advanced issues (mentioned above) that are beyond the scope of the current discussion. Finally, we summarize our findings and conclude in Chapter 9.

## Chapter 2

## **Design Issues for Persistence**

## 2.1 Introduction

In this chapter, we provide a general background for persistence, including a description of different types of persistence that are commonly implemented by various persistent systems. Our approach is designed to implement *orthogonal persistence* which provides the cleanest implementation model by separating the persistence property of an object from its type.

We also briefly describe some existing taxonomies for address translation mechanisms, and show that they are unclear for general usage. Instead, we choose to use the *granularity* of an operation as the metric for classifying different persistence mechanisms. We identify a set of basic design issues that must be considered when implementing a persistent system, and define the classification in terms of granularity choices for these design issues. We argue that this classification is better than the existing taxonomies which are primarily concerned only with the issue of address translation.

Another interesting part of this chapter is a brief discussion on fine-grained address translation and how it measures up to a coarse-grained mechanism such as ours. As we will show, fine-grained translation schemes incur some basic costs that are inherent to their general implementations. We believe that fine-grained approaches should be avoided except in those cases where other features such as locking, consistency, etc. are also being implemented at a finer granularity. Finally, we provide a background survey of some other research in persistence that is most relevant to the current discussion.

## 2.2 Background

File systems have traditionally been used to save data both for temporary storage between program executions and for general long-term storage. Unfortunately, file systems have efficiency drawbacks, because there are two parallel memory hierarchies (disk and RAM<sup>1</sup> in both), and data must be moved between them. Often there are situations where the same data exists in both memory caches, and in both disk areas; this is a poor use of resources. Also, a file system's normal view of data is a "stream of bytes" with no associated structure or type information,

<sup>&</sup>lt;sup>1</sup>In this dissertation, we use the terms RAM and main memory interchangeably for referring to the physical memory in a computer system.

while the in-memory representation of data structures is in terms of pointer-linked objects. This creates a fundamental *impedance mismatch* [CM84] between the two representations.

Persistent systems are designed to solve this impedance mismatch between volatile and non-volatile storage, and to alleviate the efficiency problems associated with file systems. In this section, we provide a general background on persistence, including descriptions of various types of persistence, before briefly discussing our approach which is designed to implement persistence for C++ and other high-level languages.

## 2.2.1 Persistence

All data created and manipulated by normal applications are usually *transient* in nature because their lifetime is bounded by the execution of the process in which they were created. In contrast, *persistent* data can outlive the execution of the process that creates them. Persistent object stores are repositories used for storing arbitrarily complex persistent data structures while maintaining pointer semantics just as in virtual memory. In essence, a persistent object store can be viewed as a long-lived virtual memory that persists after applications complete execution, and which can be accessed by the same (or different) applications when they are run again in the future.

#### 2.2.2 Types of Persistence

We classify persistence implementation mechanisms into different kinds based on the type of persistence supported by each specific approach. In general, persistence can be broadly divided into three kinds:

- class-based persistence,

- orthogonal persistence, and

- reachability-based persistence.

The simplest persistence mechanism incorporated in many applications relies on *class-based persistence*. The basic idea requires that any type or class which may be instantiated to create persistent objects *must* inherit from a top-level abstract "persistence" class. This special class defines the *interface* for saving and restoring data from a persistent object store. Each derived class that inherits from the top-level class is required to *implement* the specified interface (possibly via serialization methods) to save and restore objects of that particular derived class. This is obviously cumbersome for the programmer who must carry the burden of implementing the persistence mechanism, making the whole process extremely tedious and highly error-prone. Another problem with this approach is that it promotes code duplication in the usual case. Any type that may potentially be used to create persistent objects requires two definitions—one for normal transient objects and the other (derived from the special abstract class) for persistent objects. As a result, transient and persistent objects of the same "logical" (application) type are now *not equivalent* in terms of the "physical" (actual) type, and code that operates on one kind of object cannot operate on the other. One obvious solution is to make the derived class multiply inherit from both the actual type and the abstract class but

this is likely to add a slew of other problems related to the use of multiple inheritance. Also, this approach does not work for builtin types because their definitions cannot be changed easily in most languages.

Unlike class-based persistence, orthogonal persistence [ABC<sup>+</sup>83a, AM95] decouples the lifetime of an object from its type. In other words, persistence is viewed as a storage class<sup>2</sup> rather than as a property of the object type. The name derives from the requirement that the type of an object must be independent of (that is, orthogonal to) its storage class. In other words, persistence is a property of individual objects, not of their classes (or types), and any object can be made persistent regardless of its type. Since persistence is decoupled from the type system, this approach supports a clean implementation model that is transparent to the application programmer who does not need to make any major modifications to the application code to use the persistence mechanism.

Finally, reachability-based persistence [ABC+83a, ACCM83] is a general form of orthogonal persistence. The basic principle of this approach requires that all objects reachable from a well-defined persistent root (or roots) automatically become persistent. As with orthogonal persistence, the type of an object is not relevant when making it persistent based on the reachability property. The implementation ease for this approach depends on the support available from the programming language. In general, we believe that orthogonal persistence (and its derivatives such as reachability-based persistence) are preferable to class-based persistence or other *ad hoc* mechanisms.

### 2.2.3 Our Approach

Historically, implementations of persistence mechanisms have been slow due to at least two different cost factors. One of them is a direct (and fairly significant) cost of actions such as checking pointer formats, maintaining bookkeeping information, etc. in software. The other is an indirect cost related to the use of specialized compilers for implementing persistence through language extensions. Typically, there has been a lack of resources for extensive development of these specialized compilers and as a result, code generated by such compilers is often several times slower than that generated by most widely-available, high-performance optimizing compilers. In addition, we believe that fundamentally slow approaches used for implementing traditional address translation techniques are another potential source of performance problems. For example, some pointer-wise translation techniques require that the format of a pointer be checked every time it is dereferenced, *even if it is a transient pointer*.

We solve both these problems by designing a novel implementation strategy that is compatible with code generated by existing off-the-shelf compilers without requiring any special modifications or sacrificing optimization opportunities. We also reduce our overheads to a minimum by effectively using existing hardware to check for pointer formats, thereby avoiding software checks which are usually more expensive. This has an overall effect of removing major obstacles in the acceptance of general-purpose languages for persistent applications because of its performance and compatibility with both stock hardware and existing compilers.

$<sup>^{2}</sup>$ A storage class describes how an object is stored. For example, the storage class of an automatic variable in C or C++ corresponds to the stack because the space for the object is typically allocated on the data stack, and its lifetime is bounded by the scope in which it was allocated.

Although our approach is focused on implementing mainly orthogonal persistence (for languages such as C and C++), it is designed to be compatible with reachability-based persistence. However, the current implementation of Texas does not support reachability-based persistence. The primary obstacle in implementing this is the lack of language support for identifying type information for arbitrary data on both the stack and the transient heap. This is essentially the same problem as the one faced by garbage collectors for languages such as C or C++. We believe that it is straightforward to use solutions that are similar to those applicable in the other domain<sup>3</sup> but we have not yet done so. We are aware of at least one project that is using pointer swizzling at page fault time techniques and extending Texas to implement reachability-based persistence for C++ and Modula-3 [HN97].

## 2.3 Address Translation Taxonomies

Persistence has been an active research area for over a decade and several researchers have put forth taxonomies for pointer swizzling techniques [Mos92, KK95, MS95, Whi94]. In this section, we describe important details about each of these taxonomies and highlights various similarities and differences among them. In addition, we also provide motivation for a general classification of persistent systems based on granularity issues.

## 2.3.1 Eager vs. Lazy Swizzling

Moss [Mos92] describes one of the first studies of different address translation approaches and the associated terminology developed for classifying these techniques. The primary classification is in terms of "eager" and "lazy" swizzling based on *when* the address translation is performed. Typically, eager swizzling schemes swizzle an entire collection of objects together, where the size of the collection is somehow bounded. In other words, the need for checking pointer formats, and the associated overhead, is avoided by performing aggressive swizzling. In contrast, lazy swizzling schemes follow an incremental approach by using dynamic checks for unswizzled objects. That is, there is no predetermined or bounded collection of objects that must be swizzled together. Instead, the execution dynamically locates and swizzles new objects depending on the access patterns of the application.