Copyright

by

Ardavan Pedram

2013

# The Dissertation Committee for Ardavan Pedram certifies that this is the approved version of the following dissertation:

# Algorithm/Architecture Codesign of Low Power and High Performance Linear Algebra Compute Fabrics

| Committee:                      |  |  |  |  |

|---------------------------------|--|--|--|--|

|                                 |  |  |  |  |

| Andreas Gerstlauer, Supervisor  |  |  |  |  |

| Robert van de Geijn, Supervisor |  |  |  |  |

| Peter Hofstee                   |  |  |  |  |

| Lizy John                       |  |  |  |  |

| Keshay Pingali                  |  |  |  |  |

## Algorithm/Architecture Codesign of Low Power and High Performance Linear Algebra Compute Fabrics

by

### Ardavan Pedram, B.E., M.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm August~2013}$

Dedicated to My Late Role Models: Doctor Bahman Pedram and Professor Caro Lucas

### Acknowledgments

"Losing family obliges us to find our family. Not always the family that is our blood, but the family that can become our blood. And should we have the wisdom to open our door to this new family, we will find that the wishes and hopes we once had ... for the father who once guided us, for the brother who once inspired us, ... those wishes are there for us once again."

I wish to thank the incredible people whose company fulfilled different aspects of my new life with joy and the sense of creativity. People that intentionally and unintentionally taught me great lessons about excellence in action. People who maybe without even knowing it became my family, inspired me to dream beyond my limits, and guided me to the path of achieving those dreams.

First and foremost, I want to express my gratitude to my supervisors Professor Robert van de Geijn and Professor Andreas Gerstlauer. I am glad that I got the chance to know and introduce these great guys to each other and gain success while being protected in their safe hands.

The first time I got to know Robert goes back to 2006 when I found his paper on the material and it got me hooked. The excellent style of explanation got me interested on Robert's research and I read several other papers of his work wondering if I could join his group someday. I met him personally and

after two short conversations he offered to hire me in his group and my dream came true. Robert is an excellent teacher and a caring supervisor. Robert and Doctor Maggie Mayers, who I want to thank dearly, went far beyond a student-advisor relationship and made me feel like I have a family here. Some relationships just develop by themselves and this one turned my whole PhD studies into a joyful life.

I first met Andreas when he had just joined UT as a new faculty member. I took his course and experienced a great instructor-student relationship. Andreas is always patient with questions and gives me confidence to ask more and learn more. He has a lot of energy and interest in challenging research. As time went by in my PhD studies he backed me up more and more in all of the tight deadlines for different venues and worked persistently to keep me motivated. Andreas always considered my preferences in his decisions and it makes me proud to have an advisor who understands me so deeply.

I want to thank each of the committee members who were great motivators and supporters of this project. A special thanks to Doctor Peter Hofstee who I am honored to have on my committee. Peter spent several hours in different locations having one-to-one discussions to give me perspective and encouraged me to follow the correct scientific approach. I am really grateful to Professor Lizy John for her support when I needed guidance and was struggling to make a correct decisions with my graduate studies. I experienced one of the most exciting courses in graduate school with her and learnt the process of critical thinking from her. Lizy has always been a great and kind person

to refer to when I had questions about my project and gave me directions to correct resources and people in the field. A special thank you is extended to Professor Keshav Pingali for being a great role model. Keshav is a great scholar with an extra-ordinary personality that I have thorough respect for. Keshav is an expert in the field and gave me great subjects to think about for future work and possible extensions to my ideas. I learnt from him a great deal about the applications of my research topic in science and how to think outside of the box. He gave me the great opportunity of teaching his class as a guest lecturer.

I met great scholars and professors in UT during these last years. Specially, I want to thank Professor Earl Swartzlander. Earl has always emboldened me in my career to strive higher. He always found time for me to talk about our research overlap and gave me great advice on how to approach new problems with confidence. He introduced me to many successful people whose work helped me substantially. One of these great people was Doctor Eric Quinnell. I want to express my gratitude to Eric for his support and his research. I used his dissertation to learn about floating-point units. Eric also read my first paper's early drafts when I needed guidance to lay the foundation of my research correctly.

I want to specially thank my main collaborator Doctor John McCalpin.

I first met John in 2012 in Texas Advance Computing Center and bombarded him with my questions. He answered all of them in great detail and his intuition helped me to start extending my research. After a year, I returned to him

with a plan and he kindly spent his research time with me. He also gave me the opportunity to work under his supervision in Texas Advanced Computing Center as an intern to experience even more. I always found valuable gems of knowledge in his conversations with me and am really grateful for his support and his friendship.

My friends in the FLAME research group kept me going for these years. I want to show gratitude to Field van Zee who is a great scientist and a genuine friend. He kindly offered to read my papers and gave me great feedback on the material. Field always answered my questions with great patience. I want to express my thanks to Tze Meng Low, Bryan Marker, and Martin Schatz with whom I shared many of my research and life issues and they always offered a hand to help. I have had great discussions with these friends and never felt bored. I want to thank Doctor Jack Poulson who is my first American friend and cared for me in time of hardship. Jack is an extremely smart and a valuable friend. My friendship with Jack is a case that proved to me that there is a state of mind that two people can reach to understand each other perfectly regardless of their backgrounds. I also want to thank Doctor Victor Eijkhout for the many occasions that he gave me great feedback on my work.

I want to thank my co-authors and collaborators from The University of Wisconsin Maddison Doctor Zohaib Gilani and Professor Nam Sung Kim, and from AMD Research Doctor Michael Schulte. I first met Zohaib and Mike in ASAP 2011 and we discussed possible collaboration. Mike is a great motivator and encouraged me to follow the path of my research. Our collaboration

yielded into a successful paper in ASAP 2012.

Through these years I was blessed to get to know exceptional individuals in different fields of art and science and each inspired me to be a better person. These friends helped me to know my weaknesses better and helped me to solve my life struggles. Their care for me made me believe in myself and the bliss of friendship more and more. I want to thank Roja Najafi and Doctor Behnam Robatmilli, who were my best Persian friends in Austin and gave me unconditional support like a sister and a brother. I wish to thank Bonnie Gammill who taught me how to see beauty in life with a more optimistic view and who cared for me in great deal and made me feel appreciated and loved. Finally, I am indebted to our Graduate Program Coordinator Melanie Gulick in great deal. I want to thank her for being a true friend to me who like my own mother gave me great advice about my personal life and my graduate studies. I want to thank my other great friends Doctor Arjang Hassibi, Benini, Khosrow Afroozeh, Doctor Mehdi Haghshenas, Babak Fallah, Shahrzad Mirkhani, Doctor Sahar Ayazian, Maysam Lavasani, Khubaib, and Mehmet Basoglu.

Finally, I want to thank my family members who always believed in me. I want to thank my parents Doctor Bahman Pedram and Nikou Zandie. I did not get a chance to visit my dad for a last time although he was asking for me all the time. I owe whatever makes me happy to my mother who patiently hid all the sad stories back home and went trough all the hardship by herself. I want to thank my great sister Doctor Elham Pedram. Elham is the burning flame of life and a great motivator to me and people around her. She is a true

role model and a great mother. I am obliged to my uncle Robert Kayvon who took care of me like my own father would and kept in touch with me all of these years abroad. Bob is the most optimistic and generous person I have ever met. His door was always open to me and he treats me like his own son.

Algorithm/Architecture Codesign of Low Power and High Performance Linear Algebra Compute Fabrics

Publication No.

Ardavan Pedram, Ph.D.

The University of Texas at Austin, 2013

Supervisors: Andreas Gerstlauer

Robert van de Geijn

In the past, we could rely on technology scaling and new micro-architectural techniques to improve the performance of processors. Nowadays, both of these methods are reaching their limits. The primary concern in future architectures with billions of transistors on a chip and limited power budgets is power/energy efficiency. Full-custom design of application-specific cores can yield up to two orders of magnitude better power efficiency over conventional general-purpose cores. However, a tremendous design effort is required in integrating a new accelerator for each new application.

In this dissertation, we present the design of specialized compute fabrics that maintain the efficiency of full custom hardware while providing enough flexibility to execute a whole class of coarse-grain operations. The broad vision is to develop integrated and specialized hardware/software solutions that are

xi

co-optimized and co-designed across all layers ranging from the basic hardware foundations all the way to the application programming support through standard linear algebra libraries.

We try to address these issues specifically in the context of dense linear algebra applications. In the process, we pursue the main questions that architects will face while designing such accelerators. How broad is this class of applications that the accelerator can support? What are the limiting factors that prevent utilization of these accelerators on the chip? What is the maximum achievable performance/efficiency? Answering these questions requires expertise and careful codesign of the algorithms and the architecture to select the best possible components, datapaths, and data movement patterns resulting in a more efficient hardware-software codesign. In some cases, codesign reduces complexities that are imposed on the algorithm side due to the initial limitations in the architectures.

We design a specialized Linear Algebra Processor (LAP) architecture and discuss the details of mapping of matrix-matrix multiplication onto it. We further verify the flexibility of our design for computing a broad class of linear algebra kernels. We conclude that this architecture can perform a broad range of matrix-matrix operations as complex as matrix factorizations, and even Fast Fourier Transforms (FFTs), while maintaining its ASIC level efficiency.

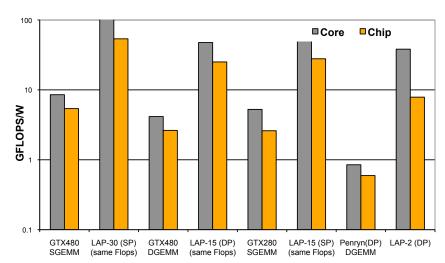

We present a power-performance model that compares state-of-the-art CPUs and GPUs with our design. Our power-performance model reveals sources of inefficiencies in CPUs and GPUs. We demonstrate how to overcome such inefficiencies in the process of designing our LAP.

As we progress through this dissertation, we introduce modifications of the original matrix-matrix multiplication engine to facilitate the mapping of more complex operations. We observe the resulting performance and efficiencies on the modified engine using our power estimation methodology. When compared to other conventional architectures for linear algebra applications and FFT, our LAP is over an order of magnitude better in terms of power efficiency. Based on our estimations, up to 55 and 25 GFLOPS/W single- and double-precision efficiencies are achievable on a single chip in standard 45nm technology.

# **Table of Contents**

| Ackno   | wledgments                                   | $\mathbf{v}$ |

|---------|----------------------------------------------|--------------|

| Abstra  | nct                                          | xi           |

| List of | Tables                                       | xviii        |

| List of | Figures                                      | xix          |

| Chapte  | er 1. Introduction and Background            | 1            |

| 1.1.    | Thesis Statement                             | 2            |

| 1.2.    | Linear Algebra Processor Overview            | 3            |

|         | 1.2.1. Architecture                          | 6            |

|         | 1.2.2. Programming model                     | 7            |

| 1.3.    | Evaluation Methodology                       | 8            |

|         | 1.3.1. Performance Analyses                  | 9            |

|         | 1.3.2. Component selection                   | 10           |

|         | 1.3.3. Power Modeling of Architectures       | 11           |

| 1.4.    | Contributions                                | 12           |

|         | Thesis Outline                               | 14           |

| Chapte  | er 2. Related Work                           | 15           |

| 2.1.    | General-Purpose Processors                   | 16           |

|         | 2.1.1. SIMD ALUs and Vector Processors       | 18           |

|         | 2.1.2. GPGPUs                                | 20           |

| 2.2.    | Custom Design Architectures and Accelerators | 22           |

|         | 2.2.1. Cell Broadband Engine                 | 25           |

|         | 2.2.2. ClearSpeed CSX                        | 28           |

|         | 2.2.3. Systolic Arrays                       | 30           |

|         | 2.2.4. FPGA Implementation                   | 32           |

| Chapte                                    | er 3. Linear Algebra Core (LAC) Design                      | 34  |

|-------------------------------------------|-------------------------------------------------------------|-----|

| 3.1.                                      | Basic Operation                                             | 35  |

| 3.2.                                      | PE Micro-Architecture                                       | 37  |

|                                           | 3.2.1. LAC Communication                                    | 38  |

|                                           | 3.2.2. Local Store                                          | 40  |

|                                           | 3.2.3. Control                                              | 41  |

| 3.3.                                      | GEMM Algorithm                                              | 43  |

| 3.4.                                      | Core Architecture                                           | 45  |

| 3.5.                                      | Core-Level Exploration                                      | 47  |

| 3.6.                                      | Power Analysis                                              | 49  |

| 3.7.                                      | Summary                                                     | 54  |

| Chapte                                    | er 4. Linear Algebra Processor (LAP) Design                 | 55  |

| 4.1.                                      | The LAP Architecture                                        | 55  |

| 4.2.                                      | Chip-Level Exploration                                      | 58  |

|                                           | 4.2.1. Memory size vs. bandwidth                            | 60  |

|                                           | 4.2.2. Number of LACs vs. on-chip bandwidth and memory size | 61  |

|                                           | 4.2.3. On-chip memory size vs. off-chip bandwidth           | 63  |

| 4.3.                                      | Model Validation and Performance Prediction                 | 66  |

| 4.4.                                      | Power and Area Exploration                                  | 69  |

| 4.5.                                      | Comparative Power and Performance Analysis                  | 74  |

| 4.6.                                      | Summary                                                     | 80  |

| Chapter 5. Generalization to Level-3 BLAS |                                                             | 82  |

| 5.1.                                      | Level-3 BLAS Operations                                     | 83  |

| 5.2.                                      | SYRK and SYR2K                                              | 85  |

|                                           | 5.2.1. Unblocked SYRK on LAC                                | 85  |

|                                           | 5.2.2. Blocked SYRK on LAC                                  | 87  |

| 5.3.                                      | TRSM                                                        | 91  |

|                                           | 5.3.1. Unblocked TRSM on LAC                                | 91  |

|                                           | 5.3.2. Blocked TRSM on LAC                                  | 96  |

|                                           | 5.3.3. Performance Analysis                                 | 98  |

| 5.4.                                      | Results                                                     | 100 |

| 5.5                                       | Summary                                                     | 104 |

| Chapter 6. |        | Generalization Beyond Level-3 BLAS                   | 105 |

|------------|--------|------------------------------------------------------|-----|

| 6.1.       | Matri  | x Factorizations                                     | 106 |

|            | 6.1.1. | Cholesky Factorization                               | 108 |

|            | 6.1.2. | LU Factorization with Partial Pivoting               | 111 |

|            | 6.1.3. | QR Factorization and Vector Norm                     | 115 |

|            | 6.1.4. | Hardware Extensions                                  | 119 |

|            | 6.1.5. | Results                                              | 120 |

| 6.2.       | Fast I | Fourier Transform                                    | 122 |

|            | 6.2.1. | FFT Algorithm and Mapping                            | 123 |

|            | 6.2.2. | Hardware Extensions                                  | 126 |

|            | 6.2.3. | Results                                              | 127 |

| 6.3.       | Sumn   | nary                                                 | 129 |

| Chapte     | er 7.  | Summary and Future Work                              | 131 |

| 7.1.       | Summ   | nary                                                 | 131 |

| 7.2.       | Futur  | e Work                                               | 133 |

| Appen      | dices  |                                                      | 136 |

| Appen      | dix A  | . Core Level Extensions for<br>Matrix Factorizations | 137 |

| A.1.       | Relate | ed Work                                              | 138 |

| A.2.       | Hardy  | ware Extensions                                      | 139 |

|            | A.2.1. | Cholesky Factorization                               | 140 |

|            | A.2.2. | LU Factorization with Partial Pivoting               | 141 |

|            | A.2.3. | QR Factorization and Vector Norm                     | 141 |

| A.3.       | Arch   | itecture                                             | 143 |

|            | A.3.1. | Floating-Point MAC Unit                              | 144 |

|            |        | Reciprocal and (Inverse) Square-root Units           | 145 |

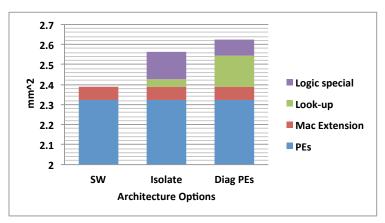

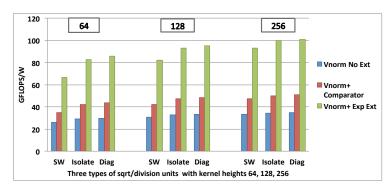

| A.4.       | Exper  | rimental Results and Implementations                 | 149 |

|            | A.4.1. | Area and Power Estimation                            | 150 |

|            | A.4.2. | Performance and Efficiency Analysis                  | 152 |

| A.5.       | Summ   | nary                                                 | 157 |

| Appendix B. Core Level Extensions for<br>Fast Fourier Transform | 159 |

|-----------------------------------------------------------------|-----|

| B.1. Related Work                                               | 160 |

| B.2. FFT Algorithm Mapping                                      | 161 |

| B.2.1. Radix-4 FFT Algorithms on the PEs                        | 162 |

| B.2.2. FFT on the Core                                          | 163 |

| B.2.3. FFT Memory Hierarchy for Larger Transform Sizes          | 167 |

| B.3. Architecture Trade-offs and Configurations                 | 171 |

| B.3.1. Analytical models                                        | 172 |

| B.3.2. Core Configuration                                       | 175 |

| B.3.3. PE Configuration                                         | 177 |

| B.3.4. Off-core Memory Configuration                            | 179 |

| B.4. Experimental Results and Implementations                   | 182 |

| B.5. Summary                                                    | 185 |

| Bibliography                                                    | 186 |

# List of Tables

| 3.1. | 45nm scaled performance and area for a LAP PE with 16KBytes of dual-ported SRAM                                                                                                                          | 51  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2. | 45nm scaled performance and area of various cores running GEMM                                                                                                                                           | 54  |

| 4.1. | Bandwidth and memory requirements of different layers of memory hierarchy.                                                                                                                               | 59  |

| 4.2. | 45nm scaled performance and area of various systems running GEMM                                                                                                                                         | 79  |

| 4.3. | Comparison between main design choices in the studied platforms.                                                                                                                                         | 80  |

| 5.1. | LAC efficiency for level-3 BLAS algorithms at 1.1 GHz                                                                                                                                                    | 103 |

| 6.1. | Computing the Householder transformation. Left: simple formulation. Right: efficient computation                                                                                                         | 116 |

| 6.2. | Comparison between the proposed hybrid core and several alternatives for cache-contained double-precision FFTs scaled to 45nm.                                                                           | 129 |

| A.1. | Operations of the divide and square-root unit with control signals [113]                                                                                                                                 | 147 |

| A.2. | Total cycle counts and dynamic energy consumption for different architecture options (columns for divide/square-root options, and row sets for MAC unit extension options), algorithms and problem sizes | 151 |

| В.1. | Different FFT core requirements for both overlapped and non-overlapped versions of $N \times N$ 2D and $N^2$ 1D FFTs                                                                                     | 171 |

| B.2. | PE SRAM options and their area, performance, and energy consumption report by CACTI [93]                                                                                                                 | 180 |

| B.3. | PE designs for dedicated LAC, dedicated FFT, and a hybrid design that can perform both operations                                                                                                        | 183 |

# List of Figures

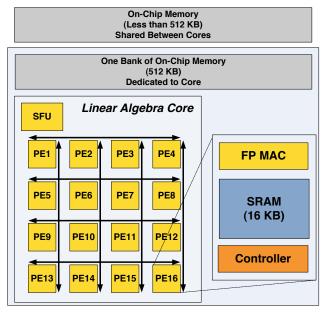

| 1.1. | A single Linear Algebra Core (LAC) in LAP Architecture, SFU is Special Functional Unit                                                                                                                                                                                                                                                                                                                                              | 6  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

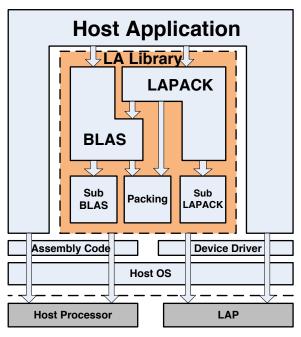

| 1.2. | LAP programming environment                                                                                                                                                                                                                                                                                                                                                                                                         | 7  |

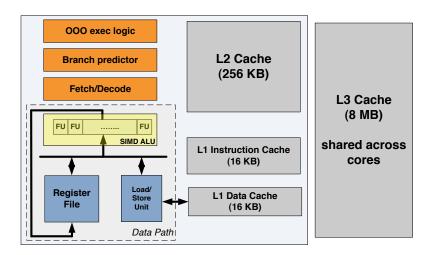

| 2.1. | (a) A typical general-purpose processor memory hierarchy and core architecture                                                                                                                                                                                                                                                                                                                                                      | 18 |

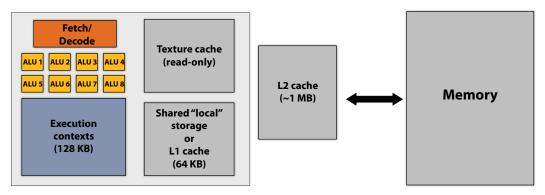

| 2.2. | Modern GPU core, and memory hierarchy architecture                                                                                                                                                                                                                                                                                                                                                                                  | 20 |

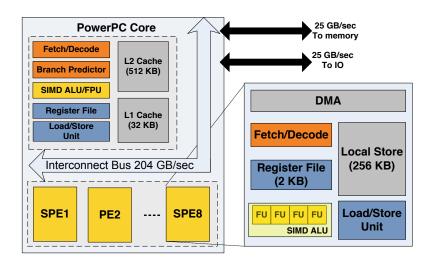

| 2.3. | (a) Cell BE processor architecture [23]                                                                                                                                                                                                                                                                                                                                                                                             | 25 |

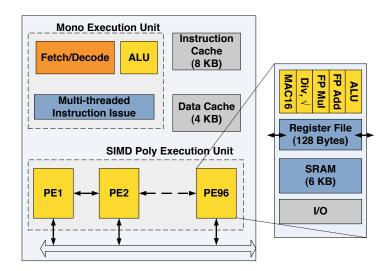

| 2.4. | Clearspeed Multi-threaded array processor architecture [28]                                                                                                                                                                                                                                                                                                                                                                         | 28 |

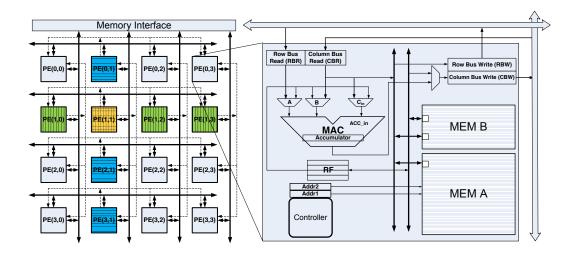

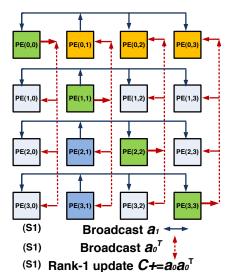

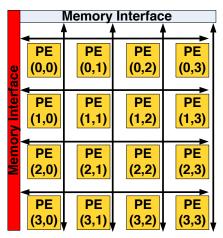

| 3.1. | The LAC Architecture. The highlighted PEs on the left illustrate the PEs that own the current column of $4 \times k_c$ matrix $A$ and the current row of $k_c \times 4$ matrix $B$ for the second rank-1 update $(p=1)$ . It is illustrated how the roots (the PEs in second columns and row) write elements of $A$ and $B$ to the buses and the other PEs read these. The dashed lines show the current data movement on the buses | 35 |

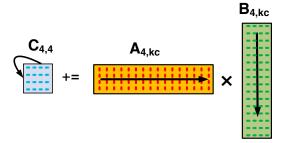

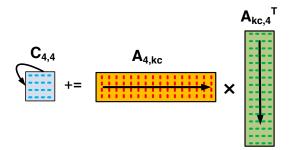

| 3.2. | Matrix multiplication as a series of Rank-1 updates                                                                                                                                                                                                                                                                                                                                                                                 | 36 |

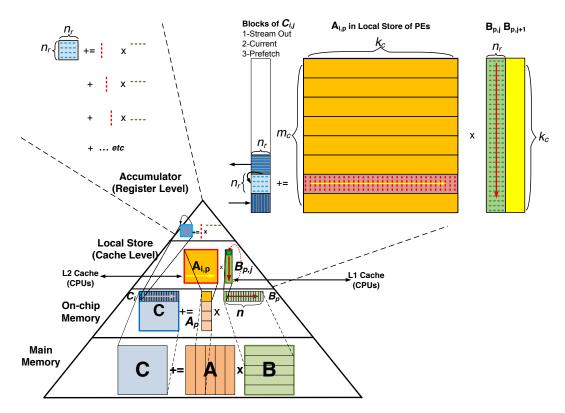

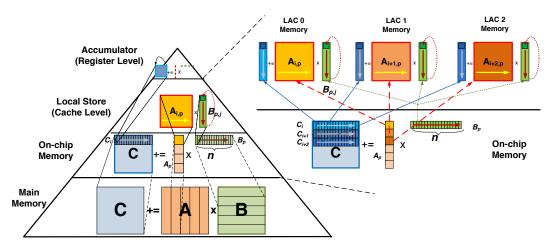

| 3.3. | Memory hierarchy while doing GEMM. In each of the top three layers of the pyramid, the largest matrix is resident, while the other matrices are streamed from the next layer down                                                                                                                                                                                                                                                   | 42 |

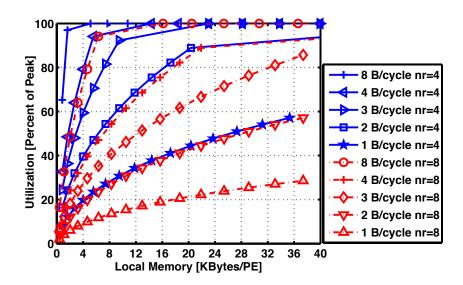

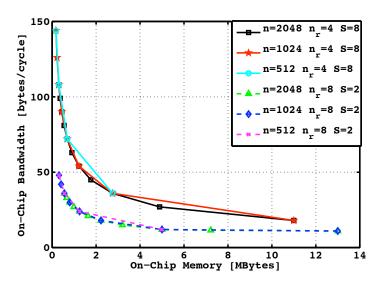

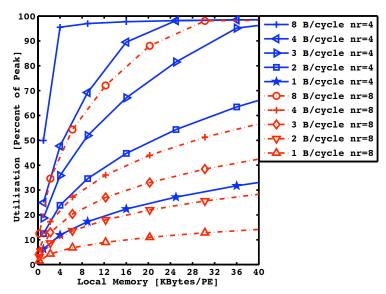

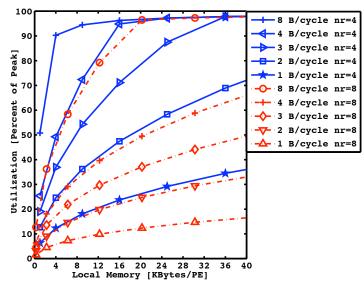

| 3.4. | Estimated core performance as a function of the bandwidth between LAC and on-chip memory, and the size of local memory with $n_r = 4$ and $n_r = 8$ , $m_c = k_c$ , and $n_r = 512$                                                                                                                                                                                                                                                 | 48 |

| 3.5. | Core Performance vs. bandwidth between LAC and on-chip memory for peak performance with $n_r = 4$ and $n_r = 8$ , $m_c = k_c$ , and $n = 512$                                                                                                                                                                                                                                                                                       | 48 |

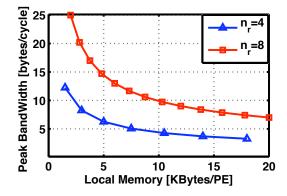

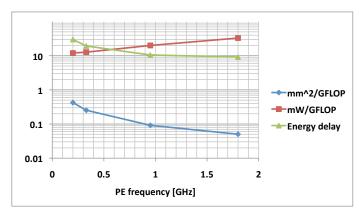

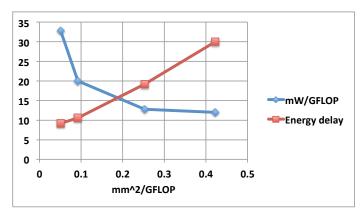

| 3.6. | Efficiency metrics of PE. 1GHz appears to be the sweet-spot of the design.                                                                                                                                                                                                                                                                                                                                                          | 52 |

| 3.7. | Power efficiency and energy-delay vs. area efficiency at different frequencies                                                                                                                                                                                                                                                                                                                                                      | 53 |

| 4.1. | Memory hierarchy with multiple cores in a LAP system                                                                                                                                                                                                                                                                                                                                                                                | 56 |

| 4.2.  | On-chip bandwidth vs. memory size for different core organizations, and problem sizes for fixed number of total PEs, and $m_c = k_c$ . The utilization in all cases is over 93% |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

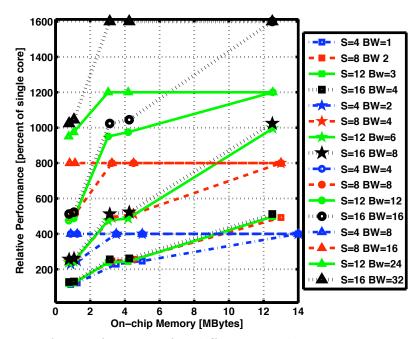

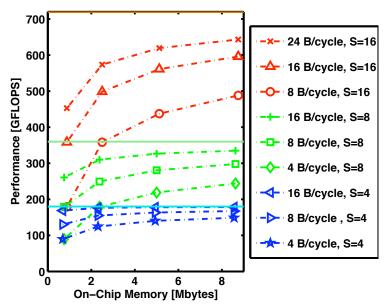

| 4.3.  | LAP performance for different on-chip memory sizes, different number of cores, and different total on-chip bandwidths with $n_r = 4$ and s=4, 8, 12, 16                         |

| 4.4.  | Blocking algorithm to map a big problem on a small on-chip memory. a) blocking for quarter size b,c)blocking for half size.                                                     |

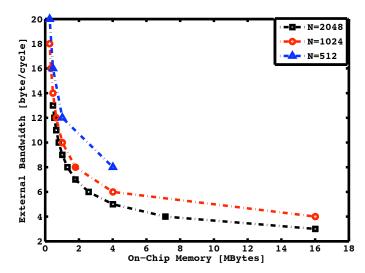

| 4.5.  | External Bandwidth vs. Size of on-chip memory tradeoff for different original problem sizes. All utilization numbers are over 92%                                               |

| 4.6.  | LAP performance as a function of external off-chip bandwidth and the size of on-chip memory with $n_r = 4$ , $m_c = k_c$                                                        |

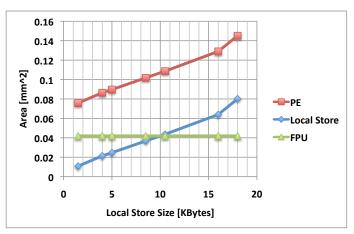

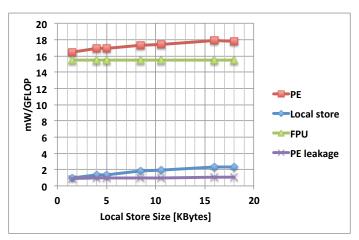

| 4.7.  | Area of a single PE in a 4x4 core for different local store sizes at 45nm                                                                                                       |

| 4.8.  | Leakage, local store, and total power efficiency of a PE at in a 4x4 core at 45nm                                                                                               |

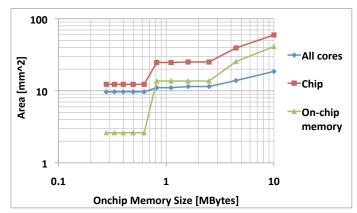

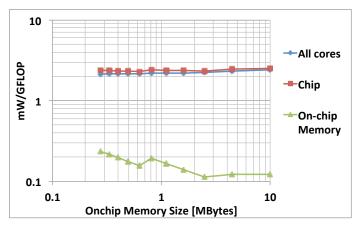

| 4.9.  | Area of cores, on-chip memory and a total 128 MAC unit system with S=8 4x4 cores, different on-chip SRAM memory sizes, and n=2048                                               |

| 4.10. | Power efficiency of cores, on-chip memory and a total 128 MAC unit system with S=8 4x4 cores, different on-chip SRAM memory sizes, and n=2048                                   |

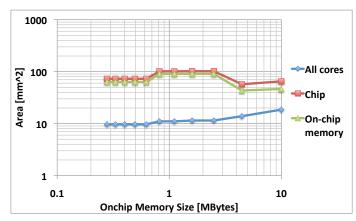

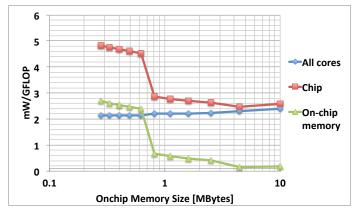

| 4.11. | Area of cores, on-chip memory and a total 128 MAC unit system with S=8 4x4 cores, different on-chip NUCA memory sizes, and n=2048                                               |

| 4.12. | Power efficiency of cores, on-chip memory and a total 128 MAC unit system with S=8 4x4 cores, different on-chip NUCA memory sizes, and n=2048                                   |

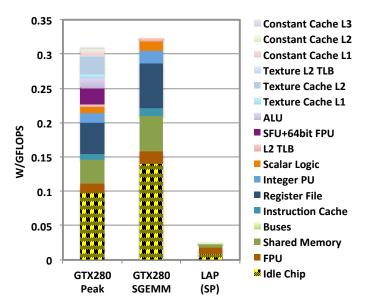

| 4.13. | Normalized power breakdown of Nvidia Tesla GTX280 versus LAP at 65nm                                                                                                            |

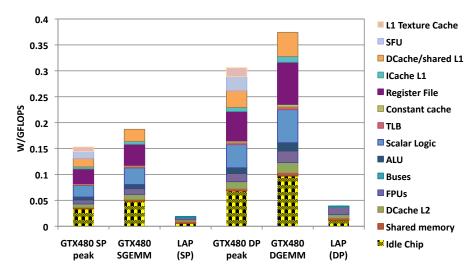

| 4.14. | Normalized power breakdown of Nvidia Fermi GTX480 versus LAP at 45nm                                                                                                            |

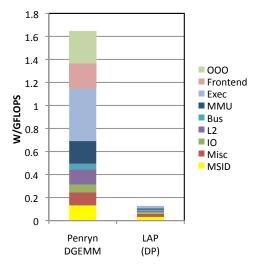

| 4.15. | Normalized power breakdown of Intel dual-core Penryn versus LAP at 45nm                                                                                                         |

| 4.16. | Comparison of efficiencies for single- and double-precisionbuses GEMM between NVidia Tesla GTX280, NVidia Fermi GTX480, Intel Penry and a LAP of equivalent throughput          |

| 5.1.  | Computing the SYRK of a $4 \times 4$ matrix. While it looks similar to the matrix-matrix multiplication in Figure 3.2, notice that each column of A needs to be transposed as the sequence of rank-1 updates is performed. | 85    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.2.  | Second iteration of a $4 \times 4$ SYRK on LAC                                                                                                                                                                             | 86    |

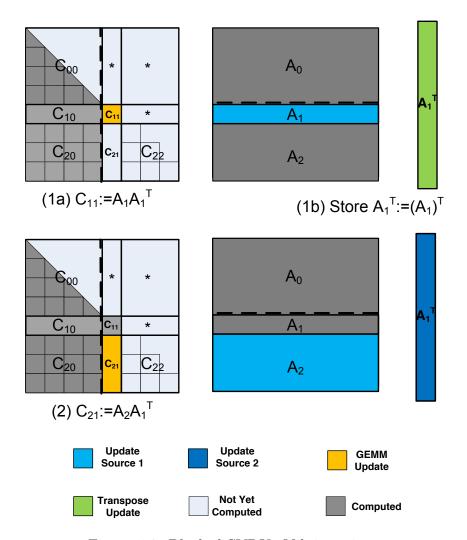

| 5.3.  | Blocked SYRK, fifth iteration.                                                                                                                                                                                             | 89    |

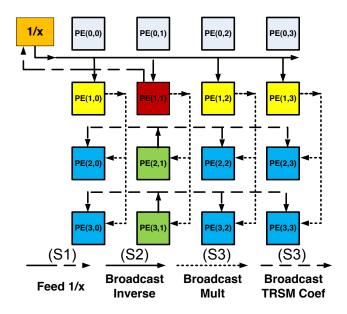

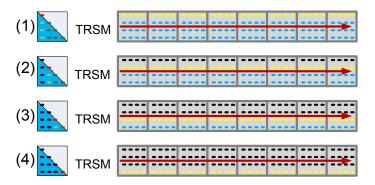

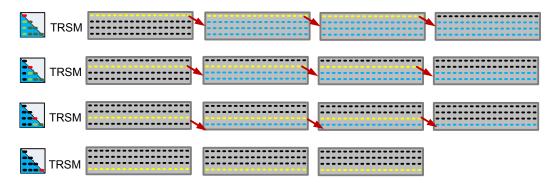

| 5.4.  | Second iteration of a $4 \times 4$ TRSM operation mapping on LAC.                                                                                                                                                          | 92    |

| 5.5.  | Overcoming the data dependency by pipelining TRSM operations. Eight blocks of $4 \times 4$ TRSMs are stacked in each of the four iterations to fill empty slots of an eight stage pipelined MAC unit                       | 94    |

| 5.6.  | TRSM operation mapping on LAC, increasing utilization by software pipelining four stacked TRSM operations                                                                                                                  | 95    |

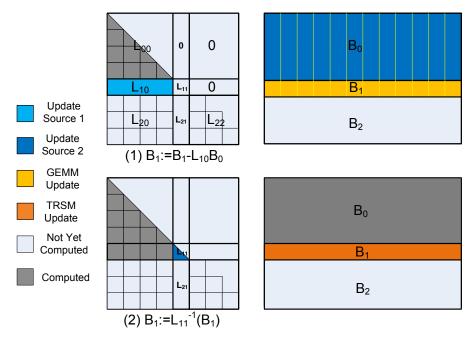

| 5.7.  | Blocked TRSM, fifth iteration                                                                                                                                                                                              | 97    |

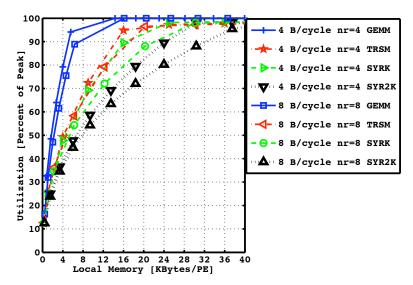

| 5.8.  | Estimated core performance for SYRK as a function of the bandwidth between LAC and on-chip memory, and the size of local memory with $n_r=4$ and $n_r=8$ , $m_c=k_c=256.$                                                  | 101   |

| 5.9.  | Estimated core performance for TRSM as a function of the bandwidth between LAC and on-chip memory, and the size of local memory with $n_r = 4$ and $n_r = 8$ , $m_c = k_c = 256$                                           | 101   |

| 5.10. | Utilizations for representative level-3 BLAS operations for $n_r = 4$                                                                                                                                                      | 4.102 |

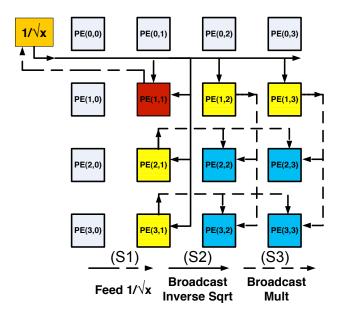

| 6.1.  | 4x4 Cholesky decomposition mapping on LAC, 2nd iteration.                                                                                                                                                                  | 109   |

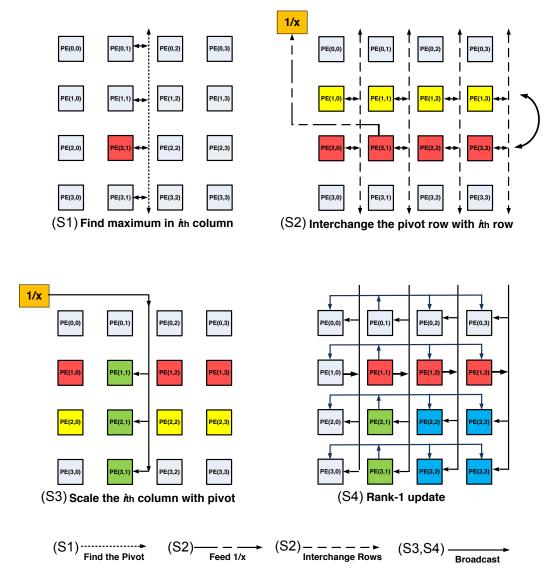

| 6.2.  | Second iteration of a $K \times n_r$ LU factorization with partial pivoting on the LAC                                                                                                                                     | 111   |

| 6.3.  | Operations and data manipulation in the second iteration of a $k \times n_r$ LU factorization inner kernel                                                                                                                 | 114   |

| 6.4.  | Mapping of the Vector Norm operation of a single vector stored in the third column of the LAC                                                                                                                              | 118   |

| 6.5.  | LAC area break-down with different divide/square-root extensions                                                                                                                                                           | 120   |

| 6.6.  | The effect of hardware extensions and problem sizes on the power efficiency of vector norm inner kernel                                                                                                                    | 121   |

| 6.7.  | The effect of hardware extensions and problem sizes on the power efficiency of LU factorization with partial pivoting inner kernel.                                                                                        | 121   |

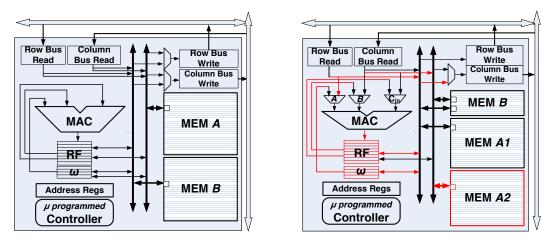

| 6.8. | New PE configurations for full-overlap FMA-optimized Radix-4 FFT: (left) FFT-optimized PE with two 8-byte, single-ported SRAMs, and (right) Hybrid PE with two 8-byte, single-ported SRAMs to contain matrix A                                                                                                                                                                                                                         | 128 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

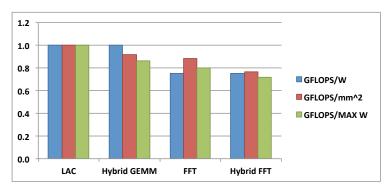

| 6.9. | Efficiency of different designs normalized to the original LAC design at 1 GHz                                                                                                                                                                                                                                                                                                                                                         | 129 |

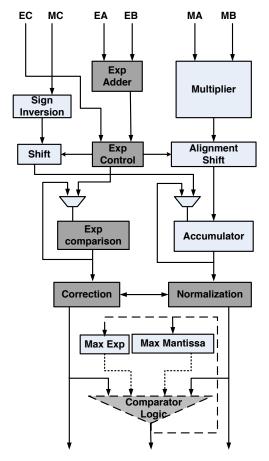

| A.1. | Extended reconfigurable single-cycle accumulation MAC unit [63] with addition of a comparator and extended exponent bit-width, where shaded blocks show which logic should change for exponent bit extension.                                                                                                                                                                                                                          | 143 |

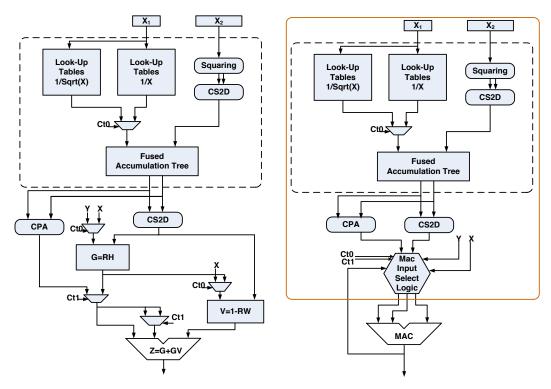

| A.2. | Floating-point unit extensions: (left) original divide, reciprocal, square-root and inverse square-root design with the Minimax logic [113] used for the isolate unit; (right) a single MAC unit design to support special functions. The overheads on top of an existing MAC unit are encapsulated in the big rounded rectangle. PEs in the LAC with that overhead can perform special functions.                                     | 147 |

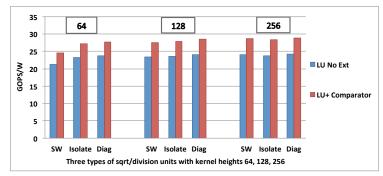

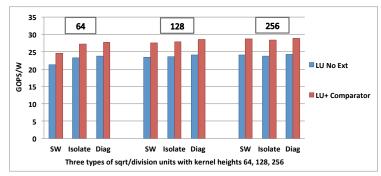

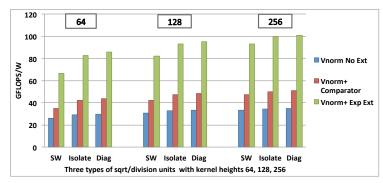

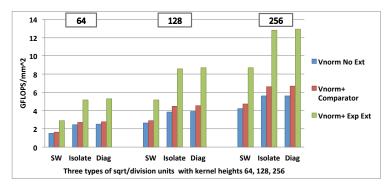

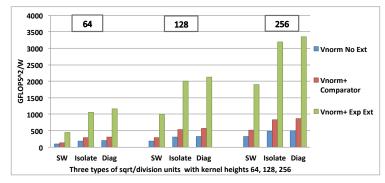

| A.3. | The effect of hardware extensions and problem sizes on the power efficiency of LU factorization with partial pivoting inner kernel.                                                                                                                                                                                                                                                                                                    | 153 |

| A.4. | The effect of hardware extensions and problem sizes on the area efficiency of LU factorization with partial pivoting inner kernel.                                                                                                                                                                                                                                                                                                     | 153 |

| A.5. | The effect of hardware extensions and problem sizes on the inverse E-D metric of LU factorization with partial pivoting inner kernel.                                                                                                                                                                                                                                                                                                  | 153 |

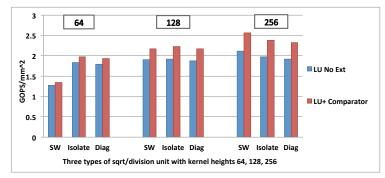

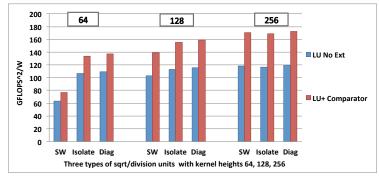

| A.6. | The effect of hardware extensions and problem sizes on the power efficiency of vector norm inner kernel                                                                                                                                                                                                                                                                                                                                | 156 |

| A.7. | The effect of hardware extensions and problem sizes on the area efficiency of vector norm inner kernel                                                                                                                                                                                                                                                                                                                                 | 156 |

| A.8. | The effect of hardware extensions and problem sizes on the inverse E-D metric of vector norm inner kernel                                                                                                                                                                                                                                                                                                                              | 156 |

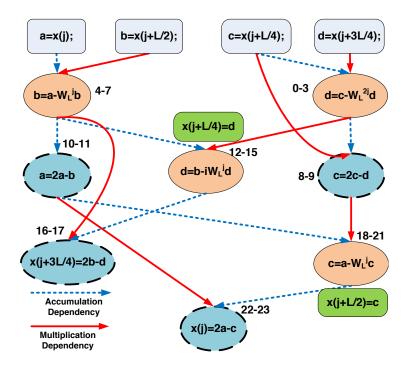

| B.1. | DAG of the optimized Radix4 Butterfly using a fused multiply-add unit. Rectangles on top indicate the input data, solid nodes show complex computations with four FMA operations each, nodes with dashed lines show complex computations with two FMA operations each. The nodes are executed in an order that avoids data dependency hazards due to pipeline latencies, as shown by the start-finish cycle numbers next to each node. | 163 |

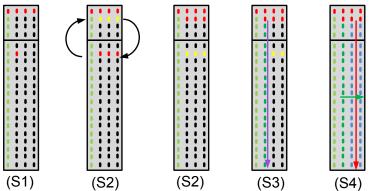

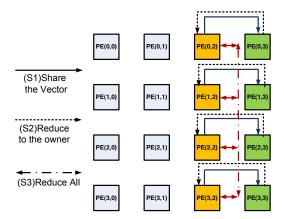

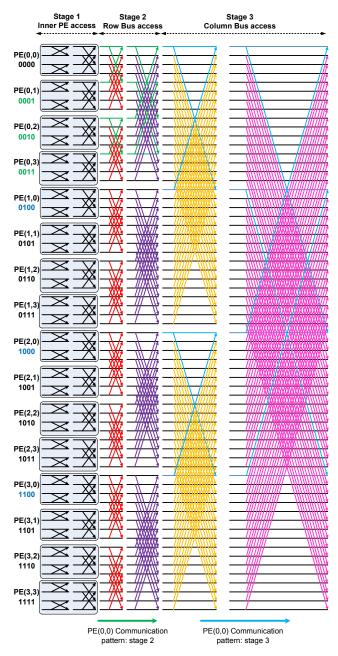

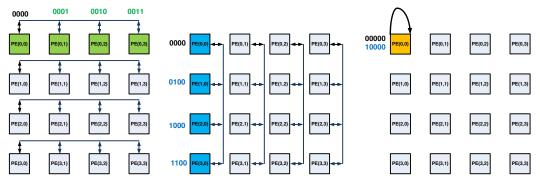

| B.2. | 64 point FFT performed by 16 PEs in the core. Each PE is performing Radix-4 Butterfly operations. The access patterns for PE(0,0) are highlighted. Stage 2 only utilizes row-buses to perform data communications. Stage 3 only utilizes column-buses to perform data communications | 166 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| В.3. | Data communication access pattern between PEs of the LAC for Radix-4 FFT                                                                                                                                                                                                             | 167 |

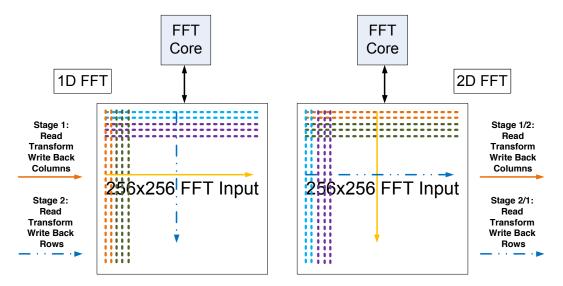

| B.4. | Overview of data motion to/from the core for performing a 64K 1D FFT (left), and for a $256 \times 256$ 2D FFT (right)                                                                                                                                                               | 169 |

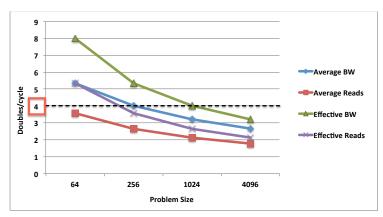

| B.5. | required bandwidth to support full overlap in the worst case for different problems. Note that four doubles/cycle is the maximum capacity of a core with column buses used for external transfers                                                                                    | 173 |

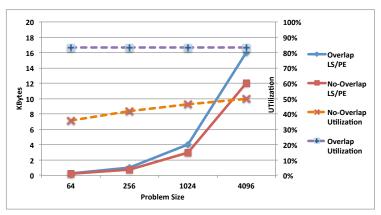

| B.6. | Local store/PE and respective utilization for both cases of non-overlap and overlapped solutions                                                                                                                                                                                     | 174 |

| B.7. | Average communication load on core for 64K 1D FFT                                                                                                                                                                                                                                    | 175 |

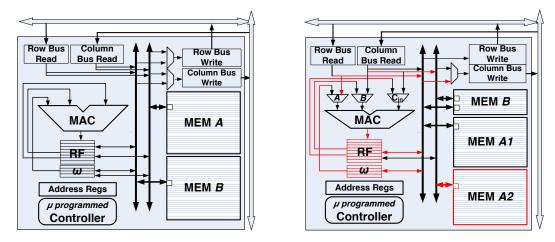

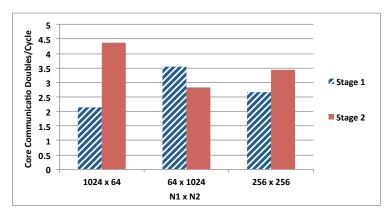

| B.8. | New PE configurations for full-overlap FMA-optimized Radix-4 FFT: (left) FFT-optimized PE with two 8-byte, single-ported SRAMs (right) Modified linear algebra PE with two 8-byte, single-ported SRAMs to contain matrix A ("Hybrid")                                                | 177 |

| B.9. | New core configurations with extended external row bus interface for full-overlap FMA-optimized Radix-4 FFT                                                                                                                                                                          | 178 |

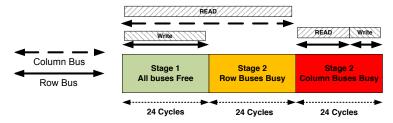

| B.10 | .Schematic of data bus usage for fully overlapped pre-fetch/post-store for the worst case of a 64-element FFT                                                                                                                                                                        | 181 |

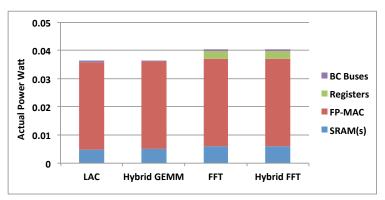

| B.11 | Actual PE power consumption of each design for target applications at 1GHz.                                                                                                                                                                                                          | 184 |

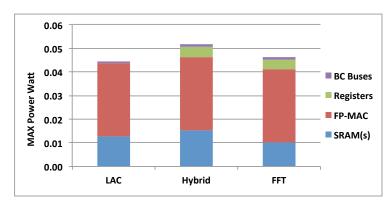

| B.12 | .Maximum PE power consumption of each target design at 1GHz. 184                                                                                                                                                                                                                     |     |

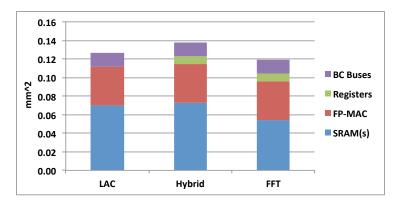

| B.13 | .Total area breakdown of the PE for each design                                                                                                                                                                                                                                      | 184 |

### Chapter 1

### Introduction and Background

Computer systems with the equivalent of 1 million to 10 million processing elements (e.g., cores) are on the horizon, heralding the age of exascale computing. This level of parallelism will be achieved by configuring computers as clusters on the macro level and, several layers down, in each processor exploiting VLSI technology that will allow on the order of 50 billion transistors to be packed onto a single chip [126]. In the past, we could rely on technology scaling to provide exponentially more and faster transistors in a constant area and at constant power with each new chip generation [31]. However, in the future only a fraction of this integration capacity can be utilized due to power constraints [36]. This provides the opportunity to integrate specialized cores that are only utilized when needed. At the same time, sustaining significant continued performance improvements will drive the need for optimization through specialization. One of the key questions going forward will be how to minimize, or at least greatly reduce, the power consumption while retaining or improving the achieved performance.

It is well known that full-custom, application-specific design of on-chip hardware accelerators, can provide orders of magnitude improvements in both power and performance for a wide variety of application domains [55, 154]. The flexibility provided by the programmability of general-purpose machines comes with inherent overhead. By contrast, in application-specific designs implementations are hardwired to directly realize the desired computation in fixed hardware. This is possible in domains such as embedded or mobile computing where applications are standardized and exponentially growing costs of chip design can be reaped across a large volume of units. The question is whether these concepts can be applied to a broader class of more general applications.

#### 1.1 Thesis Statement

Modern processors often integrate application-specific IP cores to meet power restrictions of the dark silicon era. However, each Application-specific IP core is limited to only one or a few applications/routines because the cost of extra flexibility is substantial loss in efficiency.

An accelerator design without instruction pipeline or register file, and optimized for matrix multiplication supports enough flexibility to perform level-3 BLAS, matrix-factorizations, other complicated linear algebra operations, and FFTs only by exploiting the competence of algorithm/architecture codesign. It is conjectured that such a design with all of the mentioned flexibility maintains at least an order of magnitude better power and area efficiency compared to current existing programmable architectures.

The broader vision of this project that goes beyond this dissertation

is to develop integrated and specialized hardware/software solutions that are co-optimized and co-designed across all layers ranging from the basic hardware foundations all the way to the application programming support through standard linear algebra packages. We study upper limits on performance/power ratios that can be achieved, and fundamentally investigate both limitations in current architectures and opportunities for targeted improvements in future architectures that are specially designed to efficiently support this crucial class of operations.

### 1.2 Linear Algebra Processor Overview

We target an ASIC implementation that will allow us to fully exploit state-of-the-art technologies instead of programmable hardware like FPGAs. Within this context, our goal is to develop a fixed Linear Algebra Processor (LAP) architecture that avoids inefficiencies of general-purpose processors and GPUs. We remove the overheads of program pipeline and rearrange processing elements in a more efficient way. Finally, in contrast to full custom specialized accelerators, our architecture is flexible enough to optimally execute different matrix operations, but with the same level of efficiency.

We recognize that our class of linear algebra operations essentially consists entirely of Multiply-Accumulate (MAC) computations with regular and predictable, looping access patterns. As such, we design a datapath that consists of specialized MAC units, which include local accumulators to avoid the need for unnecessary transfers to/from the register file in every operation.

We build on the SIMD concept of replicating Functional Units (FUs) to exploit parallelism; instead of communicating through shared storage, wasting cycles and instructions, our approach is based on partitioned and distributed memories local to each FU. Memory hierarchies and interconnects are specifically designed to realize available locality and required access patterns with efficient reuse as well as careful prefetching of data that moves between memory layers. Control is predominantly hardwired with a minimal set of micro-coded commands to switch between different processing modes.

A taxonomy of accelerators and the possible programming models in accelerator systems is proposed by Cascaval et al. [21], which we will discuss further in the related work. Here, we classify the LAP along this design space taxonomy. Based on all of the possible choices in the design space of accelerators, [21] introduces a classification across three dimensions. The following summarizes the possible choices and where the LAP design stands in this design space.

- 1. Architecture type: Fixed architectures such as Floating-Point Units (FPUs), programmable architectures like GPUs, or reprogrammable architectures like FPGAs are the possible choices. Our proposed architecture is reprogrammable and flexible so it can handle variety of linear algebra problems by microprogrammed control.

- 2. **Invocation and Completion**: There is a correlation between the invocation granularity and the coupling of the accelerator to the host sys-

tem. In instruction-level invocation, Streaming SIMD Extensions (SSE) or FPUs are invoked as a part of the Instruction Set Architecture (ISA). In command packet invocation, an accelerator is connected as a device with memory mapped I/O, and its invocation is asynchronous. In task-level invocation, the accelerators are programmable standalone systems with coarse-grain invocation and are typically asynchronous. Finally, workload systems are standalone systems connected to the host through a network and perform the entire tasks offline.

The invocation granularity of our LAP is coarse-grain at the task level to maintain maximum utilization of the host processor. The host could assign a series of tasks on the same data without interfering in between. The LAP interrupts the host when the result matrix is ready.

3. **Memory Addressing**: Memory addressing determines whether the address space of the host is shared with the accelerator. Memory partitioning shows if the accelerator's addressable memory is completely distributed, shared with, or hidden from the CPU. Possible coherency of address spaces with the CPU or other devices is an option.

The LAP's memory address space could be shared or separated from the CPU memory; it depends on the granularity and the complexity of tasks. In case of multiple LAPs, we need to schedule them in a shared memory environment. We avoid cache coherency overheads in our solution.

Figure 1.1: A single Linear Algebra Core (LAC) in LAP Architecture, SFU is Special Functional Unit.

#### 1.2.1 Architecture

In contrast to the conventional 1D arrangement of FUs in SIMD architectures, we use row and column buses in a 2D arrangement of PEs as illustrated in Figure 1.1. Each Processing Element (PE) contains a MAC unit, SRAM Local Storage (LS), a microprogrammed controller, and necessary datapath. Each PE is connected to all of the PEs in the same row and in the same column via corresponding row and column broadcast buses, respectively. A Special Functional Unit (SFU) performs special functions such as divide and square-root operations. Cores are connected to the on-chip shared memory and their own dedicated on-chip memory bank and communicate data in and out using column broadcast buses.

We will see in Chapter 3 that this arrangement naturally maps a ma-

Figure 1.2: LAP programming environment.

trix multiplication kernel using broadcast buses, and it eliminates the need for communication through a register file by fully exploiting the communication network. By distributing the control, we also remove the overheads of control and unnecessary data communication between processing elements. Further, we exploit the concept of separating the memory interface and intra-PE communication interface by streaming the data through a particular channel to the core.

### 1.2.2 Programming model

Figure 1.2 shows how a linear algebra application can employ a LAP. Linear algebra (LA) libraries, such as the libflame [138, 139] and LAPACK [12]

support built-in software layers that decompose big problems into smaller subproblems with so-called algorithms-by-blocks [90]. Routines with higher level functionality (e.g., a LU factorization) are called from the host application. The LA library's internal routines break the large problem recursively into smaller, simpler subroutine calls to Basic Linear Algebra Subroutines (BLAS) and communication & packing routines, until the problems reach a certain size. These small problems (for example  $128 \times 128$ ) are atomic units of data with which atomic computations are performed. On a typical general-purpose CPU, these kernels are all implemented very efficiently, often in target machine assembly code [52]. One can view the LAP as an accelerator for these atomic kernel operations and the atomic size of the kernels depends on the LAP-supported kernel sizes. Instead of calling the assembly-coded kernel on the host processor, necessary information including the data location address and type of operation to be performed is passed to the LAP through the device driver. After finishing the operation, the LAP puts the computed data back in the memory. The LAP can overlap the communication with computation by pipelining multiple operations.

### 1.3 Evaluation Methodology

We have developed both simulation and analytical power and performance models of the LAP in comparison with other architectures. We validated the performance model and LAP operation in general by developing a cycle-accurate LAP simulator. The simulator is configurable in terms of PE

pipeline stages, bus latencies, and memory and register file sizes. Furthermore, by plugging in power consumption numbers for MAC units, memories, register files, and buses, our simulator is able to produce an accurate power profile of the overall execution. We accurately modeled the cycle-by-cycle control and data movement for GEneral Matrix-matrix Multiplication (GEMM), TRiangular Solve with Multiple Right-hand Sides (TRSM), and Cholesky factorization, and we verified functional correctness of the produced results. The simulator provides a testbed for future investigation of other linear algebra operations.

#### 1.3.1 Performance Analyses

Linear algebra applications have predictable memory access behavior and the custom-designed LAP architecture does not contain caches or any other processing units with non-deterministic behavior. Therefore, one can model the data movement and access patterns with analytical formulae. We have verified our analytical formulae against our in-house cycle-accumulate simulator for some of the applications. We derived the analytical formulae in two different ways and matched the answers to bolster our confidence in their the correctness. We derived the results first from inside of the core to the next levels of the memory hierarchy as problem size grows, and then from lower levels of memory hierarchy perspective into the core as problem size shrinks.

#### 1.3.2 Component selection

To investigate and demonstrate the performance and power benefits of the LAP, we have studied the feasibility of a LAP implementation in current bulk CMOS technology using publicly available components and their characteristics as published in the literature.

State-of-the-art implementations of Fused Multiply Add (FMA) units use various optimization techniques to reduce latency, area and power consumption [117]. Fused Multiply Accumulate (FMAC) units with delayed normalization achieve a throughput of one accumulation per cycle [141, 142] and save around 15% of total power [63]. The number of pipeline stages typically ranges between 5 and 9 and the same FMAC units can be reconfigured to perform either integer, single-, or double-precision operations [132]. A precise and comprehensive study of different FMA units across a wide range of both current and estimated future implementations, design points and technology nodes was presented in [43].

Our design utilizes SRAM storages with no tags and no associativity. Given the sequential nature of access patterns to 64-bit wide double-precision numbers, we carefully selected memories with one or two banks to minimize power consumption by using CACTI [93] memory simulator. The optimized choice is the low-power ITRS technology model and aggressive interconnect projection.

To estimate latencies and power consumption of row and column buses,

we use data reported in CACTI. Since the LAP does not require complex logic for bus arbitration and address decoding, we only consider the power consumption of the bus wires themselves.

For the overall system estimation, we project the dynamic power results reported by CACTI to the target frequencies of the MAC units. According to the CACTI low-power ITRS model, leakage power of the memory blocks is estimated to be negligible in relation to the dynamic power. When more bandwidth is needed for the on-chip memory, the technology changes into a faster model and the leakage power ratio increases.

### 1.3.3 Power Modeling of Architectures

We developed a general analytical power model that builds on existing component models (e.g. for FPUs and memories) described in the previous section. The model is derived from methods described in [20,88] and we applied it to both our LAP and various existing architectures. Our power model computes the total power as the sum of the dynamic power and idle power over all components in the architecture:

$$Power = P_{dyn} + P_{idle} = \sum_{i=1}^{n} (P_{dyn,i}) + \sum_{i=1}^{n} (P_{idle,i})$$

$$P_{dyn,i} = P_{max,i} \times activity_{i}$$

$$P_{idle,i} = P_{max,i} \times ratio.$$

Dynamic power is modeled as a maximal component power multiplied by the component's activity factor. We estimate activity of memory components based on access patterns for matrix multiplications. Otherwise, we assume activity factors of one or zero depending on whether a component is utilized during the targeted operations. For leakage and idling, we use a model, derived from calibrations, that estimates idle power as a constant fraction of dynamic power ranging between 25% and 30%, depending on the technology used.

We calibrate our power model and its parameters against power and performance numbers presented for the NVidia GTX280 Tesla GPGPU when performing matrix multiplication [60, 149]. We used the sizes of different GPU memory levels reported in [149] together with numbers from [60] and [4] to match logic-level, FPU, CACTI and leakage parameters and factors in order to achieve consistent results across published work and our model. We then apply this model to other architectures, such as the NVidia GTX480 Fermi GPGPU [2,68] or the Intel Penryn [47] dual-core processor. To the best of our knowledge, there are no detailed power models yet for these architectures. We adapted our model to the architectural details as far as reported in literature using calibrated numbers for basic components such as scalar logic, FPUs or various memory layers. In all cases, we performed sanity checks to ensure that total power numbers match reported numbers in literature.

### 1.4 Contributions

The main contributions of this dissertation are as follows:

1. The design, simulation, and power estimation of a highly optimized linear

algebra core for matrix computations.

- 2. A multi-dimensional design space exploration of a multi-core linear algebra processor for the GEMM algorithm.

- 3. An analytical tool for evaluating the memory hierarchy size and bandwidth balance for linear algebra operations.

- 4. A thorough study of the behavior of level-3 BLAS operations across the linear algebra core and conventional SIMD architectures.

- 5. A generalization of the base architecture to support all level-3 BLAS and important matrix factorizations.

- 6. The power and performance details for PE and floating-point unit extensions to support special functions for divide and square-root operations.

- 7. A study of Fast Fourier Transform (FFT) operation in contrast with GEMM operation and the corresponding algorithm/architecture tradeoffs.

- 8. A design of a Hybrid FFT/Linear Algebra core with minimum loss in efficiency.

Together, these advance the state-of-the-art in this domain.

## 1.5 Thesis Outline

The rest of this dissertation is organized as follows. In Chapter 2, we present an overview and analysis of the state-of-the-art conventional and custom designed architectures. In Chapter 3, we introduce the linear algebra core (LAC) design, using matrix multiplication as a driving example, and report the estimated area, power, performance, and efficiency of the core for that operation. In Chapter 4, we develop a multi-LAC system and discuss trade-offs for matrix multiplication at different levels of the memory hierarchy. We demonstrate the potential for flexibility and support of level-3 BLAS kernels on the linear algebra core in Chapter 5. Chapter 6 discusses generalization opportunities by showing how more complicated linear algebra and signal processing algorithms like matrix factorizations and FFT, can be mapped to the LAC. We summarize the dissertation and discuss future goals in Chapter 7.

In Appendix A the details of matrix factorization algorithms are discussed. Appendix B provides the details of the algorithm and mapping for FFT operation on the LAC.

# Chapter 2

## Related Work

Matrix-matrix multiplication and related kernels are of interest because these operations are often what deliver high-performance to many crucial applications [120]. Key to a successful implementation are insights related to the optimal exploitation of parallelism and locality in general-purpose processors [52], GPUs [133, 143], and other examples of parallel architectures [141]. These insights can have a greater impact if directly applied to the co-design of algorithms and architectures.

Within the domain of linear algebra computations, it is well understood that many problems can be efficiently reduced down to a canonical set of Basic Linear Algebra Subroutines (BLAS), such as matrix-matrix operations (level-3 BLAS) and matrix-vector operations (level-2 BLAS). The response to this has been the definition of interfaces to these key operations [32, 33, 85], and high-performance libraries that are layered upon the BLAS, like the Linear Algebra Package (LAPACK) [12] and, more recently, the libflame library [138, 139]. As a result, the time to solution for the complete application is often heavily dictated by the performance of dense linear algebra operations with relatively small matrices (e.g., of size  $100 \times 100$  to  $10,000 \times 10,000$ ). If one improves

the performance and/or reduces the power consumption of such operations at the node or core level, all applications potentially benefit.

In the following, we will briefly re-examine traditional general-purpose architectures, vector extension architectures, and GPGPUs, with a discussion of their strengths and sources of overhead specifically when performing matrix computations. Next, we focus on accelerator designs and discuss their architectures. This provides the basis for developing our proposed matrix processor architecture aimed at removing such inefficiencies.

## 2.1 General-Purpose Processors

A general-purpose data path, illustrated in Figure 2.1, executes computation by repeatedly reading operands from storage, performing ALU operations on them, and writing results back to register files. In order to provide flexibility and generality, functional units are typically only provided for basic operators, and every sequence of two or more operations has to go through the register file and interconnect. In many modern general-purpose CPUs, only 15%-25% of the area and power consumption is actually dedicated to Functional Units (FUs) [1,11]. The rest is spent on aggressive superscalar, out of order execution, and multi-threading techniques to recover instruction-level parallelism out of a serialized instruction stream, and keep the FUs utilized. Furthermore, with unknown sequences of operands, the storage and interconnect has to be effectively designed for random access patterns.

A CPU takes advantage of temporal and spatial locality to reduce de-

mand on the remote slow DRAM. It supports complex memory hierarchies and multiple levels of caches to provide local high bandwidth to the core. Speculative prefetching, and associated bookkeeping and prediction overheads, are often employed to keep the core utilized. In the lowest level of memory hierarchy data access through multi-port register files is expensive and can become the bottleneck [121]. In higher levels of hierarchy, complexity of tag handling and address decoding in caches limits the size available for actual data storage. For example, in large data sets such as matrices the bulk of data is stored in higher levels of the hierarchy. While deep caching allows general-purpose architectures to recover enough locality and hence parallelism to keep their FUs busy, extraneous transfers to bring data in and out from/to far memories consume a large amount of energy, often far more than that used for computing with the data.

The costs for increased single-threaded performance gains have reached the point where old techniques incur tremendous overhead [55] and outweigh the benefits of any further improvements. Even more importantly, technology scaling is also reaching physical limits. Additional transistors will only be provided at reduced performance and increased power consumption [46, 61].

General matrix multiplication (GEMM) implementation on traditional general-purpose architectures has received a lot of attention [3, 8, 51, 118, 146]. However, general instruction handling overhead remains and, even with SIMD instructions, long computations have to be split into multiple operations that exchange data through a wide register file.

Figure 2.1: (a) A typical general-purpose processor memory hierarchy and core architecture.

### 2.1.1 SIMD ALUs and Vector Processors

Adding vector units to conventional processors has been a solution to increase efficiency of CPUs [38,39]. Modern CPUs include Single-Instruction Multiple-Data (SIMD) vector units, such as Intel's Streaming SIMD Extensions (SSE) [119]. In a SIMD solution, the data path contains multiple FUs of the same type that can simultaneously perform a single operation on multiple data items. SIMD processors exploit data parallelism while reducing the number of instructions, which is particularly beneficial for matrix operations. A taxonomy of register file architectures is presented in [121]. Along three main dimensions: data-parallel, instruction level parallel, and memory hierarchy resulting into 12 different organizations, each organization shows different behaviors in terms of area, power, and delay.

Three main limitations of conventional vector architectures are known

to be (1) complexity of central register file; (2) implementation difficulties of precise exception handling; and (3) expensive on-chip memory [75]. Although the throughput has increased in these architectures, basic instruction handling overhead still remains and fused operations like multiply-accumulate still have to be performed in multiple instructions that exchange data through a shared register file or, when spilled, through the memory. Associated costs are amplified by the fact that in each step a complete vector has to be transferred through multiple ports of a register file, wide wires, and complex point-to-point interconnects such as crossbars. CODE architecture [75] is designed around a clustered vector register file with decoupled interconnect trying to overcome these inherent limitations.

In recent years several projects were dedicated to evaluation and optimization of vector architectures. Tarantula [37] is an alpha EV8 architecture with vector unit capable of 32 FLOPs per cycle. The vector and multithreaded compute models are unified in the SCALE [76] vector-thread architecture. The vector architectures are compared with conventional superscalar and VLIW architectures for multimedia benchmarks in [74]. Energy-efficiency potentials of vector accelerators for high performance computing systems are discussed in [86]. The efficiency of an architecture depends on the organization of the SIMD units and how they are employed with regard to instruction pipeline and memory hierarchy. In the rest of this section we present examples of the different architectures based on SIMD concept and their different power and performance features.

Figure 2.2: Modern GPU core, and memory hierarchy architecture.

### 2.1.2 **GPGPUs**

Graphical Processing Units (GPUs) have recently shifted away from specialization to providing general-purpose computing capabilities. While this makes such General-Purpose GPUs (GPGPUs) interesting for a wider class of applications, the added flexibility invariably re-introduces overhead. Apart from some remaining special graphics FUs, GPGPUs essentially replicate a large number of SIMD processors on a single chip. To provide matching locality, SIMD processors are clustered into groups that share common levels of the memory hierarchy. Their pipeline is kept simple with no branch prediction or out-of-order execution but multithreading is used in GPU cores to hide long memory access latency. However, inherent characteristics and deficiencies of a SIMD processor remain.

A typical GPU today, shown in Figure 2.2, has 64Kbytes or more of local storage per core to keep the execution context. A read-only texture cache has been a part of GPUs. Modern GPUs like Nvidia Fermi [2] and

Intel Larabee [125] have recently supported the memory cache hierarchy but their on-chip cache size is relatively small (around 0.5 Mbytes). Although GPUs support high bandwidth DRAM organizations like DDR3-5 with wide 150 Gbytes/sec bus, their bandwidth to computation ratio is still much lower than CPUs. As a result GPUs have to carefully schedule memory requests to efficiently use the available bandwidth.

GPUs were originally developed as specialized hardware for graphics processing that provided massive parallelism but were not a good match for matrix computations because they did not support enough data throughput to computation ratio [40]. In recent years, GPUs have become a popular target for acceleration.shifting back towards general-purpose architectures. Such GPGPUs replicate a large number of Single Instruction Multiple Data (SIMD) processors on a single shared-memory chip. GPGPUs can be effectively used for matrix computations [10, 143] with throughputs of more than 300 GFLOPS for Single-precision GEMM (SGEMM), utilizing around 30-60% of the theoretical peak performance. In the latest GPGPUs, two single-precision units can be configured as one double-precision unit, achieving more than 700 singleprecision and 350 double-precision GFLOPS at around 70% utilization [133] for matrices larger than  $512 \times 512$ . Even when ignoring the power consumption of components such as texture caches or special functional units (SFUs), actual GEMM efficiencies in terms of GigaFlops/Watt are an order of magnitude lower than what is inherently possible. Later in this dissertation we will address the causes of this inefficiency.

The main difference between LAP and GPU design lies with the communication through a shared context and instruction handling in the GPU cores. Multithreading to hide memory latencies also adds overhead for GPU cores. In the same manner as in GPGPUs with shared on-chip memory, LAP basic cores can in the future be replicated and dropped into a larger linear algebra processor arrangement.

## 2.2 Custom Design Architectures and Accelerators

Accelerators are "specialized functional units integrated with the core, specialized cores, attached processors, or attached appliances" [21]. They are tuned to provide low power, low cost, higher performance, and less development, while maximizing throughput per unit area of silicon. An accelerator does not function on its own; it requires invocation from host programs [103,112]. The strategy is specialization and it cannot be used as a "general-purpose" compute engine. A sustainable accelerator model requires an application domain where "too much performance is never enough" [103]. These domains are open to an accelerator-based solution for which a combination of parallelism, pipelining, and regularity of computation is necessary. "The single-thread performance reduction of Moore's law makes accelerators economically viable to a degree they have never been before" [112]. Since parallelizing the code is far from trivial in the case of multithreaded solutions, avoiding it by direct hardware implementation may be a major benefit of accelerators.