Dependence-Aware **Transactional Memory for** Increased Concurrency Hany E. Ramadan, Christopher J. Rossbach, Emmett Witchel University of Texas, Austin

#### Concurrency Conundrum

- Challenge: CMP ubiquity

- Parallel programming with locks and threads is difficult

- deadlock, livelock, convoys...

- lock ordering, poor composability

- performance-complexity tradeoff

- Transactional Memory (HTM)

- simpler programming model

- removes pitfalls of locking

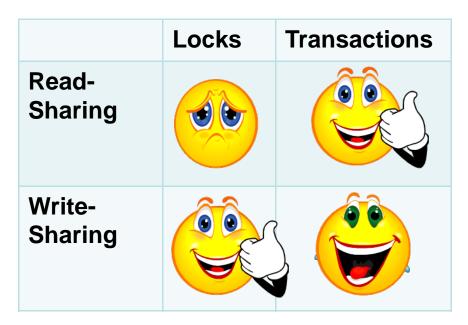

- coarse-grain transactions can perform well *under lowcontention*

#### High contention: optimism warranted?

- TM performs poorly with write-shared data

- Increasing core counts make this worse

- Write sharing is common

- Statistics, reference counters, lists...

- Solutions complicate

programming model

- open-nesting, boosting, early release, ANTs...

Dependence-Awareness can help the programmer (transparently!)

## Outline

- Motivation

- Dependence-Aware Transactions

- Dependence-Aware Hardware

- Experimental Methodology/Evaluation

- Conclusion

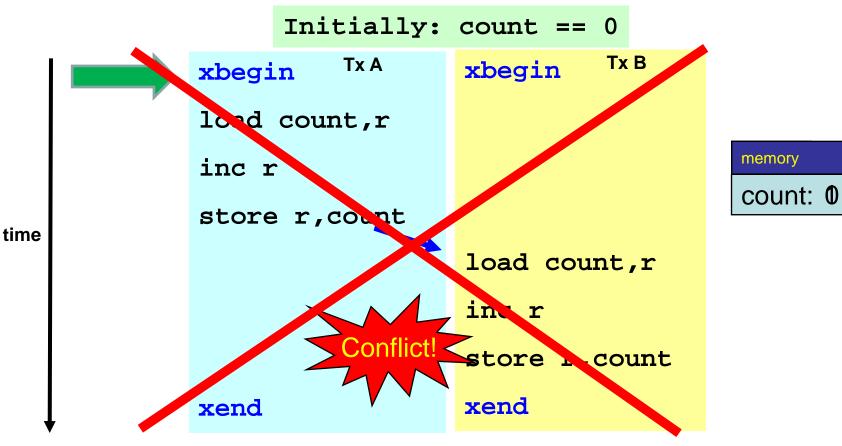

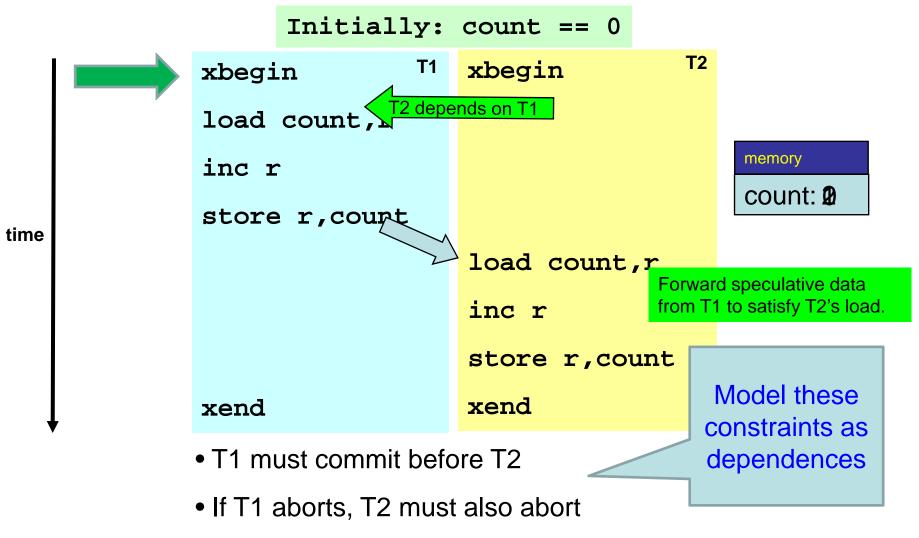

#### Two threads sharing a counter

Initially: count == 0

|      |   | •••    | Thread A |       |        | Thread B |                 |

|------|---|--------|----------|-------|--------|----------|-----------------|

|      | ٢ | load c | ount,r   |       |        |          |                 |

|      |   | inc r  |          |       |        |          | memory          |

| time |   | store  | r,count  |       |        |          | count: <b>2</b> |

|      |   |        |          | load  | l coun | it,r     |                 |

|      |   |        |          | inc   | r      |          |                 |

|      |   |        |          | stor  | e r,c  | ount     |                 |

|      | T | •••    |          |       |        |          |                 |

| •    |   |        | Result:  | count | == 2   |          |                 |

#### Schedule:

- dynamic instruction sequence

- models concurrency by interleaving instructions from multiple threads<sup>5</sup>

#### TM shared counter

• both transactions access a datum, at least one is a write despite the fact that they yield the correct result!

• intersection between read and write sets of transactions

#### Does this really matter?

| xbegin Critsec A                       | xbegin Critsec B                            |                                                                                                         |

|----------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|

| <lots of="" work=""></lots>            | <lots of="" work=""></lots>                 |                                                                                                         |

| load count,r<br>inc r<br>store r,count | <pre>load count,r inc r store r,count</pre> | <b>Common Pattern!</b> <ul> <li>Statistics</li> <li>Linked lists</li> <li>Garbage collectors</li> </ul> |

| xend                                   | xend                                        |                                                                                                         |

**DATM: use dependences to commit conflicting transactions**

#### DATM shared counter

• If T1 overwrites count, T2 must abort

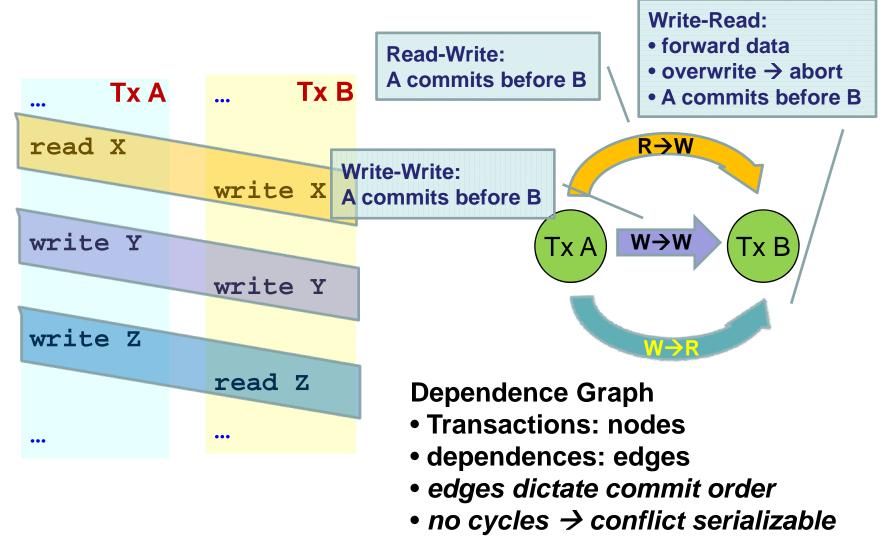

#### **Conflicts become Dependences**

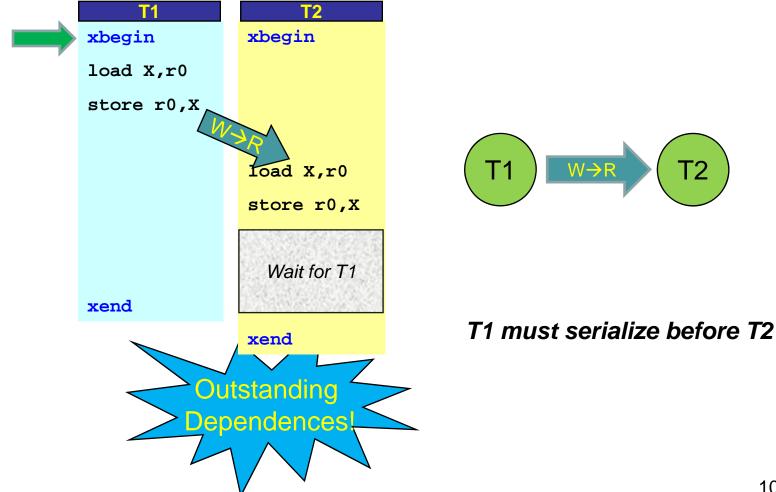

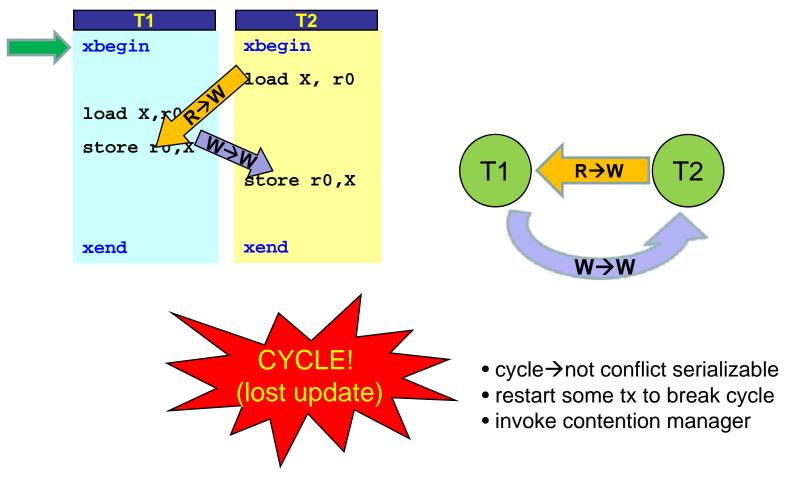

## Enforcing ordering using **Dependence Graphs**

## Enforcing Consistency using Dependence Graphs

#### **Theoretical Foundation**

Correctness and optimality /: results of Proof: See [PPoPP 09]

**2-**p

Imp

equivalent

#### **Serializable**

| Co  | Dependence                | Forward | Restart                                                    |

|-----|---------------------------|---------|------------------------------------------------------------|

|     | $W_0 \rightarrow W_1$     | No      | If in cycle                                                |

| ope | $R_0 \!\rightarrow\! W_1$ | No      | If in cycle                                                |

| ope | $W_0 \rightarrow R_1$     | Yes     | If in cycle, and $T_1$<br>must if either: <b>a</b> ) $T_0$ |

| Со  |                           |         | does. <b>b</b> ) $T_0$ overwrites forwarded data with      |

| equ |                           |         | new value.                                                 |

(LogTM, TCC, RTM, MetaTM, OneTM...

ientation of CS

respectives, and acrive (h) the set of acrive (act committed x aborted) transactions. If x is a variable, prior(x,h) is the et of acrive transactions that have read or written x in  $h_i$ iters(x, h) the active or committed transaction that most ently wrote x in h, and value(x, h) the value it wrote. ition A.1. A history h is atomic if committed(h) is lient to a legal failure-free serial history.

rial(b) be the setial history equivalent to committee transactions appear in the order of their commit

ney control mechanism can be thought of as rect if those histories are atomic. We now de

of T can o T), the set of to anactions that an

Post:  $h' = h \cdot (T \text{ abort})$ on captures the effects of deadlock detection. mition captures use exactly interest. Auct or inseract (that is, timecont). As a transaction T read, we track the write-read de T ∈ active(h) Post:

h' = h · (T, x, read(value(x, h))))

ourlier'(T) = ourlier(T) ∪ (serifers(x, b)).

When a transaction writes, we track its read-write and s-write dependencies on the active transactions that read-route that variable. Por T & active Post: and also if  $T_0 \in notLater(T_1)$ .

rite(v))  $notLater(T) \cup prior(v, k)$ , mit only if every value it read

there are interested in the

Lemma A.1. Let  $w_b$  be a write event by  $T_b$ , and  $e_b$  either a read or write event by  $T_b$ , bock to a surfable x in h,  $h'w_b$ precedes  $e_i$  in serial(h), then  $w_b$  precedes  $e_i$  in h.

Proof Suppose instead that  $e_1$  precedes  $w_0$  in h. B they were recodered T<sub>2</sub> and T<sub>2</sub> were both active wi ended to history h. It follows that T. c pr implying that T. a re To, ordering as before so in sevial h)

nma A2. Let h be a h To, r.s. a read event by T1 that return

ay of contradiction, the property becomes viol step. That step must be the commit of a tran scause the other steps leave sevial(A) unchange

ad, there can be no wy by Ty between

cent write event in a

12

# Outline

- Motivation/Background

- Dependence-Aware Model

- Dependence-Aware Hardware

- Experimental Methodology/Evaluation

- Conclusion

## **DATM Requirements**

Mechanisms:

- Maintain global dependence graph

- Conservative approximation

- Detect cycles, enforce ordering constraints

- Create dependences

- Forwarding/receiving

- Buffer speculative data

Implementation: coherence, L1, per-core HW structures

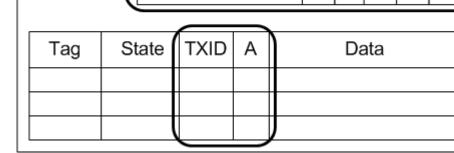

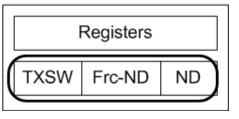

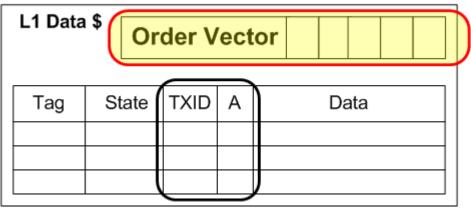

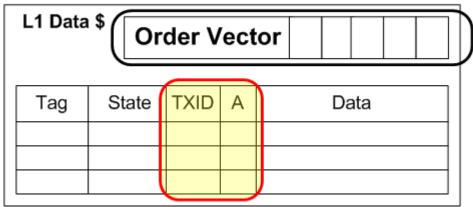

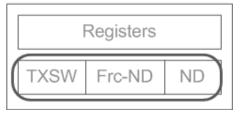

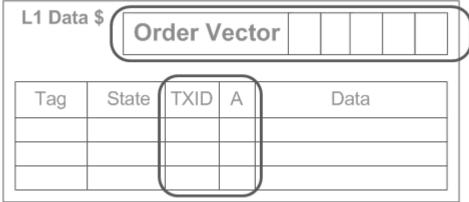

#### • Order vector: dependence graph

- **TXID**, access bits: versioning, detection

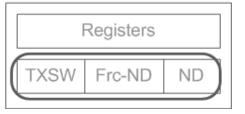

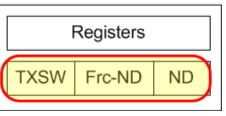

- TXSW: transaction status

- **Frc-ND + ND** bits: disable dependences

# L1 Cache Controller

**Processor Core**

These are not programmer-visible!

#### Order vector:

- dependence graph

- topological sort

- conservative approx.

#### L1 Cache Controller

**Processor Core**

- Order vector: dependence graph

- **TXID**, access bits: versioning, detection

- TXSW: transaction status

- Frc-ND + ND bits: disable dependences

#### L1 Cache Controller

**Processor Core**

These are not programmer-visible!

- Order vector: dependence graph

- **TXID**, access bits: versioning, detection

- TXSW: transaction status

- **Frc-ND + ND** bits: disable dependences, no active dependences

- Processor Core

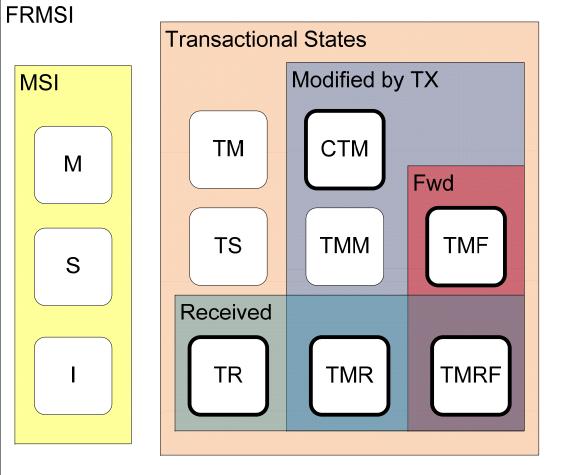

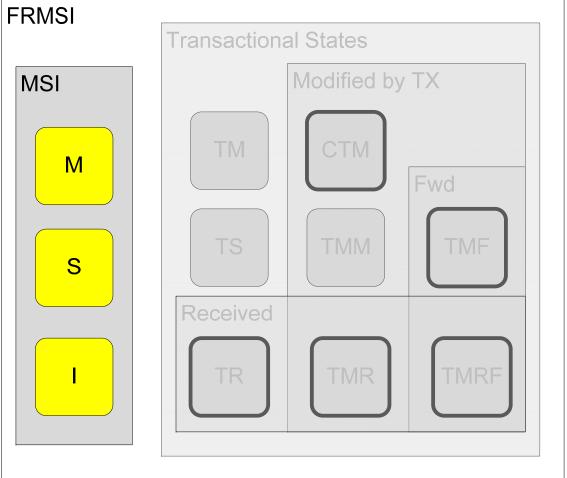

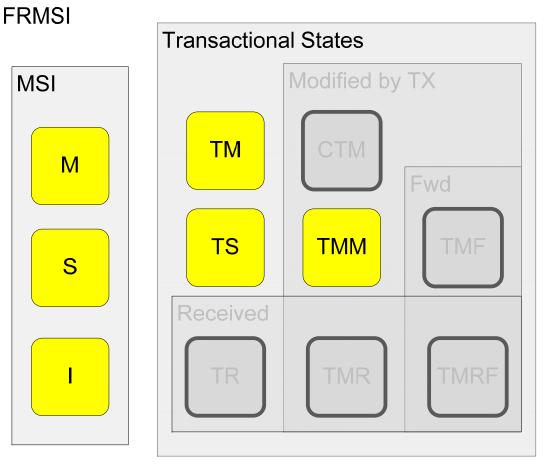

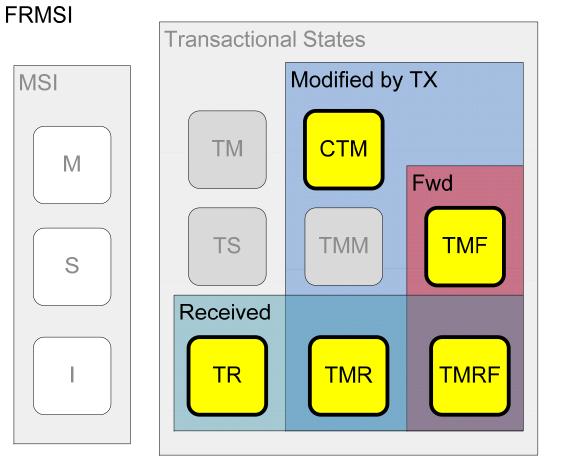

#### L1 Cache Controller

- MSI states

- TX states (T\*)

- Forwarded: (T\*F)

- Received: (T\*R\*)

- Committing (CTM)

- Bus messages:

- TXOVW

- xABT

- xCMT

- MSI states

- TX states (T\*)

- Forwarded: (T\*F)

- Received: (T\*R\*)

- Committing (CTM)

- Bus messages:

- TXOVW

- xABT

- xCMT

- MSI states

- TxMSI states (T\*)

- Forwarded: (T\*F)

- Received: (T\*R\*)

- Committing (CTM)

- Bus messages:

- TXOVW

- xABT

- xCMT

- MSI states

- TX states (T\*)

- Forwarded: (T\*F)

- Received: (T\*R\*)

- Committing (CTM)

- Bus messages:

- TXOVW

- xABT

- xCMT

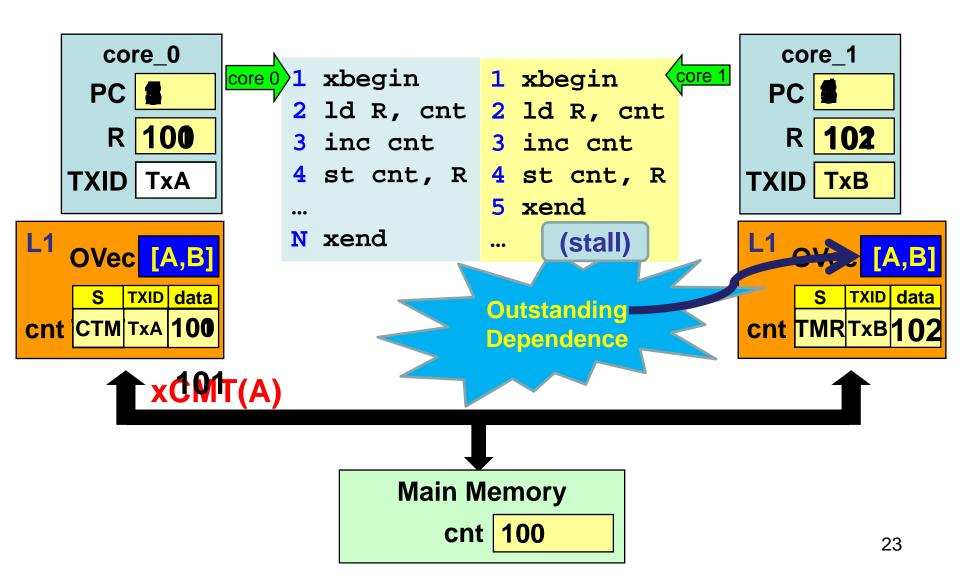

#### **Converting Conflicts to Dependences**

# Outline

- Motivation/Background

- Dependence-Aware Model

- Dependence-Aware Hardware

- Experimental Methodology/Evaluation

- Conclusion

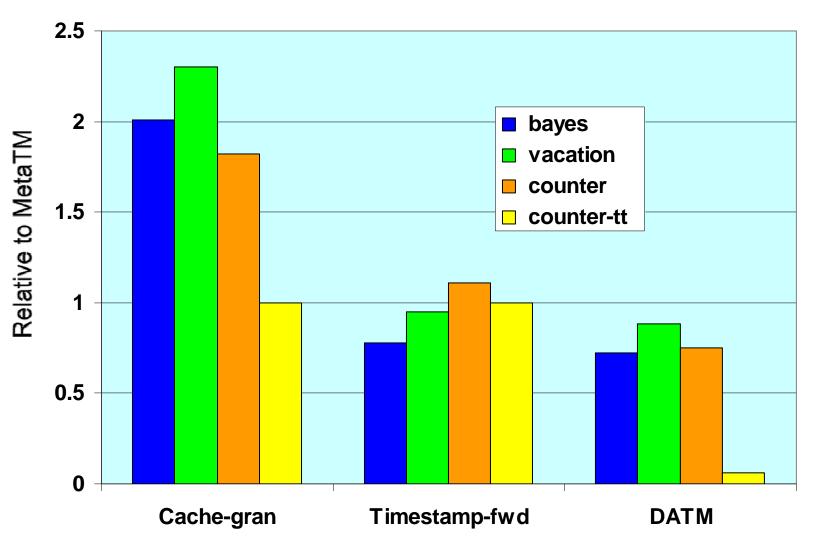

## **Experimental Setup**

- Implemented DATM by extending MetaTM

- Compared against MetaTM: [Ramadan 2007]

- Simulation environment

- Simics 3.0.30 machine simulator

- x86 ISA w/HTM instructions

- 32k 4-way tx L1 cache; 4MB 4-way L2; 1GB RAM

- 1 cycle/inst, 24 cyc/L2 hit, 350 cyc/main memory

- 8, 16 processors

- Benchmarks

- Micro-benchmarks

- STAMP [Minh ISCA 2007]

- TxLinux: Transactional OS [Rossbach SOSP 2007]

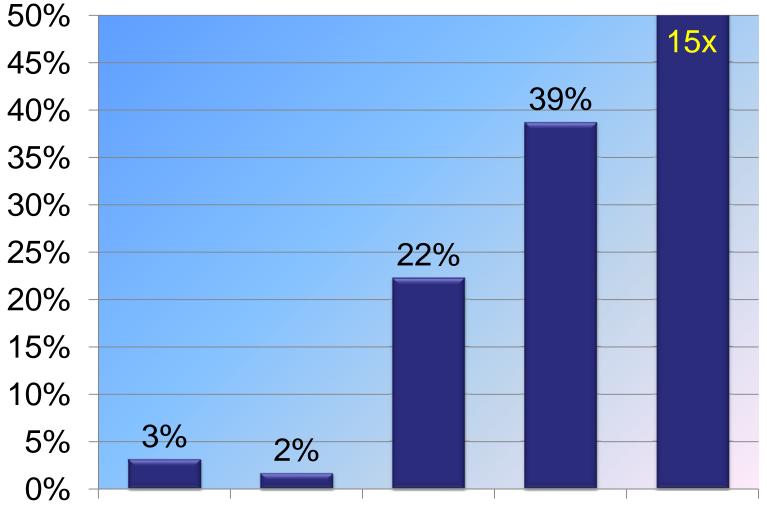

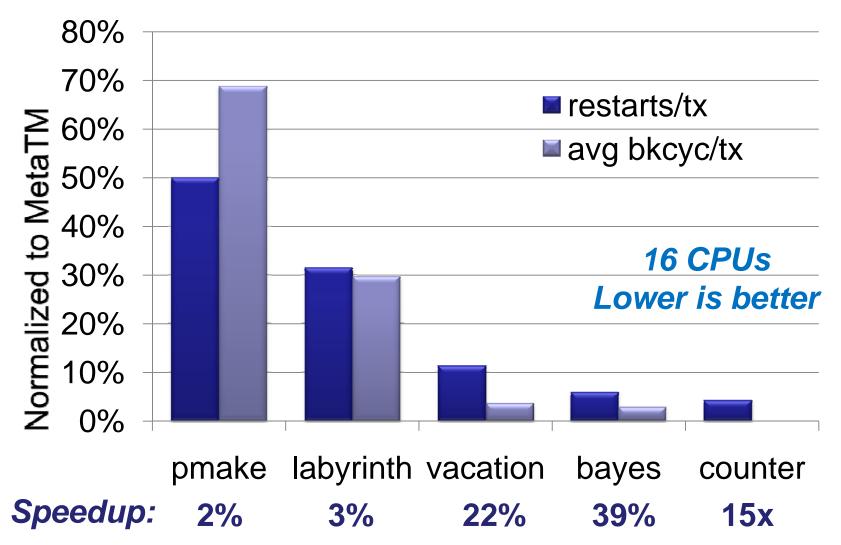

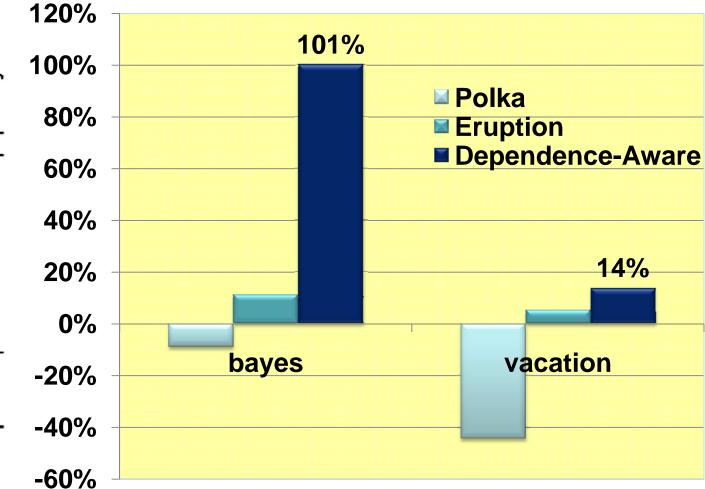

#### DATM speedup, 16 CPUs

pmake labyrinth vacation bayes counter

26

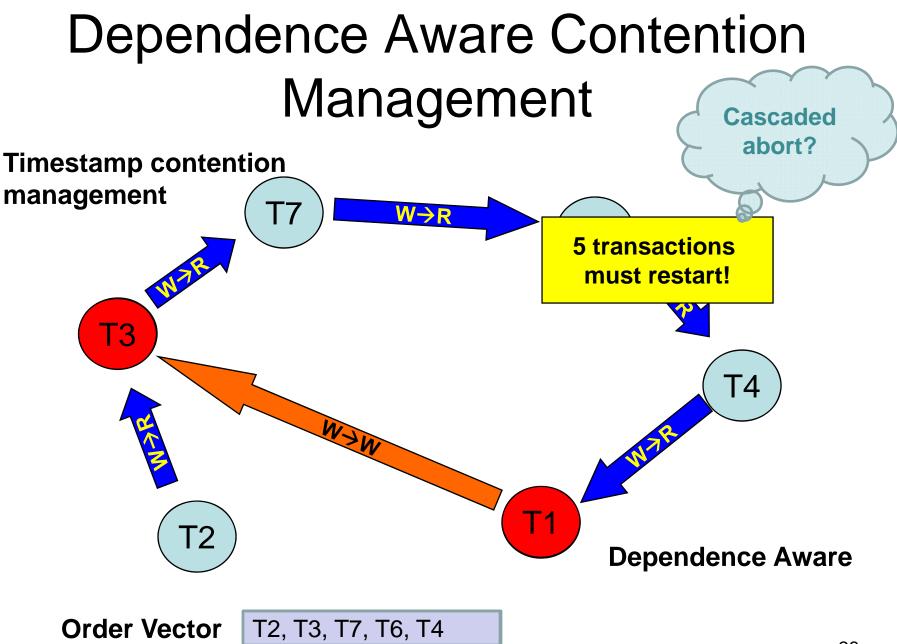

## Eliminating wasted work

#### **Contention Management**

Speedup over Timestamp policy

# Outline

- Motivation/Background

- Dependence-Aware Model

- Dependence-Aware Hardware

- Experimental Methodology/Evaluation

- Conclusion

## **Related Work**

#### • HTM

TCC [Hammond 04], LogTM[-SE] [Moore 06], VTM [Rajwar 05], MetaTM [Ramadan 07, Rossbach 07], HASTM, PTM, HyTM, RTM/FlexTM [Shriraman 07,08]

• TLS

Hydra [Olukotun 99], Stampede [Steffan 98,00], Multiscalar [Sohi 95], [Garzaran 05], [Renau 05]

#### • TM Model extensions

- Privatization [Spear 07], early release [Skare 06], escape actions [Zilles 06], open/closed nesting [Moss 85, Menon 07], Galois [Kulkarni 07], boosting [Herlihy 08], ANTs [Harris 07]

- TM + Conflict Serializability

- Adaptive TSTM [Aydonat 08]

#### Conclusion

- DATM can commit conflicting transactions

- Improves write-sharing performance

- Transparent to the programmer

- DATM prototype demonstrates performance benefits

Source code available! www.metatm.net 32

#### **Broadcast and Scalability**

#### Yes. We broadcast. But it's less than you might think...

| benchmark  | tx      | broadcast w | forw rest |

|------------|---------|-------------|-----------|

| bayes      | 762     | 1           | 0.4%      |

| config(8p) | 4698136 | 10,132      | 19.7%     |

| counter    | 160000  | 0           | 0%        |

| counter-tt | 16000   | 0           | 0%        |

| genome     | 352376  | 104         | 0%        |

| kmeans     | 436986  | 40,723      | 0%        |

| labyrinth  | 128     | 4           | 0%        |

| list(8p)   | 78586   | 86          | 3.3%      |

| pmake(8p)  | 251844  | 10,009      | 12.9%     |

| ssca2      | 47304   | 0           | 0%        |

| vacation   | 20000   | 143         | 0.4%      |

Because each node maintains all deps, <u>this design</u> uses broadcast for:

- Commit

- Abort

- TXOVW (broadcast writes)

- Forward restarts

- New Dependences

These sources of broadcast could be avoided in a directory protocol:

keep only the relevant subset of the dependence graph at each node

## **FRMSI** Transient states

## Why isn't this TLS?

|                                            | TLS          | DATM         | ТМ           |

|--------------------------------------------|--------------|--------------|--------------|

| Forward data between threads               | $\checkmark$ | $\checkmark$ |              |

| Detect when reads occur too early          | $\checkmark$ |              |              |

| Discard speculative state after violations | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Retire speculative<br>Writes in order      | $\checkmark$ | $\checkmark$ |              |

| Memory renaming                            | $\checkmark$ |              |              |

| Multi-threaded workloads                   |              | $\checkmark$ | $\checkmark$ |

| Programmer/Compiler transparency           |              | $\checkmark$ |              |

- 1. Txns can commit in arbitrary order. TLS has the daunting task of maintaining program order for epochs

- 2. TLS forwards values when they are the globally committed value (i.e. through memory)

- 3. No need to detect "early" reads (before a forwardable value is produced)

- 4. Notion of "violation" is different—we must roll back when CS is violated, TLS, when epoch ordering

- 5. Retiring writes in order: similar issue—we use CTM state, don't need speculation write buffers. <sup>35</sup>

- 6. Memory renaming to avoid older threads seeing new values—we have no such issue

#### Doesn't this lead to cascading aborts?

|             | WR deps | RW deps | forward<br>restarts | cascade<br>aborts |

|-------------|---------|---------|---------------------|-------------------|

| bayes       | 3.8%    | 8.5%    | 0.4%                | 0%                |

| config (8p) | 0.3%    | 0.2%    | 19.7%               | 2.3%              |

| counter     | 90.0%   | 80.7%   | 0%                  | 0%                |

| counter-tt  | 99.9%   | 0.3%    | 0%                  | 100.0%            |

| genome      | 0.1%    | 0.1%    | 0%                  | 14.2%             |

| kmeans      | 8.9%    | 6.0%    | 0%                  | 3.1%              |

| labyrinth   | 32.0%   | 32.0%   | 0%                  | 0.1%              |

| list        | 14.3%   | 3.8%    | 3.3%                | 0.2%              |

| pmake (8p)  | 0.5%    | 0.5%    | 12.9%               | 6.5%              |

| ssca2       | 0.1%    | 0.1%    | 0%                  | 0%                |

| vacation    | 35.2%   | 7.9%    | 0.4%                | 3.5%              |

#### Rare in most workloads

#### **Inconsistent Reads**

|             | incons.<br>reads |

|-------------|------------------|

| bayes       | 3                |

| config (8p) | 1                |

| counter     | 0                |

| counter-tt  | 0                |

| genome      | 1                |

| kmeans      | 0                |

| labyrinth   | 1                |

| list        | 0                |

| pmake (8p)  | 10               |

| ssca2       | 0                |

| vacation    | 34               |

#### **OS** modifications:

- Page fault handler

- Signal handler

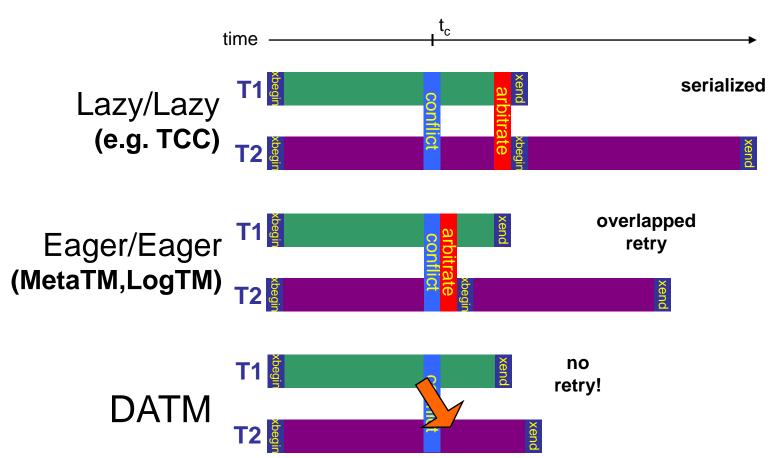

## **Increasing Concurrency**

(Eager/Eager:Upplatessbinffelence, conflict detection att common term)ence)

# Design space highlights

- Cache granularity:

- eliminate per word access bits

- Timestamp-based dependences: – eliminate Order Vector

- Dependence-Aware contention management

## **Design Points**

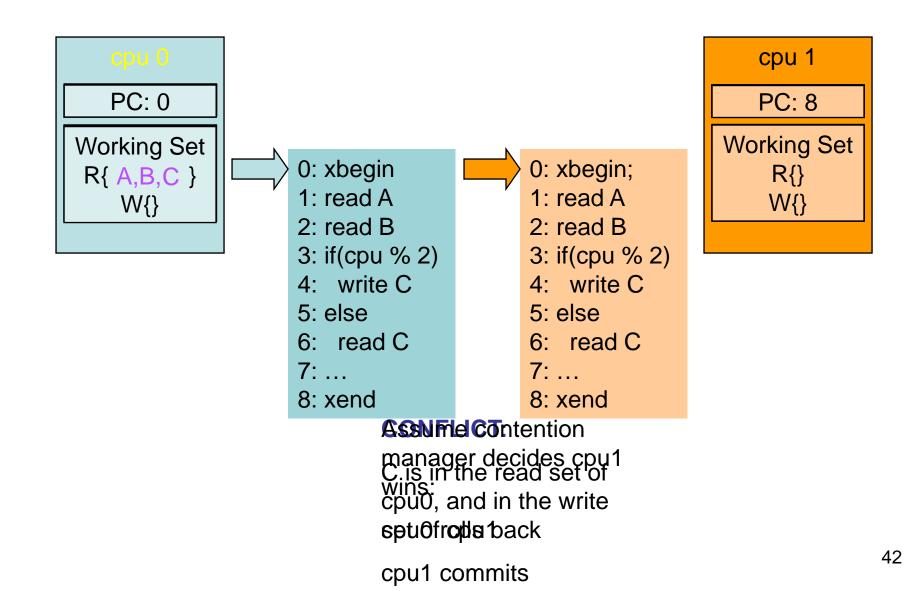

## Hardware TM Primer

#### Key Ideas:

- Critical sections execute concurrently

- Conflicts are detected dynamically

- If conflict serializability is violated, rollback

#### Key Abstractions:

- Primitives

- -xbegin, xend, xretry

- Conflict

- $\emptyset \neq \{W_a\} \cap \{R_b \cup W_b\}$

- Contention Manager

- -Need flexible policy

"Conventional Wisdom Transactionalization": Replace locks with transactions

#### Hardware TM basics: example