# Cache Vocabulary

# CS429: Computer Organization and Architecture Cache II

Dr. Bill Young Department of Computer Science University of Texas at Austin

Last updated: April 22, 2019 at 10:32

Much of the cache organization described in these slidesets applies to the L1 and L2 caches; not to other caches such as the TLB, browser caches, etc.

- Capacity

- Cache block/line

- Associativity

- Cache set

- Set index

- Tag

- Block offset

- Hit rate

- Miss rate

- Placement policy

- Replacement policy

| CS429 Slideset 19: 1 Cache II                                                                                                                  | CS429 Slideset                                                   | et 19: 2 Cache II                                                 |                                                                                         |                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|

| The Memory Abstraction                                                                                                                         | Organization of Cache N                                          | Memory                                                            |                                                                                         |                    |

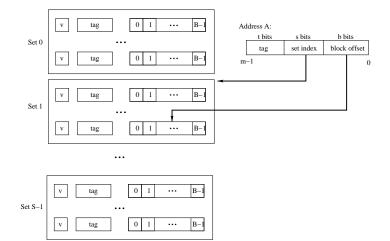

| Conceptually, memory is a large array of bytes that can be<br>accessed from your program by specifying a starting address and a<br>byte count. | Cache is an array of $S = 2^s$ sets.                             | 1 valid bit t tag bits<br>per line per line<br>v tag<br>Set 0 ··· | $B = 2b \text{ bytes} \\ \text{per cache block} \\ \hline 0  1  \cdots  B-1 \\ \bullet$ | E lines<br>per set |

| get( addr1, k )                                                                                                                                | Each set contains $E \ge 1$ lines.                               | v tag                                                             | 0 1 ··· B-1                                                                             |                    |

| addr2<br>addrk                                                                                                                                 | Each line holds a block<br>of data containing<br>$B = 2^b$ bytes | Set 1                                                             | •<br>0 1 ••• B-1                                                                        |                    |

| [M(addr1), , M(addrk)]                                                                                                                         | Cache size:<br>$C = B \times E \times S$ data                    | v tag                                                             | 0 1 ···· B-1                                                                            |                    |

| Like any other memory optimization, caching must maintain this abstraction.                                                                    | bytes. <sub>Set</sub>                                            | v tag                                                             | 0 1 ··· B-1                                                                             |                    |

CS429 Slideset 19: 3 Cache II

CS429 Slideset 19: 4 Cache II

The word at address A is in the cache if the tag bits in one of the *valid* lines in set *set\_index* match *tag* for that line.

The word contents begin at offset *block offset* from the beginning of the block.

CS429 Slideset 19: 5

Cache II

## Direct-Mapped Cache

This is the simplest kind of cache, characterized by exactly one line per set (i.e, E = 1).

#### What is the placement policy for such a cache?

An address must be placed into some line in the set matching the *set index* of the address.

#### What is the replacement policy for such a cache?

This can vary. A common replacement policy is: replace the *least* recently used (LRU) line in the set with a new line containing the accessed address.

CS429 Slideset 19: 6 Cache

## Accessing Direct-Mapped Caches

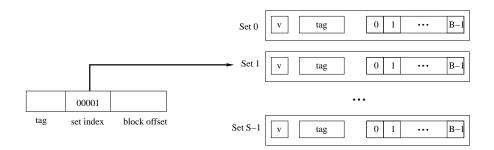

Use the set index bits to determine the set of interest.

## **Direct-Mapped Caches:** Matching and Selection

## Bytes in the Line

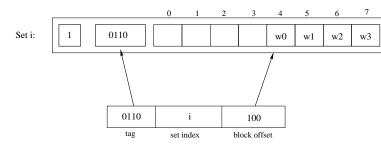

- Line matching: Find a valid line in the selected set with a matching tag.

- Word selection: Extract the word using the block offset.

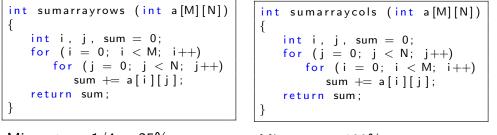

- The valid bit must be set.

- O The tag bits in the cache line must match the tag bits in the address.

- $\bigcirc$  If (1) and (2), then cache hit, and block offset selects starting bits.

#### Set i: 1 0110 w0w1w2w3 0110 i 100 tag set index block offset

Suppose that the set index is 4 bits. What are the characteristics of this cache?

- How big are addresses on this machine?

- How many sets are there in the cache?

- How many lines per set?

- How many bytes per line? 4

- How big is the block offset? 3

- Suppose i = 0101. What range of bytes are in this line?

B-

B-1

B-1

B-1

B-1

B-1

E lines

per set

CS429 Slideset 19: 9

## **Direct-Mapped Cache Simulation**

Suppose:

## Set Associative Caches

• M = 16 byte 1 valid bit t tag bits addresses: B = 2b bytes per line per line per cache block Address х xx х  $\bullet B = 2$ tag ••• bytes/block: Set 0 . . . 0 [0000] (miss) • S = 4 sets: 13 [1101] (miss) 0 1 ••• v tag tag data tag data • E = 1 line/set. 0 0 M[0-1] M[0-1]v 0 1 ••• tag (3) (1)Set 1 M[12-13] 1 1 • • • Address trace v tag 0 1 ••• (reads):  $0 = [0000_2]$ ... 8 [1000] (miss) 0 [0000] (miss) tag data tag data  $0 1 = [0001_2]$ 0 M[0-1]1 M[8-9] 1 v tag 0 •••  $13 = [1101_2]$ 3 (4) (5) Set S-1 ... M[12-13] 1 1 M[12-13] 1 1  $0 8 = [1000_2]$ v 0 ••• tag  $0 = [0000_2]$ CS429 Slideset 19: 11

These are characterized by more than one line per set.

CS429 Slideset 19: 10

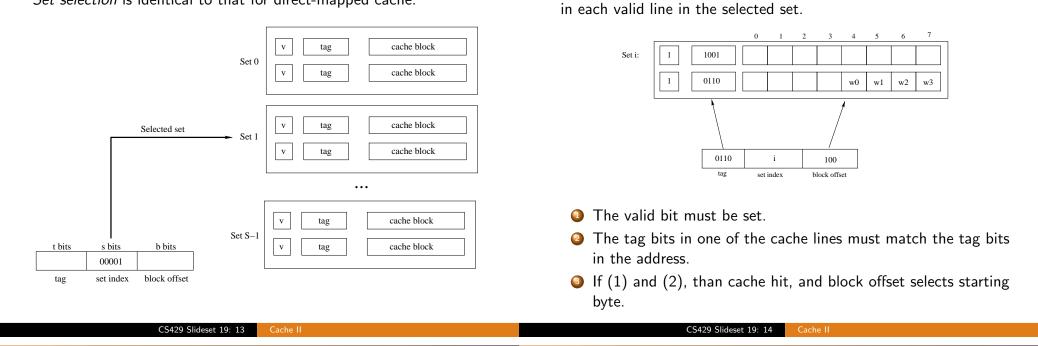

#### Accessing Set Associative Caches

#### Accessing Set Associative Caches

Set selection is identical to that for direct-mapped cache.

# Why Use Middle Bits as Index?

#### **High-Order Bit Indexing**

- Adjacent memory blocks map to same cache entry.

- Poor use of spatial locality.

#### Low-Order Bit Indexing

- Consecutive memory blocks map to different cache lines.

- Can hold a larger region of address space in cache at one time.

| High–Order<br>Bit Indexing | Middle–Order<br>Bit Indexing |  |  |

|----------------------------|------------------------------|--|--|

|                            | 0000                         |  |  |

|                            | 0001                         |  |  |

|                            | 0010                         |  |  |

|                            | 0011                         |  |  |

|                            | 0100                         |  |  |

|                            | 0101                         |  |  |

|                            | 0110                         |  |  |

|                            | 0111                         |  |  |

|                            | 1000                         |  |  |

|                            | 1001                         |  |  |

|                            | 1010                         |  |  |

|                            | 1011                         |  |  |

|                            | 1100                         |  |  |

|                            | 1101                         |  |  |

|                            | 1110                         |  |  |

|                            | 1111                         |  |  |

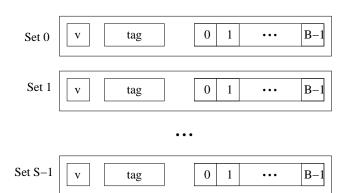

A fully associative cache is one that has only one set.

**Fully Associative Caches**

| v | tag |     | 0 | 1 | ••• | B-1 |

|---|-----|-----|---|---|-----|-----|

| v | tag | ••• | 0 | 1 | ••• | B-1 |

For Line Matching and Word Selection, we must compare the tag

- There are no set index bits in the address.

- Otherwise, accessing is the same as for a set associative cache.

- Tends to require more hardware to perform the associative search on a larger number of lines.

0000

0001 0010 0011

0100

0101

0110 0111

1000

1001

1010

1011

1100

1101

1110 1111

#### Miss Rate

- Fraction of memory references not found in the cache (misses / references)

- Typical numbers: 3-10% for L1; can be quite small (e.g., <1%) for L2, depending on size, etc.

#### Hit Time

- Time to deliver a line in the cache to the processor (including time to determine whether the line is in the cache).

- Typical numbers: 1-3 clock cycles for L1; 5-12 clock cycles for L2.

### **Miss Penalty**

• Additional time required because of a miss.

CS429 Slideset 19: 17

• Typically 100-300 cycles for main memory.

Memory System Performance II

## Average Memory Access Time (AMAT)

$$T_{access} = (1 - p_{miss}) \cdot t_{hit} + p_{miss} \cdot t_{miss}$$

$t_{miss} = t_{hit} + t_{penalty}$

Assume 1-level cache, 90% hit rate, 1 cycle hit time, 200 cycle miss time (hit time plus miss penalty).

$$t_{\textit{access}} = (1 - 0.1) \cdot 1 + 0.1 \cdot 200 = 0.9 + 20 \approx 21$$

$\mathsf{AMAT}=21$  cycles, even though 90% only take one cycle. This shows the importance of a high hit rate.

#### CS429 Slideset 19: 18 Cache

# Memory System Performance and the Pipeline

How does AMAT affect overall performance? Recall the CPI equation (pipeline efficiency).

$$CPI = 1.0 + lp + mp + rp$$

- load/use penalty (lp) assumed memory access of 1 cycle.

- Further, we assumed all load instructions were 1 cycle.

| Cause      | Name | Instr. | Cond. | Stalls | Product |

|------------|------|--------|-------|--------|---------|

|            |      | Freq.  | Freq. |        |         |

| Load       | lp   | 0.30   | 0.7   | 21     | 4.41    |

| Load/Use   | lp   | 0.30   | 0.3   | 21+1   | 1.98    |

| Mispredict | mp   | 0.20   | 0.4   | 2      | 0.16    |

| Return     | rp   | 0.02   | 1.0   | 3      | 0.06    |

| Total      |      |        |       |        | 6.61    |

More realistic AMAT (20+ cycles) really hurts CPI and overall performance.

Suppose your pipelined Y86 machine had a 1-level cache, 90% hit rate, 1 cycle hit time, 200 cycle miss time.

$$t_{access} = (1 - 0.1) \cdot 1 + 0.1 \cdot 200 = 0.9 + 20 \approx 21$$

Recall that the clock speed of the pipeline is constrained by the *slowest* stage (M).

What does this mean for the pipelined Y86 if the slowest stage has such huge variability? What could you do?

What does this mean for the pipelined Y86 if the slowest stage has such huge variability? What could you do?

- Q Run the clock 200 times more slowly to accommodate the longest memory access? Obviously not.

- Stall the pipeline when you have a cache miss? There's really no other alternative. Why not?

Reads from memory really can't come from anywhere else. Forwarding won't help; the value is not in any pipeline register.

$$egin{array}{l} T_{access} = (1 - eta_{miss}) \cdot t_{hit} + eta_{miss} \cdot t_{miss} \ t_{miss} = t_{hit} + t_{penalty} \end{array}$$

How can we reduce AMAT?

- Reduce the miss rate.

- Reduce the miss penalty.

- Reduce the hit time.

There have been numerous inventions targeting each of these. Which would matter most?

| CS429 Slideset 19: 21 Cache II                                                                                                                        | CS429 Slideset 19: 22         | Cache II |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------|

| sues with Writes                                                                                                                                      | Write Strategies              |          |

| If you <i>write</i> to an item in cache, the cached value becomes <i>inconsistent</i> with the values stored at lower levels of the memory hierarchy. | How to deal with write misses | ?        |

There are two main approaches to dealing with this:

lssue

- Write-through: immediately write the cache block to the next lowest level.

- Write-back: only write to lower levels when the block is evicted from the cache.

*Write-through* requires updating multiple levels of the memory hierarchy (causes bus traffic) on every write.

Write-back reduces bus traffic, but requires that each cache line have a *dirty bit*, indicating that the line has been modified.

Write-allocate loads the line from the next level and updates the cache block.

No-write-allocate bypasses the cache and updates directly in the lower level of the memory hierarchy.

Write-through caches are typically no-write-allocate. Write-back caches are typically write-allocate. Why does this make sense?

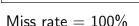

- Can write code to improve miss rate.

- Repeated references to variables are good (temporal locality).

- Stride-1 reference patterns are good (spatial locality).

**Examples:** Assume cold cache, 4-byte words, 4-word cache blocks.

Miss rate = 1/4 = 25%

- What happens where there is a miss and the cache has no free lines? What should we evict?

- What happens on a write miss?

- What if we have a multicore chip where cores share the L2 cache but have private L1 caches? What bad things could happen?

CS429 Slideset 19: 26

#### CS429 Slideset 19: 25

## **Concluding Observations**

A programmer can optimize for cache performance.

- How data structures are organized.

- How data are accessed.

- Nested loop structure.

All systems favor "cache friendly code."

- Getting absolute optimum performance is very platform specific (cache sizes, line sizes, associativities, etc.)

- But you can get most of the advantage with generic code.

- Keep the working set reasonably small (temporal locality).

- Use small strides (spatial locality).