### Proceedings of the 17th Conference on Formal Methods in Computer-Aided Design (FMCAD 2017) TU Wien, Vienna, Austria, October 2-6, 2017

Edited by Daryl Stewart and Georg Weissenbacher

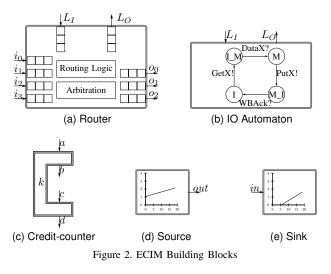

In cooperation with ACM Special Interest Group on Programming Languages ACM Special Interest Group on Software Engineering

h.....

hammi

Technical co-sponsorship of IEEE

TTITTIII.

......

Proceedings of the 17th Conference on

# Formal Methods in Computer-Aided Design FMCAD 2017

October 2-6, 2017

TU Wien, Vienna, Austria

Edited by Daryl Stewart and Georg Weissenbacher

ISBN: 978-0-9835678-7-5 Copyright owned jointly by the authors and FMCAD Inc. Title page photo: Copyright TU Wien

### Preface

The International Conference on Formal Methods in Computer Aided Design (FMCAD), held at TU Wien in Vienna, Austria, from October 2-6 in 2017, is the seventeenth in a series of meetings on the theory and applications of rigorous formal techniques for the automated design of systems. The FMCAD conference covers formal aspects of specification, verification, synthesis, testing, and security, and is a leading forum for researchers and practitioners in academia and industry alike.

The program of FMCAD 2017 comprises a tutorial day with three tutorials on security and concurrency (joint with the collocated MEMOCODE conference), two keynotes on the use of formal methods in industry, a forum for doctoral students, the Hardware Model Checking Competition 2017, the main program consisting of presentations of the accepted papers, and a Symposium in Memoriam of Helmut Veith.

The tutorial day features three presentations covering security and weak-memory concurrency (listed in the order of appearance in the program):

- "How Formal Methods and Analysis Helps Security of Entire Blockchain-based Systems", by Shin'ichiro Matsuo (MIT Media Lab, CELLOS Consortium, and BSafe.network)

- "Symbolic Security Analysis using the Tamarin Prover", by Cas Cremers (Oxford University)

- "Coalition, intrigue, ambush, destruction and pride: herding cats can be challenging", by Jade Alglave (University College London and Microsoft Research)

The keynotes focus on the application of formal verification in industry, and on the verification of cloud computing platforms and dependable systems in particular:

- "Automated Formal Reasoning About AWS Systems" by Byron Cook (Amazon Web Services and University College London)

- "Formal Methods in Industrial Dependable Systems Design The TTTech Example" by Wilfried Steiner (TTTech Computertechnik AG)

FMCAD also hosts the fifth edition of the Student Forum, which has been held annually since 2013 and provides a platform for graduate students at any career stage to introduce their research to the FMCAD community. The FMCAD Student Forum 2017 was organized by Keijo Heljanko and features posters and short presentations of thirteen accepted contributions. A detailed description of the Student Forum, listing all accepted contributions, is provided in the conference proceedings.

The Hardware Model Checking Competition 2017, affiliated with FMCAD 2017 and organized by Armin Biere, Tom van Dijk, and Keijo Heljanko, is a competitive event for hardware model checking tools from academia and industry. A description of this year's competition is provided in the proceedings.

The Symposium in Memoriam Helmut Veith, held on the last day of FMCAD 2017, is dedicated to the memory of Helmut Veith, who tragically passed away in March 2016. Helmut was one of the organizers of FMCAD 2016 and an active and much liked member of the FMCAD community. The Symposium honors Helmut and his contributions to the area of formal methods, which remain highly influential, with talks on model checking, synthesis, distributed algorithms, and security, given by collaborators, colleagues, and friends of Helmut and based on articles published in a Special Edition of the Journal on Formal Methods in System Design in Memoriam Helmut Veith. As part of the Symposium, a LogicLounge on Teaching Logic in Computer Science remembers Helmut's dedication to mentoring and his achievements in creating and shaping doctoral and master's programs on Logic and Computation at TU Wien. The LogicLounge is a series of discussions on computer science topics targeting a general audience, which was initiated by Helmut Veith at the Vienna Summer of Logic in 2014.

FMCAD 2017 received 87 abstracts, resulting in 67 submissions, of which 25 full papers and 4 short papers were accepted for publication in the conference proceedings. Each paper received at least four reviews, and the authors were given the opportunity to address the reviewers' concerns in a rebuttal phase. The topics of the accepted papers include solvers and decision procedures, verification of concurrent and distributed systems, analysis of hybrid and probabilistic systems, synthesis, run-time verification, a number of papers on the IC3 model checking paradigm, and applications of formal methods.

Organizing this event would not have been possible without the support of a large number of people and our sponsors. The program committee members and additional reviewers, listed on the following pages, did an excellent job providing detailed and insightful reviews, which helped the authors to improve their submissions and guided the selection of the papers accepted for publication. We thank each and every one of them for dedicating their time and providing their expertise. Moreover, we'd like to give special thanks to the sub-committee which agreed to select the recipients of this year's Best Paper Award. We thank the Publication Chair Mitra Tabaei Befrouei (TU Wien) for her effort in preparing and assembling the conference proceedings, and Keijo Heljanko for organizing this year's FMCAD Student Forum. Our webmaster, Jens Katelaan, has our gratitude for maintaining and regularly updating the FMCAD website (which now features the new and sleek FMCAD logo designed by Anna Oberauer). We thank all students who volunteered to help running the event. As always, the help and expertise of the FMCAD steering committee made the organization of FMCAD much easier. We thank Armin Biere (Johannes Kepler University in Linz, Austria), Alan Hu (University of British Columbia, Canada), and especially Warren A. Hunt,. Jr.

(University of Texas at Austin) and Vigyan Singhal (Oski Tech) for supporting and encouraging us, and guiding us through the organization process.

Holding a conference like FMCAD would not be feasible without the financial support of our sponsors. We would like to express our gratitude (in alphabetical order) to our sponsors Amazon, ARM Ltd., Centaur Technology Inc., DiffBlue Ltd., Galois Inc., IBM, Microsoft Research, Oski Technology, Real Intent Inc., Synopsis, TTTech Computertechnik AG, and the Vienna Science and Technology Fund for their financial support of the conference, and the Austrian Ministry for Transport, Innovation and Technology and the National Science Foundation for their support of the Student Forum.

FMCAD 2017 is in-cooperation with the ACM and its Special Interest Groups on Programming Languages (SIGPLAN) and on Software Engineering (SIGSOFT). The FMCAD conference also received technical sponsorship from the IEEE Council on Electronic Design Automation. The conference proceedings will be available through the ACM Digital Library, the IEEE Xplore Digital Library, and are also freely accessible on the FMCAD Website.

Last but not least, we thank all authors who submitted their papers to FMCAD 2017 (accepted or not), and whose contributions and presentations form the core of the conference. We are grateful to everyone who presented their paper, gave a keynote or a tutorial, devoting a significant amount of their time to the FMCAD conference. We thank all attendees of FMCAD for supporting the conference and making FMCAD a stimulating and enjoyable event.

Daryl Stewart and Georg Weissenbacher FMCAD 2017 Program Chairs Vienna, Austria, September 2017

FMCAD 2017 is overshadowed by the death of Professor Michael J. C. Gordon, who recently (22 August 2017) passed away at the age of 69 after a brief illness. Professor Gordon was a leader in the use of mechanized formal methods to analyze hardware and software, and he was the original developer of the HOL theorem-proving system. Gordon was an expert in program semantics, and he was elected a Fellow of the Royal Society in 1994. The FMCAD community has benefited tremendously from Gordon's many contributions, and no doubt Gordon's efforts will continue to influence our community for many years to come. He will be sorely missed, not only for his wisdom and expertise but also for his distinctively generous and friendly spirit.

Warren A. Hunt Jr. Chairman, FMCAD Steering Committee

### **Organization Committee**

| Program C   | o-Chairs                             |                    |

|-------------|--------------------------------------|--------------------|

|             | Daryl Stewart<br>Georg Weissenbacher | ARM, UK<br>TU Wien |

| Webmaster   | Jens Katelaan                        | TU Wien            |

| Publication | Chair                                |                    |

|             | Mitra Tabaei Befrouei                | TU Wien            |

| Student Fo  | rum Chair                            |                    |

|             | Keijo Heljanko                       | Aalto University   |

| Steering Co | ommittee                             |                    |

|             | Armin Biere                          | Johannes Kepler U  |

|             | Alan Hu                              | University of Brit |

|             | Warren Hunt                          | University of Texa |

Vigyan Singhal

Johannes Kepler University in Linz, Austria University of British Columbia, Canada University of Texas at Austin, USA Oski Tech

### **Program Committee**

Jade Alglave Christel Baier Roderick Bloem Hana Chockler Andreas Griesmayer Arie Gurfinkel Fei He Keijo Heljanko Alan J. Hu Warren Hunt Alexander Ivrii Barbara Jobstmann Dejan Jovanović Gerwin Klein Igor Konnov Rebekah Leslie-Hurd Ines Lynce Ken McMillan Charles Morisset Lee Pike Mitra Purandare Ajitha Rajan Ahmed Rezine Sean Safarpour Roopsha Samanta Martina Seidl Natasha Sharygina Anna Slobodova Ana Sokolova Daryl Stewart Murali Talupur Michael Tautschnig Thomas Wahl Chao Wang Georg Weissenbacher Florian Zuleger

University College London Technical University of Dresden TU Graz King's College London ARM University of Waterloo School of Software, Tsinghua University Aalto University University of British Columbia University of Texas IBM EPFL and Cadence Design Systems SRI International Data61 and UNSW TU Wien Intel INESC-ID/IST, Universidade de Lisboa Microsoft Research Newcastle University Galois, Inc. IBM Research Laboratory Zurich University of Edinburgh Linköping University Synopsys Purdue University Johannes Kepler University Linz Università della Svizzera italiana (USI Lugano, Switzerland) Centaur Technology University of Salzburg ARM FormalSim Queen Mary University of London Northeastern University University of Southern California TU Wien TU Wien

### **Additional Reviewers**

Aleksandrowicz, Gadi Arbel, Eli Asadi, Sepideh Ashar, Pranav Athanasiou, Konstantinos Auerbach, Gadiel

Bartocci, Ezio Beringer, Lennart Berryhill, Ryan Bjesse, Per Brain, Martin

Čadek, Pavel Chapman, Erin Chau, Cuong

Das, Shidhartha de Paula, Flavio M. Dubuisson, Thomas

Ebrahimi, Masoud Elliott, Trevor Even Mendoza, Karine

Fazekas, Katalin Fedyukovich, Grigory Fernandez, Matthew Függer, Matthias

Ganai, Malay Giefers, Heiner Gu, Yijia Guo, Shengjian Günther, Henning

Hamza, Jad Heule, Marijn Hyvärinen, Antti

Ignatiev, Alexey Iusupov, Rinat

Jacobs, Swen Jain, Himanshu Jaloyan, Georges-Axel Janota, Mikolas

Karl, Anja Katelaan, Jens Khalimov, Ayrat Kirsch, Christoph Klüppelholz, Sascha Koelbl, Alfred Koyfman, Shlomit Kragl, Bernhard Krakovsky, Roi Kukovec, Jure Kusano, Markus

Laarman, Alfons Lammich, Peter Lazic, Marijana Leslie-Hurd, Joe Liu, Peizun

Malik, Sharad Marescotti, Matteo Mencía, Carlos Morgado, Antonio Märcker, Steffen

Nalla, Pradeep Kumar Nevo, Ziv

Orni, Avigail

Pani, Thomas Previti, Alessandro

Rabe, Markus N. Radicek, Ivan Ramachandran, Jaideep Ravitch, Tristan Rebola Pardo, Adrian Ritirc, Daniela Roveri, Marco

Saracino, Andrea Schlaipfer, Matthias Sethi, Divjyot Sewell, Thomas Singleton, Iain Sison, Robert Stoilkovska, Ilina Sumners, Rob Sung, Chungha Swords, Sol

Tanaka, Miki Tomb, Aaron Tran, Thanh Hai

Wendler, Philipp Winwood, Simon Wu, Meng

Yin, Liangze

### **Table of Contents**

#### **Invited Papers**

| How formal analysis and verification add security to blockchain-based systems                                                                                                 | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Symbolic Security Analysis using the Tamarin Prover                                                                                                                           | 5  |

| Coalition, intrigue, ambush, destruction and pride: herding cats can be challenging<br>Jade Alglave                                                                           | 6  |

| Automated Formal Reasoning About AWS Systems<br>Byron Cook                                                                                                                    | 7  |

| Formal Methods in Industrial Dependable Systems Design - The TTTech Example                                                                                                   | 8  |

| Hardware Model Checking Competition 2017<br>Armin Biere, Tom van Dijk and Keijo Heljanko                                                                                      | 9  |

| The FMCAD 2017 Graduate Student Forum                                                                                                                                         | 10 |

| Arithmetic                                                                                                                                                                    |    |

| goSAT: Floating-point Satisfiability as Global Optimization<br>M. Ammar Ben Khadra, Dominik Stoffel and Wolfgang Kunz                                                         | 11 |

| On Sound Relative Error Bounds for Floating-Point Arithmetic                                                                                                                  | 15 |

| Column-Wise Verification of Multipliers Using Computer Algebra<br>Daniela Ritirc, Armin Biere and Manuel Kauers                                                               | 23 |

| Solving                                                                                                                                                                       |    |

| Efficient Generation of All Minimal Inductive Validity Cores                                                                                                                  | 31 |

| Duality-Based Interpolation for Quantifier-Free Equalities and Uninterpreted Functions                                                                                        | 39 |

| Solving Linear Arithmetic with SAT-based Model Checking<br>Yakir Vizel, Alexander Nadel and Sharad Malik                                                                      | 47 |

| Z3str3: A String Solver with Theory-aware Heuristics<br>Murphy Berzish, Vijay Ganesh and Yunhui Zheng                                                                         | 55 |

| Concurrency and Distributed Systems                                                                                                                                           |    |

| Verification of a lazy cache coherence protocol against a weak memory model<br>Christopher Banks, Marco Elver, Ruth Hoffmann, Susmit Sarkar, Paul Jackson and Vijay Nagarajan | 60 |

| Safety Verification of Phaser Programs<br>Zeinab Ganjei, Ahmed Rezine, Petru Eles and Zebo Peng                                                                               | 68 |

| Learning to prove safety over parameterised concurrent systems                                                                                                                | 76 |

Lasso detection using Partial State Caching

84

Rashmi Mudduluru, Pantazis Deligiannis, Ankush Desai, Akash Lal and Shaz Qadeer

84

Yu-Fang Chen, Chih-Duo Hong, Anthony Widjaja Lin and Philipp Ruemmer

#### **Probabilistic Systems**

| Exact Quantitative Probabilistic Model Checking Using Rational Search                 | 92 |

|---------------------------------------------------------------------------------------|----|

| Matthew S. Bauer, Umang Mathur, Rohit Chadha, A. Prasad Sistla and Mahesh Viswanathan |    |

| Sampling Invariants from Frequency Distributions                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| BDDs                                                                                                                                              |

| Tagged BDDs: Combining reduction rules from different decision diagram types                                                                      |

| First-order Temporal Logic Monitoring with BDDs                                                                                                   |

| Factored Boolean Functional Synthesis                                                                                                             |

| IC3                                                                                                                                               |

| Property Directed Reachability with Word-Level Abstraction                                                                                        |

| Learning Support Sets in IC3 and Quip: the Good, the Bad, and the Ugly                                                                            |

| K-Induction without Unrolling                                                                                                                     |

| Designing Parallel PDR                                                                                                                            |

| FuseIC3: An Algorithm for Checking Large Design Spaces                                                                                            |

| FAR-Cubicle - A new reachability algorithm for Cubicle       172         Sylvain Conchon, Amit Goel, Sava Krstic, Rupak Majumdar and Mattias Roux |

| Theta: a Framework for Abstraction Refinement-Based Model Checking                                                                                |

| Hybrid Systems                                                                                                                                    |

| Modular SMT-Based Analysis of Nonlinear Hybrid Systems                                                                                            |

| SMT-based Analysis of Switching Multi-Domain Linear Kirchhoff Networks                                                                            |

| Applications                                                                                                                                      |

| Automatic Verification of Application-Tailored OSEK Kernels                                                                                       |

| Estimating Worst-case Latency of on-chip Interconnects with Formal Simulation                                                                     |

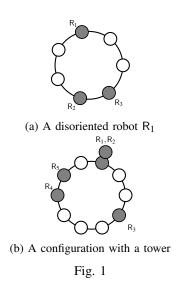

Parameterized Verification of Algorithms for Oblivious Robots on a Ring ...... 212

Freek Verbeek and Nike van Vugt-Hage

William Hallahan, Ennan Zhai and Ruzica Piskac

Arnaud Sangnier, Nathalie Sznajder, Maria Potop-Butucaru and Sebastien Tixeuil

# How formal analysis and verification add security to blockchain-based systems

Shin'ichiro Matsuo Keio University and BSafe.network

Extended Abstract of Tutorial Talk

Abstract—Blockchain is an integrated technology to ensure keeping record and process transactions with decentralized manner. It is thought as the foundation of future decentralized ecosystem, and collects much attention. However, the maturity of this technology including security of the fundamental protocol and its applications is not enough, thus we need more research on the security evaluation and verification of Blockchain technology. This tutorial explains the current status of the security of this technology, its security layers and possibility of application of formal analysis and verification.

*Index Terms*—Blockchain, Security Evaluation, Formal Method, Formal Verification, Domain Specific Language

#### I. INTRODUCTION

#### A. Background

There are proposed many applications which aim to use blockchain technology as a fundamental distributed ledger. We expect considerable commercial interest in many new and novel applications using a blockchain. In spite of this burgeoning interest, academic research on the security model of blockchain technology and its application are at an early stage. Due to the Ethereum DAO debacle, the importance of analysis of the security of blockchain-based systems is rapidly increasing. Current research issues are to find a good framework to analyze the security of blockchain technology including defining the security requirements and the way to evaluate their security. Several existing researchers deal with how to figure out the security of blockchain by using formal analysis. To facilitate this direction of research, we need a more well-organized framework.

#### B. Structure of the tutorial

In this tutorial, we firstly figure out the security requirements needed for blockchain based systems and smart contracts. Then we propose technology layers for such systems and application and security considerations for each layer. Next we explore the applicability of formal analysis for each layer and pick three layers which are good targets of evaluation by formal analysis. Then, we propose the framework of applying formal analysis to help secure blockchainbased systems. An explanation of the limitations of formal *verification* follows. At the end of this tutorial, we conclude the direction to the framework to design application code and system which facilitate formal analysis and formal verification.

#### II. SECURITY REQUIREMENTS FOR SYSTEM AND SMART CONTRACT

The security definition of blockchain backbone protocol was proposed in [1], [2]. This security definition focuses on the difficulty of forgery of the block by introducing CommonPrefix property and Chain Quality property. By using these properties, we can estimate the probability which the adversary succeeds to manipulate the blockchain. This is the requirement only for protocol specification of the backbone protocol. From the system and application viewpoints, we should care about more aspects of security. Even on the protocol security, there are many assumptions in achieving its security goals. Cryptographic protocol assumes that the private cryptographic keys are kept secret at all nodes. We should analyze if the assumption surely holds.

For the application logic, there is possibility that some critical bugs remain in the program code. An adversary takes advantage of this bug to attack the application based on blockchain. The Ethereum DAO case gives us an important study that such attack may cause a rollback and a hard fork.

From above, we should cover not only the security requirements for backbone blockchain protocol, but also all mechanisms to ensure the assumptions and scripting language and codes to realize blockchain-based applications.

#### **III. SECURITY LAYERS**

#### A. Technology layers and security consideration

In [3], Croman et al, proposed the technology layer of blockchain technology. This layers consist of network plane, consensus plane, storage plane, view plane and side plane. This structure is made to rethink the technology to provide more scalability.

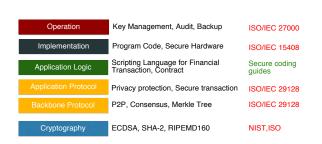

From system and application security viewpoints, we set the technology layers by the target of evaluation. They consist of cryptography layer, backbone protocol, application protocol, application logic, implementation and operation (see Fig.1).

As this figure shows, each layer has international standards to analyze the security of the security mechanisms, except application logic. Cryptography layer is covered by standardization process of ISO, NIST and many effort by the cryptographic academic community. Security of backbone protocol is analyzed by using formal analysis and UC (Universal Composability) framework and ISO/IEC 29128 [8]. The security of implementation is certified by Common Criteria

|               | Model checking       |                                          | Theorem proving                                                         |  |  |

|---------------|----------------------|------------------------------------------|-------------------------------------------------------------------------|--|--|

| Symbolic      | NRL<br>FDR<br>AVISPA | SCYTHER<br>ProVerif<br>AVISPA<br>(TA4SP) | Isabelle/HOL                                                            |  |  |

| Cryptographic |                      | CryptoVerif<br>Unt                       | BPW(in Isabelle/HOL)<br>Game-based Security<br>Proof (in Coq)<br>ounded |  |  |

Fig. 2. Categorization of Formal Analysis for cryptographic protocol

Fig. 1. Technology layers and security consideration

(ISO/IEC 15408) [7] and operation of the system is defined and audited using ISMS and the framework of ISO/IEC 27000 series. Unfortunately, the application logic layer, which contains a scripting language for financial transaction and contract, does not yet have good standard to provide security analysis. Further research here is clearly required.

#### IV. APPLYING FORMAL ANALYSIS

#### A. Abstract of formal analysis and formal verification

Here, we revisit the basis for the formal analysis and formal verification. Note that we distinguish between these two words. Formal analysis means evaluating the possibility of attack on the specification of the protocol, products or system by conducting some mathematical formalization of the security requirements, specifications and operational environment (an adversarial model). Is the description of the state spaces, axioms and changes both necessary and complete? Formal verification means to verify the correctness of the specification of the protocol, products or system formal methods such as automated axiomatic theorem proving or model checking. Formal analysis means a manner to use a mathematical formalization to evaluate the security and formal verification means checking if the specific protocol, product or system is qualified against the formal specification.

Formal analysis was originally used for check the existence of a bug in the circuit. Then it is applied to check the existence of bug in software code, design of the software and information system and security of cryptographic protocols.

#### B. State of formal analysis and checking Tools

The term formal methods refers to the use of methods for the mathematical modeling, calculation, and predication in the specification, design, analysis, construction, and assurance of hardware and software systems. These methods are distinguished as having a well-defined syntax, a semantics, and often a deductive system (or other machinery) for making semantically-sound statements about systems specified in the language of the formal method. Over the last two decades, the security community has made substantial advances in developing automated formal methods for analyzing cryptographic protocols and thereby preventing the kinds of attacks mentioned above. These methods and tools could be categorized by several points of view. Here we categorize them by "Symbolic versus Cryptographic", "Bounded versus Unbounded", and "Model checking versus Theorem proving" as Fig. 2.

#### C. Which security layer can formal method be applied?

According to the past results and history of formal analysis, the following three layers are main targets of evaluation for formal analysis.

1) Implementation: This layer contains both software and hardware implementation of security mechanisms including cryptographic algorithm, protocols and key management mechanisms. Especially, crypto-token wallet programs used in general user device may become the weakest link and should be carefully implemented. In ISO/IEC 15408, there are seven EALs(evaluation assurance levels), and EAL 6 requires semiformal analysis on the design and implementation, and EAL 7 requires fully formal analysis on the design and implementation. There are many past examples and result of formal analysis in this layer.

2) Backbone protocol and application protocol: Formal analysis on the protocol specification has a long history and it gives many results to enhance the security of cryptographic protocols. ISO/IEC 9798 and 11770 are revised from results of formal analysis [4], [5]. Recently, formal analysis on TLS1.3, the latest version of TLS protocol, helps its sound development and the result is used in the IETF standardization process [6]. Recently, combination of mathematically rigorous proof (UC Framework and game-based proof) and formal analysis are used to apply formal analysis to a wider and complicated set of protocols.

3) Language for Smart Contracts: Checking the program code is the well-known application of formal analysis and we have extensive research in this area. It is not easy to check the highly complicated program by using formal analysis, there are many existing research to realize security assured language specification. For smart contracts, we will have good application by specifically defining new languages that are designed to lend themselves to formal analysis and verification.

|                             |                |                |                           | Accuracy |  |

|-----------------------------|----------------|----------------|---------------------------|----------|--|

| Protocol<br>Assurance Level | PAL1           | PAL2           | PAL3                      | PAL4     |  |

| Protocol<br>Specification   | PPS_SEMIFORMAL | PPS_FORMAL     | PPS_MECHANIZED            |          |  |

| Adversarial<br>Model        | PAM_INFORMAL   | PAM_FORMAL     | PAM_MECHANIZED            |          |  |

| Security<br>Property        | PSP_INFORMAL   | PSP_FORMAL     | PSP_MECHANIZED            |          |  |

| Self Assessment<br>Evidence | PEV_ARGUMENT   | PEV_HANDPROVEN | EN PEV_BOUNDED PEV_UNBOUI |          |  |

#### Fig. 3. PALs in ISO/IEC 29128

#### V. PROPOSAL OF THE FRAMEWORK

#### A. Implementation

We can apply the same framework and methodology as Common Criteria (ISO/IEC 15408). Especially, wallet software or hardware should be secure against known attacking methodology like gray-box attack (side-channel attack) and white-box attack for software-only implementation. FIPS140-2 is also useful to make the framework for analyzing implementation. In this tutrial, we will provide past examples of formal analysis on the cryptographic implementation and how we can apply it to blockchain-based systems and devices.

#### B. Protocol

We can apply the same framework and methodology as ISO/IEC 29128 (verification of cryptographic protocols). It defines four PALs(Protocol Assurance Levels) according to the level of formalization for protocol specification, security requirements and operational environment. This framework covers combination of mathematical rigorous proof and formal analysis. In this tutrial, we will provide past examples of formal analysis on protocol specifications, how we write the report to align to this standard, and how we can apply it for analysis on backbone protocol and application protocol.

#### C. Language for smart contract

Analyzing the existence of bug in the program code is still fundamental research topic in computer science. We still do not have perfect results for general purpose language. The main problem is the openness of general purpose of programming language. As for the smart contract, Bhargavan et al. proposed a framework to analyze and verify both the runtime safety and the functional correctness of a Solidity contract by introducing an intermediate functional programming language suitable for verification [9]. Although the paper does not cover all EVM functionality at the time of writing this tutrial abstract, it seems a good approach to add limitation to operational environment to facilitate formal analysis.

In this tutrial, we additionally propose another approach to define a domain specific language for certain application domain, which has enough capability to write business logic and also suitable for formal verification. Then, we will present an example of the domain specific language for trade finance and trade facilitation.

#### VI. LIMITATION OF FORMAL VERIFICATION AND HOW WE FACILITATE THE USE OF IT

In this part of the tutrial, we discuss about the limitation of the formal verification. Automated and tool-aided formal verification is strong approach to check the correctness of specification and code. However, there are two major issues when we use such automated tool. The first is on the limitation of the time and memory of the computer which executes the verification. In many formal methods, the tool finds the possibility of bug and security problems by exploring as many execution states as possible. In this case, the upper bound of runtime memory of the computer and execution time become the essential limitation for complicated programs and protocols. While there are many techniques to reduce the number of states to be explored, they are not generally sufficient for complicated software implemented in a general programming language.

The second issue is the correctness of the formalization. When we use the formal verification tool, we formalize the specification (code), security goals and operational environment. The result of execution of the tool depends on the accuracy of the formalization. However, we do not have a good tool check the accuracy. For arbitrary formalized systems, we need to check the correctness by reviewing the formalized code by humans. This limits the applicability of formal verification in general. Here, we need some kind of templates and code patterns in formalization.

From above perspective, limiting the number of states by tightly defining the language and preparing code patterns or templates are good direction to facilitate the use of formal analysis and formal verification. As for the implementation, the protection profile is the actual template for formalization. In the verification of cryptographic protools, there already exists evaluation reports which aligns to ISO/IEC 29128 and they can be used as templates. As for the language for smart contract, defining a domain specific language helps to reduce the number of states to be explored and creates a template of formalization.

#### VII. CONCLUSION

In this tutrial, we proposed the way to facilitate the application of formal analysis and formal verification by considering technology layers and their security concerns. We picked three layers, implementation, protocol and language, as targets of applications of formal analysis. Then, we propose a framework to apply formal analysis to each layer by using existing standards and results. We can use the same framework as ISO/IEC15408 for implementation and ISO/IEC 29128 for protocol analysis. For the language, which was essential problem with the Ethereum DAO issue, defining a domain specific language is the new and effective solution and we showed an example for trade finance and trade facilitation. The domain specific language should have a design framework which facilitates formal analysis and, if possible, formal verification.

From the above, formal analysis research and technology development can deliver immediate value to the investments in blockchain technology with mutual benefits to all involved.

#### References

- J. Garay, A. Kiayias and N. Leonardos, "The Bitcoin Backbone Protocol: Analysis and Applications," Proceedings of Eurocrypt 2015.

- [2] R. Pass, L. Seeman and A. Shelat, "Analysis of the Blockchain Protocol in Asynchronous Networks," IACR ePrint Archive, https://eprint.iacr.org/2016/454.pdf

- [3] K. Croman, C. Decker, I. Eyal, A. Efe Gencer, A. Juels, A. Kosba, A. Miller, P. Saxena, E. Shi, E. Gün Sirer, D. Song, and R. Wattenhofer, "On Scaling Decentralized Blockchains," Proceedings of Bitcoin Workshop 2016.

- [4] C. Cremers and M. Hovert, "Improving the ISO/IEC 11770 standard for key management techniques," International Journal of Information Security, November 2016, Volume 15, Issue 6, pp 659?673.

- [5] D. Basin, C. Cremers, S, Meier, "Provably repairing the ISO/IEC 9798 standard for entity authentication," Journal of Computer Security - Security and Trust Principles, Volume 21 Issue 6, November 2013, Pages 817-846.

- [6] K. Paterson and T. van der Merwe, "Reactive and Proactive Standardisation of TLS," In Proc. of SSR 2016.

- [7] "Information technology Security techniques Evaluation criteria for IT security – Part 1: Introduction and general model," ISO/IEC 15408-1:2009

- [8] "Information technology Security techniques Verification of cryptographic protocols," ISO/IEC 29128:2011

- [9] K. Bhargavan, A. Delignat-Lavaud, C. Fournet, A. Gollamudi, G. Gonthier, N. Kobeissi, A. Rastogi, T. Sibut-Pinote, N. Swamy and S. Zanella-Béguelin "Short Paper: Formal Verification of Smart Contracts," http://www.cs.umd.edu/ aseem/solidetherplas.pdf

## Symbolic Security Analysis using the Tamarin Prover

Cas Cremers Oxford University

Abstract of Tutorial Talk

In this talk I will present the Tamarin Prover, an analysis tool for symbolic security analysis of systems. A prime example of systems that fall within its scope are security protocols that are executed in the presence of an active attacker. Tamarins state-of-the-art analysis of such systems requires dealing with unbounded replication of processes, loops, the prolific behaviour of the attacker, and equational theories to model cryptographic operations as accurately as possible within the symbolic model.

This tutorial covers Tamarins system specification, execution model, and property specification language. I will demonstrate how Tamarin can automatically analyse systems, and how its extensive interactive mode aids in the analysis of more complex systems. Finally, I will touch upon Tamarins more advanced features and larger successful case studies, such as the upcoming TLS 1.3 internet standard.

# Coalition, intrigue, ambush, destruction and pride: herding cats can be challenging.

Jade Alglave

University College London and Microsoft Research Cambridge

Abstract of Tutorial Talk

Abstract—Herding cats can lead to coalition (of cheetahs), intrigue (of kittens), ambush (of tigers), destruction (of wild cats) or pride (of lions). In this tutorial, I will present the **cat** language to write consistency models as a set of constraints on the executions of concurrent programs. A **cat** model can be executed within the herd tool [3], which I will use during the tutorial.

Concurrent programming can be difficult: how are concurrent programs supposed to behave? Do they behave correctly on exotic hardware? Formal *consistency models* can help answer these questions. Unfortunately, very often, the consistency models of the machines or operating systems we run our software on are not precisely defined. Our software itself may be written in languages whose concurrency semantics is a work in progress. To try to remedy this, the past decade has been quite rich in works aiming at describing the consistency models of hardware [20], [5], [19], [18], [6], [7], [12], [13], programming languages [10], [9], [8], [17] and more [11].

Most of these models belong to one of two formal styles: they are *operational* or *axiomatic* models. Operational models describe the executions of a concurrent program as sequences of steps: for example, reading from memory or writing to a store buffer. Axiomatic models describe executions as relations over events which represent the semantics of instructions: relations represent for example the order in which instructions are executed, or who reads from where. Both styles have advantages: operational models can be quite close to hardware designs, thus becoming a good device to communicate with hardware folks. Axiomatic models can be quite abstract, which leads to concise models and efficient verification [2].

The cat language [7] is a domain-specific language which allows the user to describe axiomatic consistency models as a set of constraints on executions. It has been used to describe hardware models such as ARMv7 and IBM Power [7], Nvidia GPUs [1], HSA GPUs [4], C++ and OpenCL [8]. More recently, ARM has released an official cat file as part of their formalisation of their ARMv8 consistency model [15]. A cat model can be executed by the herd tool [3], to answer questions about the semantics of concurrent code.

In this tutorial, I will present the cat language and the herd tool. By the end of this tutorial, you should have the skills required to build several models amongst the following: Sequential Consistency [14], Total Store Order [20], IBM Power [7], ARM [12], Nvidia GPUs [1], C++ [8] and Linux [16]. I hope to make this tutorial interactive, using the herd tool. For this to go smoothly, I would suggest downloading and installing the herd tool from http://diy.inria.fr.

#### REFERENCES

- Jade Alglave, Mark Batty, Alastair F. Donaldson, Ganesh Gopalakrishnan, Jeroen Ketema, Daniel Poetzl, Tyler Sorensen, and John Wickerson. GPU Concurrency: Weak Behaviours and Programming Assumptions. In ASPLOS 2015.

- [2] Jade Alglave, Daniel Kroening, and Michael Tautschnig. Partial orders for efficient Bounded Model Checking of concurrent software. In CAV 2013, pages 141–157.

- [3] Jade Alglave and Luc Maranget. The diy7 tool suite. http://diy.inria.fr/, 2011–2017.

- [4] Jade Alglave and Luc Maranget. Towards a formalisation of the HSA memory model in the cat language. http://www.hsafoundation.com/ ?ddownload=5381, 2015.

- [5] Jade Alglave, Luc Maranget, Susmit Sarkar, and Peter Sewell. Fences in weak memory models. In CAV 2010, pages 258–272.

- [6] Jade Alglave, Luc Maranget, Susmit Sarkar, and Peter Sewell. Fences in weak memory models (extended version). FMSD 2012, 40(2):170–205.

- [7] Jade Alglave, Luc Maranget, and Michael Tautschnig. Herding cats: Modelling, simulation, testing, and data mining for weak memory. *TOPLAS 2014*, 36(2):7:1–7:74.

- [8] Mark Batty, Alastair F. Donaldson, and John Wickerson. Overhauling SC atomics in C11 and OpenCL. In POPL 2016, pages 634–648.

- [9] Mark Batty, Kayvan Memarian, Scott Owens, Susmit Sarkar, and Peter Sewell. Clarifying and compiling C/C++ concurrency: From c++11 to POWER. In *POPL 2012*, pages 509–520.

- [10] Mark Batty, Scott Owens, Susmit Sarkar, Peter Sewell, and Tjark Weber. Mathematizing c++ concurrency. In POPL 2011, pages 55–66.

- [11] Andrea Cerone, Giovanni Bernardi, and Alexey Gotsman. A framework for transactional consistency models with atomic visibility. In CONCUR 2015, pages 58–71.

- [12] Shaked Flur, Kathryn E. Gray, Christopher Pulte, Susmit Sarkar, Ali Sezgin, Luc Maranget, Will Deacon, and Peter Sewell. Modelling the ARMv8 architecture, operationally: Concurrency and ISA. In *POPL* 2016, pages 608–621.

- [13] Shaked Flur, Susmit Sarkar, Christopher Pulte, Kyndylan Nienhuis, Luc Maranget, Kathryn E. Gray, Ali Sezgin, Mark Batty, and Peter Sewell. Mixed-size concurrency: ARM, POWER, C/C++11, and SC. In *POPL* 2017, pages 429–442.

- [14] Leslie Lamport. How to make a multiprocessor computer that correctly executes multiprocess programs. *IEEE Trans. Computers*, 28(9):690– 691, 1979.

- [15] ARM Ltd., editor. ARM Architecture Reference Manual (ARMv8, for ARMv8-A architecture profile). ARM Limited, 2017.

- [16] Paul E. McKenney, Jade Alglave, Luc Maranget, Andrea Parri, and Alan Stern. Linux-kernel memory ordering: Help arrives at last! In *LinuxCon Europe*, 2016. http://www.rdrop.com/users/paulmck/scalability/paper/ LinuxMM.2016.10.04c.LCE.pdf.

- [17] Jean Pichon-Pharabod and Peter Sewell. A concurrency semantics for relaxed atomics that permits optimisation and avoids thin-air executions. In *POPL 2016*, pages 622–633.

- [18] Susmit Sarkar, Kayvan Memarian, Scott Owens, Mark Batty, Peter Sewell, Luc Maranget, Jade Alglave, and Derek Williams. Synchronising C/C++ and POWER. In *PLDI 2012*, pages 311–322.

- [19] Susmit Sarkar, Peter Sewell, Jade Alglave, Luc Maranget, and Derek Williams. Understanding POWER multiprocessors. In *PLDI 2011*, pages 175–186.

- [20] Peter Sewell, Susmit Sarkar, Scott Owens, Francesco Zappa Nardelli, and Magnus O. Myreen. x86-TSO: a rigorous and usable programmer's model for x86 multiprocessors. *CACM* 2010, 53(7):89–97.

ISBN: 978-0-9835678-7-5. Copyright owned jointly by the authors and FMCAD, Inc.

### Automated Formal Reasoning About AWS Systems

Byron Cook

Senior Principal Engineer, Amazon Web Services Professor, University College London

#### Abstract of Invited Talk

Automatic and semiautomatic formal verification tools are now being developed and used within Amazon Web Services (AWS) to find proofs that prove or disprove desired properties of key AWS components. In this session, we outline these efforts and discuss how tools are used to play and then replay found proofs of desired properties when software artifacts or networks are modified, thus helping provide security throughout the lifetime of the AWS system.

# Formal Methods in Industrial Dependable Systems Design - The TTTech Example

Wilfried Steiner TTTech

Abstract of Invited Talk

Over the last decades the field of dependable computer systems has gained tremendous significance in our modern society. We rely on the dependability of automobiles, railways, airplanes, medical devices, critical infrastructures, like the electrical grid or industrial production facilities, and many more. These dependable systems frequently implement non-trivial mechanisms, for example, to coordinate between redundant components, and a guarantee of correctness of these mechanisms is therefore crucial to avoid catastrophic incidents. Consequently, formal methods are frequently used in industrial dependable system design and in this talk I will discuss the various aspects in which formal methods are and have been deployed for specification, verification, and configuration at TTTech for critical networking products.

### Hardware Model Checking Competition 2017

| Armin Biere        | Tom van Dijk             |

|--------------------|--------------------------|

| armin.biere@jku.at | tom.vandijk@jku.at       |

| Johannes Kepler    | University Linz, Austria |

Keijo Heljanko keijo.heljanko@aalto.fi Aalto University, Finland

The Hardware Model Checking Competition (HWMCC) 2017 affiliated to the International Conference on Formal Methods in Computer Aided Design (FMCAD) in 2017 in Vienna was the 9th competitive event for hardware model checkers we organized. After HWMCC'15 affiliated with FMCAD'15 in Austin, the competition took a break in 2016.

The competition has its roots in the model checking community with focus on hardware verification, a former central theme in International Conference on Computer-Aided Verification (CAV) and the first three incarnations of the competition in 2007, 2008 and 2010 were affiliated with CAV. This topic is now more at home at FMCAD, the primary place for research in formal methods for hardware. Accordingly the hardware model checking competition stays with FMCAD (2011,2012,2013,2015,2017) except when CAV is part of the Federated Logic Conference (FLoC) as in 2014 [4].

The goal in organizing this competition is to keep up the driving force in improving hardware model checkers. We also want to motivate implementors to present their work to a broader audience. Another important objective is to collect realistic benchmarks and to make them available to the research community. Both academia and industry is invited to submit solvers and benchmarks. Competiting model checkers have to solve benchmarks in the AIGER format [2], [3].

The competition in 2017 had multiple tracks. The most important track was the single safety property track (SINGLE). As in previous years we also had a (single) liveness property track (LIVE), and a deep bound track (DEEP), but no multiple property track. The winner of the deep bound track received an award of \$500 sponsored by Oski Technology.

The tracks were run in the same way as in the previous four incarnations of the competition, except that we were using our new cluster running Ubuntu 16.04.2 64 bit. Each cluster node had two Intel(R) Xeon(R) CPU E5-2620 v4 @ 2.10GHz CPUs and 128 GB of main memory.

Each solver had full access to both processors on one node, thus combined 16 cores (32 virtual cores) and 128 GB of main memory. Accordingly a memory limit of 120GB was enforced. As in the last competition in 2015 affiliated to FMCAD'15 we were further using a time limit of 1 hour of wall clock-time.

Also as before the number of submissions was restricted to at most two model checkers per submitter and model checkers were required to produce witnesses in the SINGLE track. These witnesses were checked by the AIGSIM tool, which is part of the AIGER tools [1].

Supported by Austrian Science Fund (FWF) NFN S11408-N23 (RiSE)

Except for the new hardware, competition rules, as well as input and output formats [2] did not change compared to previous competitions. As starting with HWMCC'12 model checkers competing in the DEEP bound track were requested to print the bounds reached during running in the SINGLE track. In the SINGLE track model checkers were required to print witnesses traces if a bad state was claimed to be reachable. These witnesses serve as certificates for satisfiable bad state properties and were checked for correctness.

Again as in HWMCC'14 and HWMCC'15, in order to avoid glitches in interpreting the format, the SINGLE track only used AIGER pre 1.9 single property benchmarks [2], with the single bad state property encoded as an output (MILOA header with O = 1). All latches were assumed to be initialized implicitly to zero as it is the default in the pre 1.9 AIGER format [2].

There was no change in the LIVE track which of course used the AIGER 1.9 format [3] nor in the DEEP track. Solvers intended to participate in the DEEP track were run in the SINGLE track and were expected to print reached bounds as in previous years (see for instance HWMCC'12).

In the previous competition HWMCC'15 we were proposing to completely switch to the AIGER 1.9 format [3] (also in the SINGLE track), add back the multiple property track, provide support for fuzzing and delta-debugging, and last but not least to establish a word-level track. However, due to lack of resources, we had to postpone these changes again.

#### REFERENCES

- [1] AIGER library and tools. http://fmv.jku.at/aiger.

- [2] A. Biere. The AIGER And-Inverter Graph (AIG) format version 20071012. Technical report, FMV Reports Series, Institute for Formal Models and Verification, Johannes Kepler University, Altenbergerstr. 69, 4040 Linz, Austria, 2007.

- [3] A. Biere, K. Heljanko, and S. Wieringa. AIGER 1.9 and beyond. Technical report, FMV Reports Series, Institute for Formal Models and Verification, Johannes Kepler University, Altenbergerstr. 69, 4040 Linz, Austria, 2011.

- [4] G. Cabodi, C. Loiacono, M. Palena, P. Pasini, D. Patti, S. Quer, D. Vendraminetto, A. Biere, and K. Heljanko. Hardware model checking competition 2014: An analysis and comparison of solvers and benchmarks. *Journal on Satisfiability, Boolean Modeling and Computation*, 9:135–172, 2014 (published 2016).

10

### The FMCAD 2017 Graduate Student Forum

Keijo Heljanko Aalto University, Finland

Abstract—The FMCAD Student Forum provides a platform for graduate students at any career stage to introduce their research to the wider Formal Methods community, and solicit feedback. In 2017, the event took place in Vienna, Austria, as integral part of the FMCAD conference. Thirteen students were invited to give a short talk and present a poster illustrating their work. The presentations covered a broad range of topics in the field of verification, such as automated reasoning, model checking of hardware, software, as well as parameterized systems, verification of concurrent programs, and checking of floating point properties.

Since 2013, the FMCAD conference features a Student Forum, providing a platform for graduate students at any career stage to introduce their research to the wider Formal Methods community. The FMCAD 2017 Graduate Student Forum follows the tradition of its predecessors, which took place in Mountain View, CA, USA in 2016 [1], Austin, Texas, USA in 2015 [2], Lausanne, Switzerland in 2014 [3], and in Portland, Oregon, USA in 2013 [4].

Graduate students were invited to submit short reports describing their ongoing research in the scope of the FMCAD conference. Based on the reviews provided by the organizing committee, 13 high quality submissions were accepted. The reviews focused on the novelty of the work, the technical maturity of the submission, and the quality and soundness of the presentation. The presentations covered a broad range of topics in the field of verification, such as automated reasoning, model checking of hardware, software, as well as parameterized systems, verification of concurrent programs, and checking of floating point properties.

The following contributions have been accepted:

- Yulia Demyanova, Thomas Pani, Helmut Veith and Florian Zuleger: *Empirical Software Metrics for Benchmarking of Verification Tools*

- Sepideh Asadi, Karine Even-Mendoza, Grigory Fedyukovich, Antti Hyvärinen, Hana Chockler and Natasha Sharygina: *HiFrog: Interpolation-based Software Verification using Theory Refinement*

- Thanh Hai Tran and Jure Kukovec: Pattern-based abstractions for parameterized model checking of distributed algorithms

- David Declerck, Sylvain Conchon and Fatiha Zaidi: A Backward Reachability Algorithm for Parameterized Systems on Weak Memory

- William Hallahan, Ruzica Piskac and Anton Xue: Building a Symbolic Execution Engine for Haskell

- Samuel Pastva: Discrete Bifurcation Analysis of Reactive Systems

- Rohit Dureja and Kristin Yvonne Rozier: From One To Many: Checking A Set Of Models

- Adrian Rebola Pardo: Satisfiability-preserving Reasoning in Software Verification

- Ákos Hajdu and Zoltan Micskei: *Towards Using Multiple Counterexamples for Abstraction Refinement*

- Yiji Zhang, Lenore Zuck and Kedar Namjoshi: An LLVM Refinement Checker and its Applications

- Andreas Fellner: *Model-based, mutation-driven test case* generation via heuristic-guided branching search

- Lucas Martinelli Tabajara: Synthesis via CNF Decomposition

- Jaideep Ramachandran: Unified Solver Strategy for Floating-Point

The 2017 student forum also featured a Best Contribution Award (based on the quality of the submission, the poster, and the presentation), announced during the conference and publicized on the FMCAD website.<sup>1</sup>

The Student Forum would not have been possible without the excellent contributions of the student authors. The generous support of the National Science Foundation and FMCAD's sponsors enabled us to subsidize the travel cost of the participating students. The help and advice of Georg Weissenbacher, FMCAD 2017 General and PC chair who organized the earlier FMCAD 2015 student forum was invaluable. Also help from Warren Hunt and Lindy Aleshire was instrumental in providing and administering the NSF grant for subsidizing travel costs.

#### REFERENCES

- H. Hojjat, "The FMCAD 2016 graduate student forum," in *Formal Methods in Computer-Aided Design (FMCAD)*. FMCAD Inc, 2016, p. 8.

- [2] G. Weissenbacher, "The FMCAD 2015 graduate student forum," in Formal Methods in Computer-Aided Design (FMCAD). FMCAD Inc, 2015, p. 8.

- [3] R. Piskac, "The FMCAD 2014 graduate student forum," in *Formal Methods in Computer-Aided Design (FMCAD)*. IEEE, 2014, p. 13.

- [4] T. Wahl, "The FMCAD graduate student forum," in Formal Methods in Computer-Aided Design (FMCAD). IEEE, 2013, pp. 16–17.

<sup>1</sup>http://www.cs.utexas.edu/users/hunt/FMCAD/FMCAD17/

# goSAT: Floating-point Satisfiability as Global Optimization

M. Ammar Ben Khadra, Dominik Stoffel, Wolfgang Kunz Department of Electrical and Computer Engineering University of Kaiserslautern, Germany {khadra,stoffel,kunz}@eit.uni-kl.de

Abstract—We introduce goSAT, a fast and publicly available SMT solver for the theory of floating-point arithmetic. We build on the recently proposed XSat solver [1] which casts the satisfiability problem to a corresponding global optimization problem. Compared to XSat, goSAT is an integrated tool combining JIT compilation of SMT formulas and NLopt, a feature-rich mathematical optimization backend. We evaluate our tool using several optimization algorithms and compare it to XSat, Z3, and MathSat. Our evaluation demonstrates promising results.

*Index Terms*—satisfiability modulo theories, decision procedure, floating-point, global optimization

#### I. INTRODUCTION

Automated bit-precise reasoning over floating-point arithmetic (FPA) is essential for a wide range of applications. For instance, test generation and program synthesis. SMT solvers are often used as a backend to implement such reasoning. Improving the support for FPA theory has been tackled in several recent works [2]–[5]. Despite these advances, the performance of SMT solvers regarding FPA theory still suffers from relatively poor scalability. Moreover, clauses involving common non-linear functions, e.g., trigonometric, remain particularly difficult. In fact, modern SMT solvers are based on DPLL(T) as their central framework. Therefore, their core SAT engines can be ineffective in deducing facts that might otherwise be "obvious" at the theory level [3]. In the following, we elaborate on two key challenges raised by FPA theory.

**Standard complexity.** The IEEE 754-2008 standard defines seven core operations that need to be correctly rounded, namely,  $\{+,-,*,/,\text{rem},\text{sqrt},\text{fma}\}$ . The result of a core operation is affected by the rounding mode, five defined modes, and whether it involves a special number  $\{\text{NaN}, \pm\infty\}$ . Also, rules for type conversion and exception handling, e.g., overflow, need to be considered.

**Tunable approximation.** FPA is an approximation of reals by definition. In practice, FPA implementations are *tunable* depending on the required performance and precision. For example, the flag -ffast-math instructs GCC to enable FP optimizations that are less precise. Moreover, a function like sin might be evaluated using a software library or a single hardware instruction with potentially different results [6]. Further, function sin might even be evaluated at compile time with correct rounding<sup>1</sup>. Therefore, sound reasoning about FPA should take into account the semantics of various approximate implementations of a single function. This can overwhelm SMT solvers particularly in the case of non-linear functions.

To address this, Fu et al. recently proposed XSat [1], an SMT solver for FPA based on mathematical optimization. XSat works by transforming a quantifier-free SMT instance  $\mathcal{F}(\vec{x})$ , where  $\vec{x} \in FP^n$ , to a corresponding objective function  $\mathcal{G}(\vec{x})$ . The latter represents a distance value that needs to be minimized by Global Optimization (GO) techniques [7]. The goal is to find an assignment  $\alpha$  satisfying  $\mathcal{G}(\alpha) = 0$ . The key advantage of XSat is that it doesn't need to explicitly encode FPA semantics. Rather, it can guide its reasoning purely by observing the outputs of  $\mathcal{G}(\vec{x})$ . Consequently, it can generally reason about any executable function. The original implementation of XSat consists of (1) a code generator that generates  $\mathcal{G}(\vec{x})$  in C language, and (2) a Python tool that invokes Basin Hopping (BH) [8], a GO algorithm built in Scipy<sup>2</sup>, to find a satisfying  $\alpha$ . Note that the C code of  $\mathcal{G}(\vec{x})$ needs to be compiled as a C extension to Python in a separate step which makes XSat difficult to use.

In this work, we build on the ideas proposed in XSat. We make a number of contributions. First, goSAT is an integrated tool that generates the objective function  $\mathcal{G}(\vec{x})$  using Just-in-Time (JIT) compilation and directly attempts to solve it on-the-fly. Second, our backend is based on the feature-rich non-linear optimization library NLopt [9]. In contrast, XSat is restricted to the BH algorithm. Third, in addition to its native solving mode, goSAT has a code generation mode similar to XSat. This enables experimenting with various optimization libraries that are not yet natively supported by goSAT. Fourth, we evaluate our tool on the same benchmarks used in XSat. We employ various GO algorithms available in NLopt and compare them with the BH algorithm. Finally, we make our tool publicly available at (https://github.com/abenkhadra/gosat).

#### II. BACKGROUND

We discuss here the theoretical basis of goSAT. Given an SMT formula  $\mathcal{F}(\vec{x})$ , where  $\vec{x} \in FP^n$ , we need to systematically derive a corresponding objective function  $\mathcal{G}(\vec{x})$ . Evaluating  $\mathcal{G}(\vec{x})$  for a particular assignment  $\alpha$  returns a distance value that becomes smaller as we get closer to the global minimum at zero. In order to establish the equivalence between

$<sup>^1</sup>GCC$  supports compile-time evaluation of built-in functions that have constant arguments since v4.3: https://gcc.gnu.org/gcc-4.3/changes.html

<sup>&</sup>lt;sup>2</sup>Popular Python library for scientific computing: https://www.scipy.org/

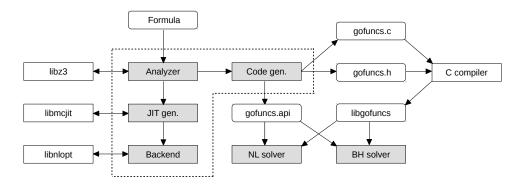

Fig. 1. goSAT architecture

satisfiability of  $\mathcal{F}(\vec{x})$  and global optimization of  $\mathcal{G}(\vec{x})$ , the function  $\mathcal{G}(\vec{x})$  must satisfy (R1)  $\forall \vec{x} \in \text{FP}^n, \mathcal{G}(\vec{x}) \ge 0$  and (R2)  $\mathcal{G}(\alpha) = 0 \Leftrightarrow \alpha \models \mathcal{F}(\vec{x})$ .

Consider  $\mathcal{F}(\vec{x})$  to be in the language  $\mathcal{L}_{fp}$  defined over quantifier-free FPA. Our  $\mathcal{L}_{fp}$  is slightly modified to that found in XSat, namely,

where  $\bowtie \in \{<, \leq, >, \geq, ==, \neq\}$ ,  $\otimes \in \{+, -, *, /\}$ , c is a floating-point constant, x is a variable, and H can be any user-defined function, e.g., logarithm.

Let  $\mathcal{F}_c(\vec{x})$  be  $\mathcal{F}(\vec{x})$  after eliminating  $\neg$  using De-Morgan's law and transforming it to CNF,

$$\mathcal{F}_c(\vec{x}) \stackrel{\text{def}}{=} \bigwedge_{i \in I} \bigvee_{j \in J} e_{i,j} \bowtie_{i,j} e'_{i,j} \tag{1}$$

we derive  $\mathcal{G}(\vec{x})$  from  $\mathcal{F}_c(\vec{x})$  as follows:

$$\mathcal{G}(\vec{x}) \stackrel{\text{def}}{=} \sum_{i \in I} \prod_{j \in J} d(\bowtie_{i,j}, e_{i,j}, e'_{i,j}) \tag{2}$$

where,

$$d(\leq, e_1, e_2) \stackrel{\text{def}}{=} e_1 \leq e_2 ? 0 : \theta(e_1, e_2)$$

(3)

$$d(<, e_1, e_2) \stackrel{\text{def}}{=} e_1 < e_2 ? 0 : \theta(e_1, e_2) + 1$$

(4)

$$d(\geq, e_1, e_2) \stackrel{\text{def}}{=} e_1 \geq e_2 ? 0 : \theta(e_1, e_2)$$

(5)

$$d(>, e_1, e_2) \stackrel{\text{def}}{=} e_1 > e_2 ? 0 : \theta(e_1, e_2) + 1$$

(6)

$$d(==,e_1,e_2) \stackrel{\text{def}}{=} \theta(e_1,e_2) \tag{7}$$

$$d(\neq, e_1, e_2) \stackrel{\text{def}}{=} e_1 \neq e_2 ? 0 : 1 \tag{8}$$

Function  $\theta(x_1, x_2)$  represents the distance between bit representations of  $x_1$  and  $x_2$ . It has the following key properties:

$$\forall x_1, x_2 \in \mathrm{FP}, \theta(x_1, x_2) \ge 0 \tag{9}$$

$$\forall x_1, x_2 \in \mathrm{FP}, \theta(x_1, x_2) = 0 \quad \Rightarrow x_1 = x_2 \tag{10}$$

$$\forall x_1, x_2 \in \operatorname{FP}, \theta(x_1, x_2) = \theta(x_2, x_1) \tag{11}$$

From equations (2) to (11), it can be shown that  $\mathcal{G}(\vec{x})$  satisfies requirements R1 and R2. Consequently, goSAT provides a sound method for proving FPA satisfiability. However, completeness of goSAT depends on the applied GO algorithm.

Generally, GO algorithms can be classified into deterministic [10] and stochastic [11]. The former are complete by providing a guarantee of finding a global minimum within a finite time. However, their applicability usually depends on the type of considered function, e.g., convex functions. Also, they often require the user to provide first and/or second derivatives (gradient and Hessian, respectively). In comparison, stochastic methods are more flexible by being applicable to functions as black box. This comes at the expense of not guaranteeing convergence to global minimum.

#### **III. IMPLEMENTATION DETAILS**

Now we discuss the implementation of goSAT. We begin with its native solving mode. Then, we move to discuss its code generation mode and helper utilities, namely, NL solver and BH solver. Finally, we discuss our choice of optimization algorithms and their parameter tuning. Our discussion will be based on Fig. 1. Highlighted components are part of our contribution. Our implementation language is C++ except for the BH solver which is written in Python.

#### A. Native solving mode

This is the default mode of goSAT where it accepts an SMT file as input. The Analyzer parses the input file using the facilities of libz3 to get an expression (expr) representing the formula. Then, the Analyzer constructs an LLVM module that contains the objective function  $\mathcal{G}(\vec{x})$ . The latter is passed to a JIT generator that traverses expr in a post-order manner in order to generate the corresponding LLVM IR. The translation process is syntax-directed resembling equations (2) to (11) discussed previously. Next, function  $\mathcal{G}(\vec{x})$  is just-intime compiled (jitted) and optimized using libmcjit from the LLVM framework. A pointer to the jitted  $\mathcal{G}(\vec{x})$  is provided to our Backend alongside other required data structures. Finally, the Backend configures and invokes libnlopt on function  $\mathcal{G}(\vec{x})$  in order to find a satisfying model.

#### B. Code generation mode

This tool mode is similar to what is implemented in XSat. We developed it in order to facilitate experimentation with GO algorithms that we still do not natively support in goSAT.

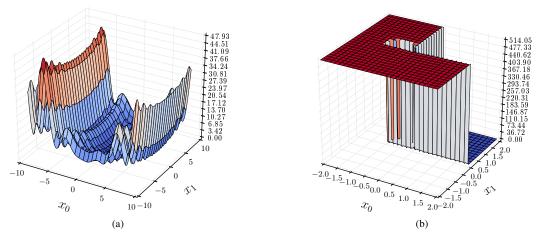

Fig. 2. Topologies of (a) levy function compared to (b) f23 function generated by goSAT. Functions generated by goSAT are non-smooth, however, they exhibit more regularity which is a key property for goSAT to work in practice.

Additionally, we provide two utilities, NL solver and BH solver, to demonstrate its use. The former depends on NLopt as its backend while the latter uses Scipy as its backend. Note that Scipy currently supports only one GO algorithm, namely, basin hopping. We were able of reproducing (most) results published in XSat using our BH Solver.

This goSAT mode is mainly implemented in the code generation component, refer to Fig. 1, which receives an expr after parsing the input formula by Analyzer. Code generation is realized using syntax-directed translation similar to the native solving mode. The output of this mode are C code and header files. These need to be compiled to obtain a shared library libgofuncs. Additionally, goSAT generates an api text file which is required to properly call the functions in libgofuncs. The api file, in its simplest forms, lists the name and dimension (variable count) of each  $\mathcal{G}(\vec{x})$ .

#### C. Optimization algorithms

We decided to use NLopt as our backend since it is publicly available and supports several derivative-free non-linear GO algorithms. There are, however, other open source packages for large-scale non-linear optimization, e.g., IpOpt [12]. Unfortunately, they generally have restrictions regarding the types of supported functions and the availability of derivatives. Note that open-source derivative-free GO algorithms still lack in performance compared to commercial implementations [13].

Our next step was to profile various GO algorithms implemented in NLopt to experiment with their efficiency and reliability. To this end, we chose several standard functions that have multiple local minima, e.g., levy, griewank, and rastrigin. These functions are commonly used for benchmarking GO algorithms [14]. We ended up choosing four promising derivative-free algorithms, namely, the deterministic algorithm DIRECT and the stochastic algorithms CRS2, ISRES, and MLSL<sup>3</sup>. Note that algorithm parameters play a crucial rule in convergence to global minima. For example, consider the levy function depicted in Fig. 2a which has a global minimum  $\mathcal{G}(\vec{x}) = 0$  for  $\vec{x} = (1, 1)$ . Basin Hopping (BH) with default parameters and an initial guess x = (-8.2, 1) was unable of "hopping" over the barrier and was trapped at a local minimum 6.056. Convergence to the global minimum required increasing the Monte-Carlo step size to 2.0. Fortunately, the transformation implemented in goSAT produces functions with more regularity. For example, consider formula £23 depicted in Fig. 2b which is taken from the Griggio benchmarks [15]. BH quickly converged to the satisfiable area using default parameters despite setting an initial guess that is far away at  $\vec{x} = (-10^9, -10^9)$ . Actually, it is easy see, from equations (3)-(8), that  $\mathcal{G}(\vec{x})$  generated by goSAT are non-smooth due to the use of conditional statements. However, they exhibit some regular structure that makes them easier to solve compared to standard GO benchmarking functions.

#### IV. EVALUATION

We evaluated goSAT on the entire Griggio benchmark set (214 instances). The GO algorithms used in the evaluation are DIRECT, CRS2, ISRES, and MLSL. In order to draw a comparison with XSat (BH algorithm), we used goSAT to generate a libgofuncs library representing the same benchmark instances. Then, we provided libgofuncs as input to our BH solver.

We "reasonably" tuned algorithm parameters in order to provide a fair comparison. The initial guess for all algorithms was set to zeros, step size to 0.5, and timeout to 600s. Each algorithm was executed once per instance. This makes BH solver achieve slightly different results to those reported in XSat. The latter uses a restart strategy using multiple initial guesses. Note that native goSAT has a small extra overhead compared to NL solver since it needs first to parse and JIT the input formula. We draw a comparison with Z3 v4.5 and MathSat v5.3.14. Both solvers were used with their default parameters. Experiments were conducted on a Linux machine with 8 GB RAM and Intel<sup>®</sup> Core i7 processors.

<sup>&</sup>lt;sup>3</sup>Please refer to NLopt algorithm documentation for further details.

TABLE I EVALUATION RESULTS

|         | sat | unsat | timeout | errors | avg. time |

|---------|-----|-------|---------|--------|-----------|

| CRS2    | 91  | 123   | 0       | 0      | 2.60      |

| ISRES   | 88  | 126   | 0       | 0      | 2.89      |

| BH      | 89  | 113   | 0       | 12     | 4.43      |

| MLSL    | 56  | 116   | 0       | 42     | 5.30      |

| DIRECT  | 45  | 169   | 0       | 0      | 13.60     |

| MathSat | 100 | 68    | 46      | 0      | 55.54     |

| Z3      | 85  | 60    | 65      | 4      | 71.39     |

Results are summarized in Tab. I. We provide the number of sat, unsat, timeout, and error instances together with the average query time in seconds (excluding timeout and error instances). Some GO algorithms faced numerical errors, e.g., round-off. Z3 encountered 4 out-of-memory exceptions. In the case of goSAT, error instances can be considered unsat since GO algorithms are generally incomplete. We used Z3 to externally validate all sat models returned by goSAT.

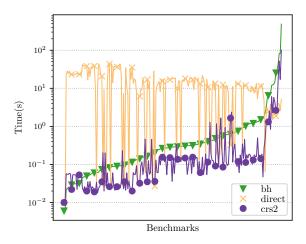

Our results provide a rough comparison since algorithm parameters can be tuned further. For instance, using the same function evaluation limit of  $5 \times 10^5$ , the deterministic DIRECT algorithm needed more time and found fewer sat instances compared to the stochastic CRS2. Fig. 3 compares the solving time of BH algorithm to CRS2 and DIRECT (fastest and slowest in goSAT respectively). Note that the performance of DIRECT varies relatively widely across the benchmarks. Also, BH needed a maximum of 488s for one instance while CRS2 was able to respond in about 25% of that time at most.

Overall, GO algorithms can provide a viable alternative to conventional SMT solvers for FPA particularly in the case of formulas involving non-linear functions. Moreover, they can assist them in special applications, e.g., in Optimization-Modulo-Theory (OMT) [16], [17]. Note, however, that SMT solvers often need to reason about multiple theories which is still not possible in goSAT. The theory of quantifier-free bitvectors (BV) can be particularly relevant in combination with FPA in the domains of software verification and synthesis. Recently, Fröhlich et al. [18] demonstrated promising results in applying stochastic search for solving BV satisfiability directly on the theory level. This provides potential ideas for combining BV and FPA to be solved using stochastic search.

#### V. CONCLUSION

We introduced goSAT, an SMT solver for the theory of FPA. In contrast to XSat, goSAT is capable of natively solving SMT formulas and is publicly available. Unlike conventional solvers, goSAT is based on mathematical optimization which enables it to reason, in principle, about any executable function. There are, however, several areas for future improvement. Most notably, we plan to exploit the particular structure of  $\mathcal{G}(\vec{x})$  generated by goSAT in order to improve solving effectiveness. Also, our restriction to derivative-free GO algorithms might be too strict. Relaxing this restriction might be possible using automatic differentiation techniques.

Fig. 3. Solving time of CRS2 and DIRECT compared to BH used in XSat.

#### REFERENCES

- Z. Fu and Z. Su, "XSat: A Fast Floating-Point Satisfiability Solver," in Computer Aided Verification (CAV'16). Springer, 2016, pp. 187–209.

- [2] K. Scheibler, F. Neubauer, A. Mahdi, M. Franzle, T. Teige, T. Bienmuller, D. Fehrer, and B. Becker, "Accurate ICP-based floating-point reasoning," in *Formal Methods in Computer-Aided Design (FMCAD'16)*. IEEE, 2016, pp. 177–184.

- [3] L. Haller, A. Griggio, M. Brain, and D. Kroening, "Deciding floatingpoint logic with systematic abstraction," in *Proceeding of Formal Methods in Computer-Aided Design (FMCAD'12)*, 2012, pp. 131–140.

- [4] A. Zeljić, C. M. Wintersteiger, and P. Rümmer, "Approximations for Model Construction," in *Proceedings of 7th International Joint Conference on Automated Reasoning (IJCAR'14)*, 2014, pp. 344–359.

- [5] M. Brain, V. D'Silva, A. Griggio, L. Haller, and D. Kroening, "Deciding floating-point logic with abstract conflict driven clause learning," *Formal Methods in System Design*, vol. 45, no. 2, pp. 213–245, 2014.

- [6] S. Duplichan, "Intel overstates FPU accuracy." [Online]. Available: http://notabs.org/fpuaccuracy/

- [7] R. Horst, P. M. Pardalos, and N. V. Thoai, *Introduction to global optimization*, 2nd ed. Springer, 2000.

- [8] D. J. Wales and J. P. K. Doye, "Global Optimization by Basin-Hopping and the Lowest Energy Structures of Lennard-Jones Clusters Containing up to 110 Atoms," *Journal of Physical Chemistry*, 1997.

- [9] S. G. Johnson, "The NLopt nonlinear-optimization package." [Online]. Available: http://ab-initio.mit.edu/nlopt

- [10] C. A. Floudas and C. E. Gounaris, "A review of recent advances in global optimization," *Journal of Global Optimization*, vol. 45, no. 1, pp. 3–38, 2009.

- [11] J. C. Spall, Introduction to Stochastic Search and Optimization. Hoboken, NJ, USA: John Wiley & Sons, Inc., mar 2003.

- [12] A. Wächter and L. T. Biegler, "On the implementation of an interiorpoint filter line-search algorithm for large-scale nonlinear programming," *Mathematical Programming*, vol. 106, no. 1, pp. 25–57, 2006.

- [13] L. M. Rios and N. V. Sahinidis, "Derivative-free optimization: a review of algorithms and comparison of software implementations," *Journal of Global Optimization*, vol. 56, no. 3, pp. 1247–1293, 2013.

- [14] M. Jamil and X. S. Yang, "A literature survey of benchmark functions for global optimisation problems," *International Journal of Mathematical Modelling and Numerical Optimisation*, vol. 4, no. 2, p. 150, 2013.

- [15] "Benchmarks of QF\_FP track in SMT-COMP (2015)." [Online]. Available: http://www.cs.nyu.edu/~barrett/smtlib/QF\_FP\_Hierarchy.zip

- [16] Y. Li, A. Albarghouthi, Z. Kincaid, A. Gurfinkel, and M. Chechik, "Symbolic optimization with SMT solvers," in *Proceedings of 41st* ACM Symposium on Principles of Programming Languages (POPL'14). ACM, 2014, pp. 607–618.

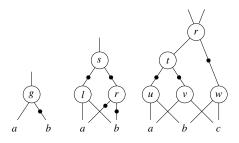

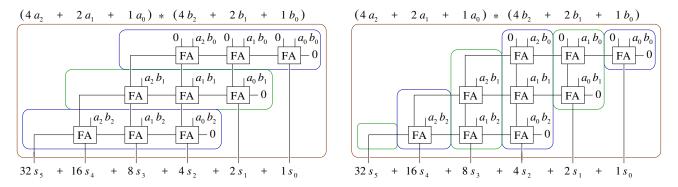

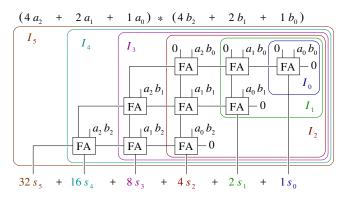

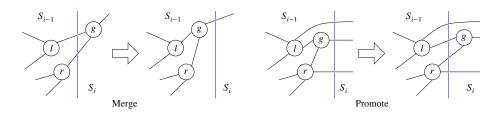

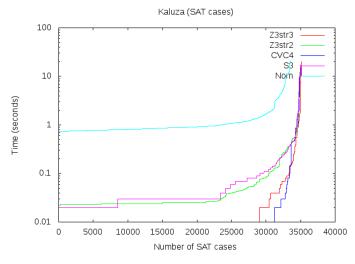

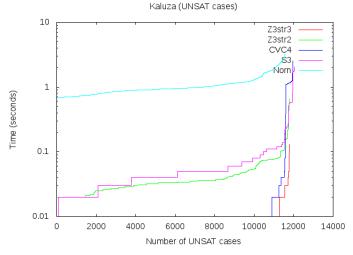

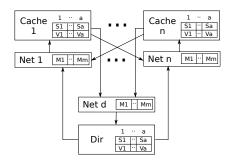

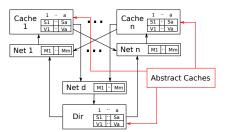

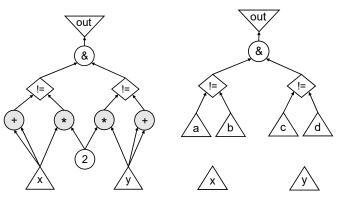

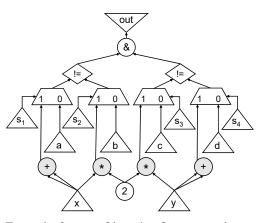

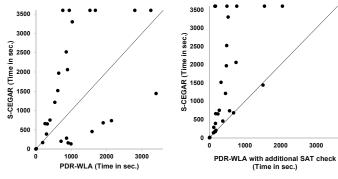

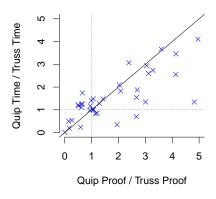

- [17] N. Bjørner, A.-D. Phan, and L. Fleckenstein, "νZ An Optimizing SMT Solver," in *International Conference on Tools and Algorithms for the Construction and Analysis of Systems*. Springer, 2015, pp. 194–199.