# Diploma Thesis

# Software Methods for Avoiding Cache Conflicts

Frank Kuehndel

August 25, 1998

Supervisor (Austin): Prof. Ph.D. Calvin Lin Supervisor (Munich): Univ.-Prof. Dr. Dr.h.c. Juergen Eickel

| I assure that I wrote this diploma thesis myself and that I used only the stated sources and tools.                               |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Ich versichere, dass ich diese Diplomarbeit selbstaendig verfasst und nur die angegebenen Quellen und Hilfsmittel verwendet habe. |

| Munich, August 25, 1998                                                                                                           |

|                                                                                                                                   |

|                                                                                                                                   |

|                                                                                                                                   |

|                                                                                                                                   |

# Acknowledgement

#### I want to thank

- Prof. Calvin Lin for many hours of discussion, for the many hints which really impoved this text and for correcting numerous spelling mistakes.

- all those people who made it possible for me to write my thesis in America. If I would write here all their names it would fill the entire page but I want to thank especially my parents and Dr. Linda Conrad from the International Office of the Technical University of Munich and Becky R. Conn from the International Office of the University of Texas at Austin.

# Abstract

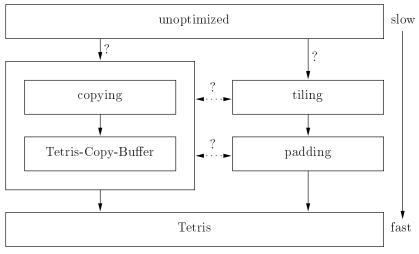

Caches improve the speed of programs by reducing the number of accesses to the slowly main memory. Unfortunately, most programs which work with arrays suffer from cache conflicts. Cache conflicts slow down the programs and counteract the advantages of the cache. The speed of affected programs can be improved by avoiding cache conflicts. This thesis concentrates on the question how to avoid cache conflicts with software methods. I describe

- the state of the art software methods

- how to pad for tiling

- a new padding algorithm (Odd-Padding)

- a new technique to avoid cache conflicts (Tetris)

- experiments which compare these techniques

Furthermore, I prove the odd-padding algorithm correct.

CONTENTS 1

# ${\bf Contents}$

| 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 2 | The State of the Art  2.1 A historically interesting paper 2.2 Finding the optimal tile size . 2.3 Copying the data into a continuous buffer 2.4 Changing the way the data is stored in memory: Padding . 2.5 Changing the way the data is stored in memory: Tetris 2.6 Changing the way the data is stored in memory for stencil operations 2.7 Other ideas . 2.8 An analysis of real programs                                                                                                                                         | 66<br>66<br>66<br>99<br>100                                        |

| 3 | The Padding for Tiling Guide 3.1 How do you start: things you should know. 3.2 How do you pad a single two-dimensional array? 3.3 How can you access that array? 3.4 How do you pad for tiles with odd base coordinates? 3.5 How do you pad for tiles with odd sizes? 3.6 How do you pad for several arrays? 3.7 How can you access several arrays? 3.8 How do you handle multi-dimensional arrays? 3.9 How do you pad for hierarchical caches? 3.10 How do you pad for stencil operations? 3.11 How do you choose a padding algorithm? | 122<br>133<br>166<br>188<br>199<br>200<br>233<br>255<br>266<br>277 |

| 4 | The Odd-Padding Proofs 4.1 The core theorem 4.2 The Odd-Padding-algorithm theorem 4.3 The Odd-Padding-formula theorem 4.4 The multi-array-access-algorithm theorem 4.5 The multi-array-access-formula theorem                                                                                                                                                                                                                                                                                                                           | 32<br>34<br>36<br>38<br>40                                         |

| 5 | The Tetris Idea 5.1 Tetris basics 5.2 Tetris access rules 5.3 Tetris mapping rules 5.4 Tetris and hierarchical caches 5.5 Tetris and multiple loops 5.6 Tetris Copy-Buffer 5.7 Tetris matrix multiplication example 5.8 Tetris — towards an algorithm                                                                                                                                                                                                                                                                                   | 45<br>46<br>46<br>47<br>48<br>50<br>51                             |

| 6 | The Experiments 3.1 Discussion of the graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>56</b> 56                                                       |

| 7 | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                 |

## 1 Introduction

One of my supervisors told me I should write here:

- caches are good

- cache conflicts are bad

- this thesis tells you how you can avoid cache conflicts with software methods

Calvin Lin

He has probably not thought of the possibility that I could cite him. Nevertheless, these few lines get really to the point, but let me explain them in more detail.

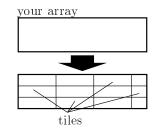

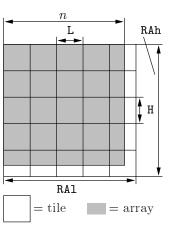

Data stored in the cache can be accessed much faster than data stored in memory. Therefore it is possible to speed up programs which deal with large arrays by *tiling*, also known as *blocking*. The idea of tiling is to work only on small blocks or tiles which do fit into the cache even if the whole array itself does not. The loops in a program are changed to work on these small tiles instead of the whole array. When the tile fits into the cache, the data once read from memory can be reused without accesses to the slower main memory.

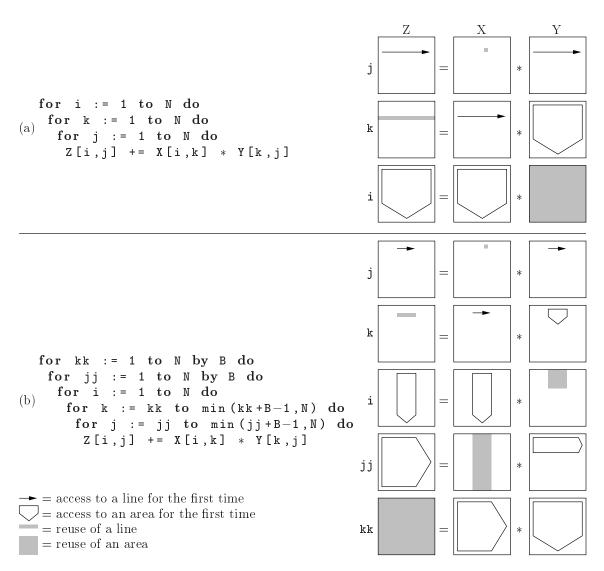

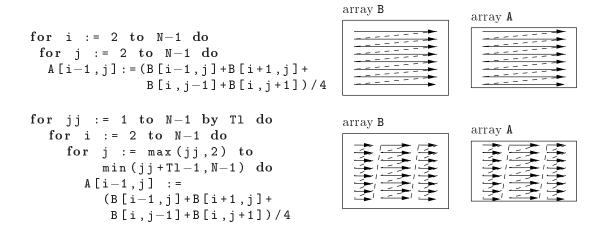

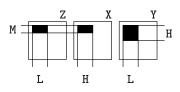

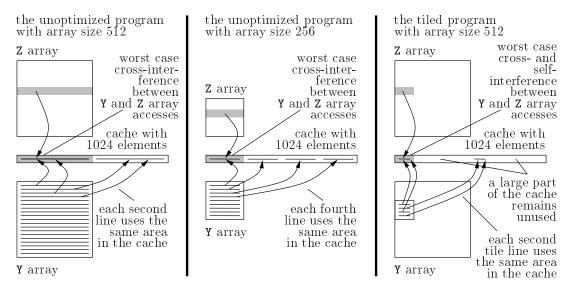

An example for tiling found in Lam et al. [3] is matrix multiplication. Figure 1 shows two versions of that algorithm, one (a) without tiling and one (b) with tiling. The tiled version can reuse a fraction of a line of the  $\bf Z$  array at the  $\bf k$  loop and a whole block of  $\bf Y$  at the  $\bf i$  loop no matter how big the matrix is. For the non-tiled version, in contrast, the cache must hold at least a line of  $\bf Z$  to be able to reuse it and a whole array to reuse  $\bf Y$ .

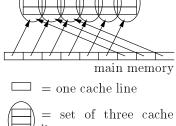

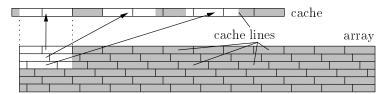

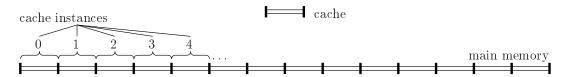

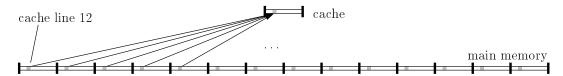

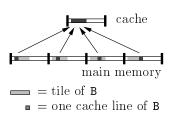

Tiling is reasonably easy to implement and, therefore, often realized. Unfortunately it is not simply a matter of choosing the tile small enough to fit into the cache. The problem is the way the cache maps memory addresses to cache lines. One may think the cache replaces the content of that cache line that was unused for the longest time. Wrong! Multi-way caches do this only for sets with a very small number of cache lines. Direct mapped caches do not do it at all. Instead caches choose the cache line by applying the modulo function. For memory address adr and cache size  $C_S$  the number of the cache line used is  $(adr \mod C_S)$ .

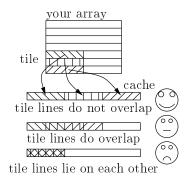

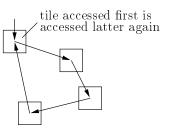

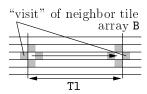

For tiling this means that whether a tile can be completely stored in the cache or not is left to chance. See the figure on the right for what may happen. Therefore, tiling must be accompanied by a method which makes sure that the whole tile is stored in the cache. This accompanying method avoids cache conflicts. Please, have a look at box 3 on page 5. It explains some words and phrases which are used in this text.

3-way cache

This paper describes methods for avoiding cache conflicts in the context of tiling. The aim of this thesis is to teach you how to avoid cache conflicts. The rest of this text is organized as follows:

**Section 2** discusses the papers that I believe are most important in this area.

Section 3 describes padding in more detail — one of the most powerful methods for avoiding cache conflicts.

This part of the text is written in a "programmer's guide" style to keep it most readable. A new algorithm (Odd-Padding) to calculate the amount of pad needed is presented, as well.

**Section 4** proves the Odd-Padding algorithm correct.

# Box 1: What is new?

Which contributions do I make to this area of Computer Science? The following list tries to give a very detailed answer.

- I describe in box 6 the *Brute-Force-Padding* algorithm. I have not seen this algorithm in another paper but it is likely that it is known because it is so simple.

- Section 3 is a *Programmer's Guide for Padding*. While other researchers do discus padding namely Panda, Nakamura, Dutt and Nicolau [5] and Rivera and Tseng [7] and others they do not go into such a level of detail and do not put all the pieces together. In particular, the discussion of the access rules (sections 3.3 and 3.7), the discussion of odd base addresses and odd tile sizes (sections 3.4 and 3.5) and the discussion of padding for hierarchical caches (section 3.9) appear here for the first time. Moreover, Rivera and Tseng [7] can not guarantee reuse when the arrays become larger than the cache, whereas I discuss only that case in section 3.10.

- The *Odd-Padding algorithm* (see box 8) is new. This includes the proofs of the algorithm (see section 4) as well as it's average and worst case behavior (see box 7).

- Everything about *Tetris* (see section 5) is completely new.

## Box 2: Variable names

$adr = {

m memory\ address}$   $C_S = {

m cache\ size}$   $T_L,\,T_H = {

m tile\ length,\ height}$   $C_L = {

m cache\ line\ size}$   $C_L = {

m cache\ line\ size}$

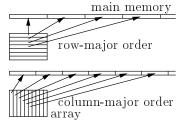

The unit of the values is usually the *cache line length*, that is, the values in the formulas are multiples of  $CL_S$  unless explicitly mentioned otherwise. All figures, formulas and programs in this paper assume row-major order memory layout of multidimensional arrays — the way C stores arrays in memory.

**Section 5** describes Tetris — a new method for avoiding cache conflicts. Tetris can handle situations where padding fails.

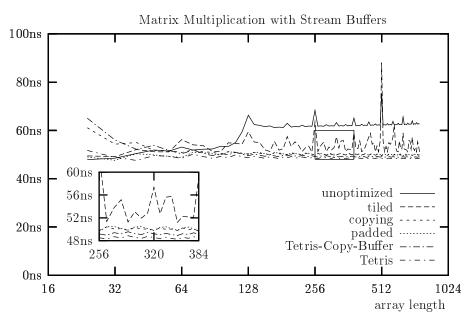

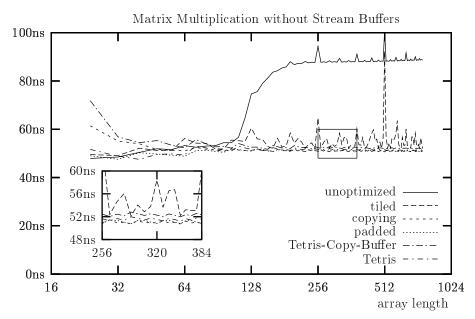

**Section 6** shows some experiments which compare the different methods.

Box 1 tells you in detail which contributions I make in this thesis. Box 2 explains some variables which I use throughout the text.

Figure 1: The original (a) and the tiled version (b) of matrix multiplication from [3]. The original must read  $2N^3 + N^2$  words from memory when the arrays are so big that not even a line can be stored in the cache (worst case). The tiled program accesses only a small tile of size B in the inner loops. If B is small enough the cache can hold this data and the program need only  $2N^3/B + N^2$  direct memory accesses.

# Box 3: Glossary

array layout see memory layout

**cache** A small but very fast memory buffer used to store data which has been read from or should be written to the main memory. The hope is that the cache speeds up programs because accesses to it are much faster than accesses to the main memory. See section 1.

cache conflicts see cache interference

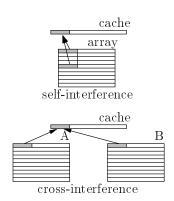

cache interference When accessing some data, other useful data is thrown out of the cache. The name *self-interference* means that data loaded into the cache throws useful data from the same variable out of the cache; in contrast, *cross-interference* occur when useful data from another variable is kicked out.

cache line When the cache reads or writes data from or to the main memory it always reads or writes a whole block — even if only one element of that block is accessed by the processor. These blocks are called *cache lines* and usually between 4 and 64 bytes long. Each cache use one certain size.

cache misses Accessed data is not in the cache and must be fetched from the main memory. Capacity misses or compulsory misses are caused intentionally, for example when moving from one tile to the next one. Conflict miss means that data is not in the cache which should be in the cache. The source of Conflict misses is cache interference.

cache thrashing The worst case cache interference is called cache thrashing. Cache thrashing happens when the processor consecutively access different memory locations which are mapped to the same cache line in the cache. This causes the cache to non-stop load a cache line from one location and throw it out immediately to replace it by a cache line from another location. Loops affected from cache thrashing are often a order of magnitude slower than unaffected loops.

data layout see memory layout

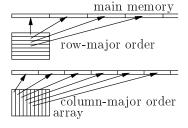

memory layout The way data — usually arrays — are stored in memory. Arrays commonly stored either in row-major order (C) or column-major order (FORTRAN). See figure at the right. The Tetris memory layout is described in section 5.1.

ping pong see cache thrashing

**reuse** Data which is accessed is in the cache. A cache line is four times *reused* if it is accessed four times while the cache line is in the cache (after it had once been loaded).

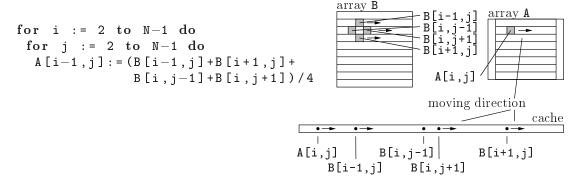

stencil operation A certain way to access arrays. See figure 6 for an example.

## 2 The State of the Art

Here I discuss papers from other researchers which I believe are the major contributions to this area. Almost all papers describe an idea to avoid cache interferences. I will try to point out the strong and the weak sides of these suggestions.

## 2.1 A historically interesting paper

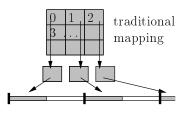

One of the first ideas to avoid cache interferences selects the tile size in such a way that there are no self-interferences. Lam, Rothberg and Wolf present an iterative algorithm in their paper [3]. Given the length of an array their algorithm tries to find the largest square tile that does not cause self-interferences. The advantage of this method is that it is not necessary to change the way the array is stored in memory (memory layout).

The disadvantage is an often very small tile so that a large part of the cache remains unused. In the worst case when the array length is a multiple of the cache size, as described in box 4, the tile size becomes one element i. e. the programmer must accept that very bad performance. Therefore, it is not surprising that Lam, Rothberg and Wolf finally came to the conclusion that the best results were obtained by copying the data which should be reused into a continuous buffer.

## 2.2 Finding the optimal tile size

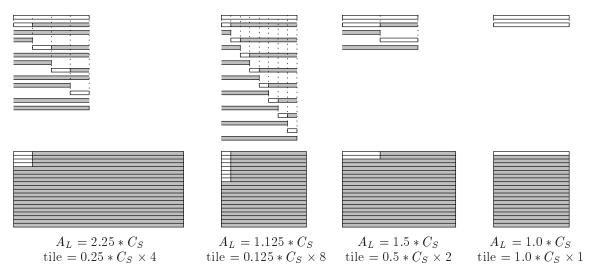

The method of Lam et al. [3] often fails to utilize large parts of the cache because it searches only for square tiles. Coleman and McKinley present an iterative algorithm [2] which searches for the biggest rectangular tile. Figures 2, 3 and 4 show how the length of an array influences the tile size. Rectangular tiles can use most or all of the cache without changing the way the data is stored in memory.

A program employing this algorithm must accept any given tile shape, which may be very small and long, or very flat. Moreover, as with the algorithm from Lam et al., Coleman and McKinley's method fails to handle the worst case where the array length is a multiple of the cache size.

#### 2.3 Copying the data into a continuous buffer

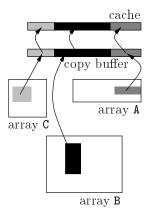

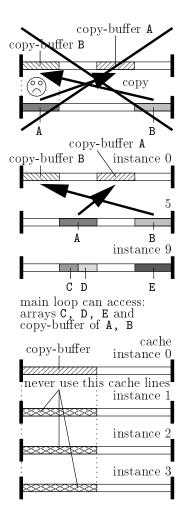

Temam, Granston and Jalby [8] suggest a way to copy the data as proposed earlier by Lam et al. [3]. The idea is to copy those data which are often accessed (reused) into a buffer. Since the buffer is continuous and not bigger than the cache, there is no cache interference possible when accessing it. Moreover, this buffer can store any data even from different variables. This way, virtually all cache interference can be avoided.

Note, however, that the copy operation itself may cause cache conflicts (interferences). Furthermore, data which is read in a loop must be copied before the loop. Data that is written or changed must be copied back after the loop. All of this slows down the program. Therefore, Temam, Granston and Jalby's algorithm analyzes the cost of copying very carefully and decides whether it is worth doing it or not in each given situation.

## 2.4 Changing the way the data is stored in memory: Padding

Instead of simply accepting the way the data is stored in memory *padding* changes the data layout by adding unused dummy elements. There are two kinds of padding:

intra-variable padding makes the lines of an array longer by adding a certain amount of dummy elements to the end of each line. Done correctly, intra-variable padding avoids self-interference and can guarantee

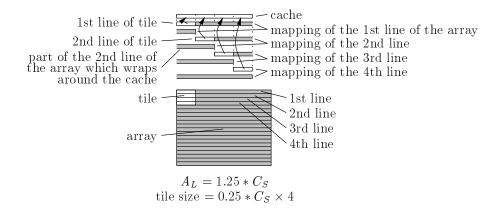

Figure 2: An array with row-major memory layout — which is the way C stores arrays — is mapped into the cache. A line of the array which reaches the end of the cache wraps around and continuous from the beginning of the cache. To distinguish between the end of one line and the beginning of the next one, there is a small vertical gap between the individual lines in the figure. A program which accesses only the white tile part of the array uses the whole cache without causing any cache interferences. Note: the maximal length of a tile  $T_L$  is  $(A_L \mod C_S)$  but a shorter tile length is often preferable. For example if  $(A_L \mod C_S)$  is greater than  $C_S/2$  the tile with maximal  $T_L$  would consist of only one single line.

Figure 3: The length of the array influences the length of a tile. Note how the array length — the number written below the arrays — results in different tile sizes. Compare this picture also to figure 2. Different methods to avoid self-interferences have been suggested. Methods which do not change the data layout like those from Lam et al. [3] and Coleman and McKinley [2] may return very small and degenerate tiles. Methods which do change the length of the array like padding from Panda et al. [5] can make any intended tile — no matter what length and height — fit into the cache, provided the cache is large enough to hold a tile of that size.

# Box 4: The worst case data layout

How much a program actually suffers from the layout of its data depends on many factors. Among these factors are the way the program accesses the data, the size of the arrays involved, the size of the tiles if it uses tiling, the start address of one array in relation to other arrays and hardware features like stream buffers. But experience has shown that two situations heavily slow down almost all programs. These situations are:

- The length of a line of an array is an exact multiple of the cache size assuming row-major order that is,  $A_L = i * C_S$  where  $i \in \mathbb{N}$ . This causes heavy self-interference because all elements of a column of that array are mapped to the very same cache line or small set of cache lines if the cache is a multi-way cache.

- The distance between the base address of two similar arrays is an exact multiple of the cache size i. e.  $|A_{adr} B_{adr}| = i * C_S$  where  $i \in \mathbb{N}$ . This can cause heavy cross-interference because elements of arrays A and B with the same coordinates are mapped to the same cache line or small set of cache lines if the cache is a multi-way cache.

These situations can be considered to be the worst case because they can slow down programs by an order of magnitude compared with programs which suffer only from a "usual" amount of cache interferences. Therefore this bad cases should, wherever possible, be avoided. Methods to avoid them are copying [8] and padding [6]. Here padding uses only a very small pad; just enough to avoid the worst case without a guarantee for reuse of specific data.

Figure 4: Here is an example where the chosen tile length is different from the maximal possible tile length. The maximal possible length  $T_L$  would be  $(A_L \mod C_S) = 0.75 * C_S$ . The fist line of this tile would use 75% of the cache, so that there wont be enough space in the cache to store a complete second line. The result would be a degenerated tile which consists of only one line and uses only three-fourth of the cache. The chosen tile length is  $T_L = 0.25 * C_S$  and the tile height  $T_H$  is four lines. Therefore this shorter tile uses the whole cache.

For convenience, the arrays in my figures start at the beginning of the cache. This is, of course, unlikely to happen in practise. The start or base address of the array may fall into any position of the cache. A tile line may even be cut off at the end of the cache and wrap around to continue at the beginning of it, so that a part of the tile line is at the end of the cache and another part at the beginning of it. However, the array base address is irrelevant for self-interference as long as it starts at a cache line border.

reusability of data. That is: data which can be reused will not be accidentally thrown out of the cache.

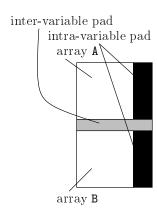

inter-variable padding changes the base or start address of a variable by adding dummy elements before that variable. Inter-variable padding changes the distance between several variables or arrays in memory and, therefore, can avoid or reduce cross-interference if done in the right way.

Despite its obvious disadvantage — wasted memory — padding is one of the most powerful techniques to avoid cache interference. Rivera and Tseng [6] present a padding technique which only avoids the worst cases, as described in box 4. Their method needs only very little "wasted memory" for padding because they do not intend to guarantee the reuseability of any data i. e. they do not care whether or not a whole tile can be stored in the cache without causing cache interference.

A much more powerful method has been presented by Panda, Nakamura, Dutt and Nicolau [5]. Their algorithm searches iteratively for the smallest intra-variable pad, so that a given tile can be accessed without self-interference. They also describe (very shortly) how to extend their method to access several arrays in the same loop by using inter-variable padding. These arrays must have the same size and must be accessed in a fairly similar way. This is a clear shortcomming of padding. Furthermore, this method uses much more memory than Rivera and Tseng's technique. Section 3 discusses padding in more detail.

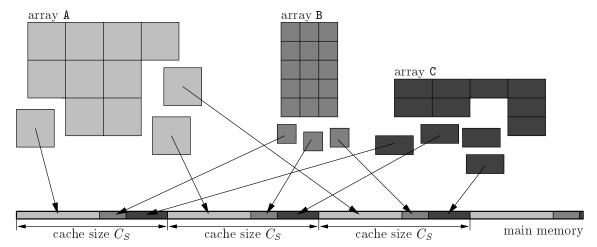

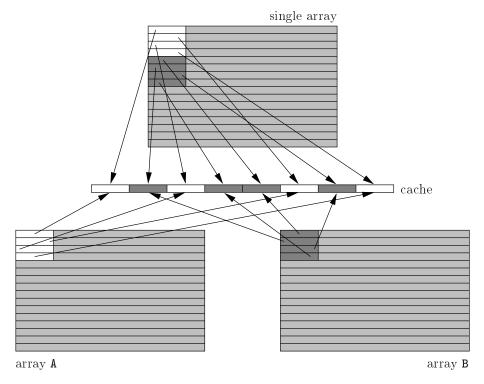

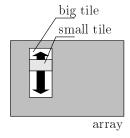

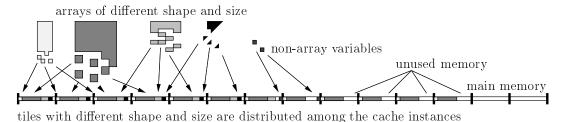

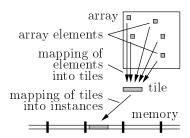

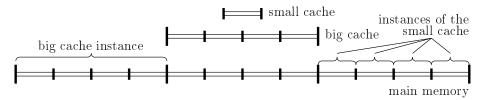

### 2.5 Changing the way the data is stored in memory: Tetris

Observe that an array which is small enough to fit completely into the cache does not cause self-interference. Therefore, the main idea is to split a big array into many small pieces. Tetris distributes the small pieces in memory in such a way that several arrays can be accessed in the same loop without causing cross-interference. This is done by dividing the memory in cache size chunks. The small pieces are then distributed into these chunks so that each chunk has a piece from each array, and the pieces always occupy the same part of the chunks. See figure 5 for an example.

The advantage is that Tetris allows accessing different arrays with different sizes, different tile sizes and different access patterns. The drawback is the relative difficulty in implementing Tetris. I recommend using padding before Tetris. Another shortcomming is its wasted memory, similar to that of padding. Tetris is described in section 5.

## 2.6 Changing the way the data is stored in memory for stencil operations

Strictly speaking, the idea described here is padding again, with an emphasis on changing the base address of the involved arrays (inter-variable padding). The difference is the way the data is accessed and reused. With tiling, a tile is selected and all data read once from memory are stored in the cache until the next tile is processed. In a stencil operation a certain access pattern (the stencil) sweeps over the whole array as shown in figure 6. The intention is to load an element of the array into the cache when the stencil first hits it and to hold it in the cache until the stencil has been moved entirely over that element.

Rivera and Tseng [7] — in an extension of their earlier work [6] — present a method which arranges several arrays in such a way that there will be as few conflicts as possible. These arrays must be accessed by stencil operations. The basic idea is to change the base addresses of the arrays in such a way that the accesses to one array are mapped into the cache without falling between accesses of some other array. Their method does not use too much dummy memory because they do intra-variable padding only for the worst case. Moreover, they fail to guarantee reuse when the length of the arrays

| <b>A</b> ■ • • • • | <b>→</b> •         | •- <b>-</b><br>B | cache<br>B       | $\bigcirc$ |

|--------------------|--------------------|------------------|------------------|------------|

| <b>•</b><br>В      | <b>A</b> ■ • • • B | •- <b>-</b><br>B | cache<br>•→<br>B | (-)        |

| в                  | A<br>► •<br>B      | •- <b>-</b><br>B | cache<br>B       | (° °)      |

Figure 5: The idea of Tetris is to split the arrays into small pieces and to uniformly distribute the pieces into memory chunks which are exactly as large as the cache.

gets large. Stencil operations can be combined with tiling and padding. Hence I describe them in more detail in section 3.

#### 2.7 Other ideas

There are many other ideas which change loops or the way the data is stored in memory (data layout). They usually neither guarantee that data once read is stored in the cache for future access (reuse) nor that there will be fewer cache conflicts. Instead, these ideas are based more on the believe that, in the general case, they will improve performance somewhat.

To represent them all I picked the paper by Cierniak and Li [1]. Their idea is to bring data that is accessed in one iteration of the inner loop as close together as possible. They change both the way the data is stored in memory and the loop interations to achieve this goal. To store an array they choose between row-major order or column-major order. Their method can handle several loops and arrays. Moreover, they show an example where changing the loops and the data layout together does give better results than either of these alone. However, they do not consider whether this leads to reuse or not.

### 2.8 An analysis of real programs

McKinley and Temam [4] analysed the cache efficiency of the Perfect Benchmarks. Here are some of their results:

- The prevalent kind of reuse in the entire program is accessing the same element of a cache line several times. In contrast the commonly held assumption says: "The reuse of other elements of a cache line is dominant."

- Loops have a more balanced reuse than whole programs. They usually access the same element again, as well as other elements of a once loaded cache line.

- When a loop causes the processor to wait for a memory access, the cause is usually a cache interference.

This is in opposition to the common assumption that a loop spends most of the time waiting for capacity misses.

Figure 6: This is a stencil operation as discussed by Rivera and Tseng in [7]. The access to array B is the stencil which is moved over the whole array. The trick is to choose the base addresses of the arrays in such a way that the A-access does not fall between the B-accesses. This way, the data once loaded from memory by B[i+1,j] can be reused three times without reading it from memory again.

Note that the array A must have the same length as B although the frame of A remains unused. If this would not be the case then the relative position of the A-access in the cache would change (minus two elements) when moving to the next line of the arrays.

- Waiting on capacity misses, occurs mainly when the processor proceeds from one loop to the next.

- The largest number of successful accesses to the cache that is: the cache holds already the data happens within loops.

- The cache fails most often when the execution moves from one loop to the next.

- In many cases only one word is accessed from a cache line and the rest remains unused. This causes bad cache utilization.

- Most accesses to memory have a very regular pattern.

Moreover, they found that the tile size chosen by tile size selection algorithms, e. g. Lam et al. [3], is too small to make tiling effective.

# 3 The Padding for Tiling Guide

Tiling or blocking is a well known technique to increase the speed of programs which work with arrays. Tiled algorithms make better use of the cache and thereby decrease the time a program needs to access its data. But tiling alone is not enough. It must be accompanied by a method which ensures that the data actually stay in the cache.

Here, I explain how you pad your arrays so that your tiled loops do not cause cache interference. I describe what can be done with padding and where padding fails. This section is written as a programmer's guide. I assume you have a program which works on arrays and you want to speed up this program by making better use of your cache. I further assume you have already tiled your loops or you are going to do so. This is not a guide for tiling! You need to know how to tile a program (see figure 1 for a tiling example).

### 3.1 How do you start: things you should know

Why do it? to make most efficient use of your time

What to do? know some tricks and tips

This is a list of general hints. These hints help you to speed up and to debug your program. They are not directly related to padding but you should consider them before you do padding.

- Analyze your program before you start to optimize it. The critical point here is to really use an analysis

tool. These tools tell you how much time your program spends in each statement. If you do not use

such a tool you will find yourself spending much time to optimize code which does not account for

much execution time.

- It is always a good idea to keep the elements of an array accessed in a loop as close together as possible. This way it is more likely that data is still or already in the cache when you access it.

- If you can combine several loops to a single one and the loops access the same arrays, do so. This makes it more likely that data is already in the cache when accessed. This is often as effective as padding and tiling.

- When you can replace an array by a smaller one or, even, by a simple variable, do so. You reduce the number of memory accesses and avoid spoiling the cache. This is often more effective than padding and tiling.

- Be sceptical about optimizations done by your compiler. Loop optimization and tiling are believed to be very well understood and, consequently, implemented in most compilers. For some reason or another compilers tend to "optimize" those loops you have already tiled and optimized by hand. This often degenerates performance.

- Let your compiler generate an assembler listing and print it on paper. No, I do not want you to understand details! Just draw an arrow from each jump or branch instruction to its destination label. This way, you should fast find the loops produced by your compiler.

- Know your hardware. When you start to optimize for your cache, you made a decision to optimize for your hardware. So know the game pieces you are playing with. It is not enough just to know how large your cache is.

- If your hardware can read and write without going through the cache, use that facility for data which is not accessed again. If you do so, you avoid spoiling the cache with data which can not be reused.

- When you optimize for a cache, optimize for the smallest top-level cache, first. It is the fastest and gives you the best speed.

# Box 5: The process of padding

Padding avoids cache conflicts by making your array longer and change it's base address. First, there are two things you need to know (see also box 8 on page 20):

- $UA_L$ : the user array length the minimum length of your array.

- $UT_L$ : the user tile length the minimum length of a tile.

Then padding tells you:

- $A_L$ : the real array length that is  $UA_L$  plus the required intra-variable pad.

- $T_L$  and  $T_H$ : the real tile length and height  $T_L$  is  $UT_L$  plus zero or more unused elements.

- $A_{adr}$  and  $B_{adr}$ : the base addresses of you arrays.

Figures 2, 3 and 4 may create the impression that your chosen array length  $UA_L$  implies a tile size  $T_L$ . The algorithms from Lam, Rothberg and Wolf [3] and Coleman and McKinley [2] actually go this way but the resulting tile size is often very degenerated.

Padding works exactly the other way around: once you have chosen your user tile length  $UT_L$  it tells you which array length  $A_L$  you should use (where  $A_L \geq UA_L$ ). That is: padding chooses you array length so that you get your intended tile size.

Depending on which padding algorithm you use, the real tile length  $T_L$  is subjected to some restrictions. Therefore, you may need to change your intended tile length  $UT_L$  to  $T_L$  so that  $T_L$  meeds the restrictions. In the text, for didactic reasons I first tell you how to calculate the array length  $A_L$  given  $T_L$  in section 3.2. Later, I describe how you find  $T_L$  given  $UT_L$  (sections 3.4 and 3.5). You need to change the base address of your arrays only if you work with several arrays. This is described in section 3.6.

- You do not need to pad arrays which are so small that they fit completely into the cache.

- Think in cache lines. Your cache works with whole cache lines not with single array elements.

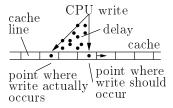

- Note that reads *and* writes slow down your program. Most people think only about read accesses when optimizing but write accesses can cause as much trouble as read accesses.

- It is exceedingly hard to debug cache behavior because you cannot see into your cache. If you do not use an analyze program you will most likely not even recognize when your program's speed is hurt by bad cache usage. A trick is to convert the addresses of the memory accesses into cache line numbers  $(adr \mod C_S)$  and to print them.

In the rest of this section I assume you have a direct mapped cache. If you have a multi-way cache, divide its size by the number of ways and use that value as cache size  $C_S$ ; e. g. a 3-way cache with 1536 cache lines gives  $C_S = 512$ . If you have several caches use the size of the smallest one. If not stated differently I assume all lengths are in cache lines — that is: the size of the cache and the length of an array or tile is given in cache lines. If your computer uses cache lines with different lengths, use the longest one. Heights are given in lines and never in cache lines.

I have no experience with virtual mapped caches. Therefore, the methods presented in this paper may or may not work for virtual mapped caches. You need to take care of what ever is necessary to make padding work with that kind of caches; consider especially the virtual page length and the table look aside buffer.

#### 3.2 How do you pad a single two-dimensional array?

Why do it? to avoid self-interference

What to do? align your array base address at a cache line border and extend the line length of the array

There are two things you need to do:

- 1. make your array start at a cache line border

- 2. extend the length of all lines of your array

In sections 3.4 and 3.5 you learn why you need to align the array at a cache line border. It is not always necessary to start an array at a cache line border (see box 6 for a counter example). On the other hand, aligning an array at a cache line border costs you only a few byte and it does not do any harm if you do it unnecessarily. Therefore, it is wise to start all arrays at a cache line border.

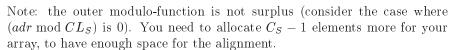

If a cache line holds  $CL_S$  elements of your array and the base address for your array is adr (in array elements) then you can calculate the next higher address which is aligned at a cache line border, using this function:

$$A_{adr}(adr, CL_S) = adr + (CL_S - (adr \bmod CL_S)) \bmod CL_S$$

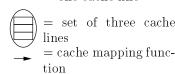

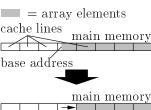

Now, you must extend the length of the lines of your array to avoid self-interference (see figure 7). I assume row-major memory layout, if your array is stored in column-major order then you need to extend the height of the columns. This kind of padding is called intra-variable padding. At the moment, there are two algorithms to select a pad length. One is described in Panda et al. [5], and the other is my invention: Odd-Padding. Here I describe the Odd-Padding algorithm.

You need to fulfill the following requirements<sup>1</sup>:

- The size of your cache<sup>2</sup> is a power of two i. e.  $C_S \in \{1, 2, 4, 8, 16, 32, 64, \ldots\}$ .

- Your cache line size is a power of two i. e.  $CL_S \in \{1, 2, 4, 8, 16, 32, 64, \ldots\}$ .

- You have chosen a tile length  $T_L$  which is also a power of two and is given in multiples of cache lines.

- You know that your array must be at least  $UA_L$  cache lines long.

Then the height of your tile — in lines — is:

$$T_H = \frac{C_S}{T_L}$$

You do not need to use all lines.  $T_H$  is just the upper maximum. The length of your array must be an odd multiple of the tile length i. e.  $A_L = iT_L$  where  $i \in \{1, 3, 5, 7, 9, 11, 13, ...\}$ . That  $A_L$  must be an odd multiple of  $T_L$  is the core of the Odd-Padding algorithm and based on a property of the modulo-function (see section 4.1 for a proof). You can use this formula to calculate such a length for your array:

$$A_L(UA_L, T_L) = UA_L + (2T_L - ((UA_L + T_L) \mod (2T_L))) \mod (2T_L)$$

The new array length  $A_L$  may be up to  $2T_LCL_S-1$  elements longer than the initial array length  $UA_L$ . (Recall:  $T_L$  is the tile size in cache lines,  $CL_S$  is the cache line size in elements.) Therefore,  $T_LCL_S$  is the tile size in elements.) Confused? How about an example?

<sup>&</sup>lt;sup>1</sup>If the first two requirements do not meet your situation, you need to look at the theorem of section 4.2 to figure out how to handle your case. Requirement three is weakened in sections 3.4 and 3.5.

$<sup>^{2}</sup>$ I assume a direct mapped cache. See the end of section 3.1 for how to calculate  $C_{S}$  if you have a multi-way cache.

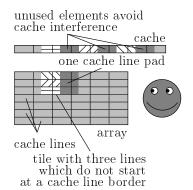

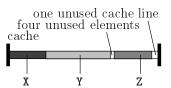

Figure 7: Here is an example of the effect of intra-variable padding. In the top figure, the array is not padded. Only two of its eight tile lines are mapped into the cache without causing cache interference. A large part of the cache remains unused.

In the bottom figure, the same array has been padded to the next odd multiple of the tile size. All tile lines are mapped into the cache without any interference and the whole cache is used.

- Example 1: Padding for a two dimensional array

Assume the following situation:

- Your cache line size  $CL_S$  is 8 elements.

- Your cache size  $C_S$  is 128 cache lines (that is 1024 elements).

- You tile length  $T_L$  is 4 cache lines.

- You want to use an array with a length of  $UA_L = 32$  cache lines and a height of 256 lines.

The padded length of your array must be an odd multiple of the tile length:

$$A_L(32,4) = 32 + (8 - ((32 + 4) \mod 8)) \mod 8 = 36$$

You need to create an array with 256 lines, each line has 36 cache lines, that is 288 elements per line. Note that  $A_L/T_L = 36/4 = 9$  is odd as required.

It remains to allocate that array and to align its base address at a cache line border. The array has  $256A_LCL_S = 73728$  elements but you need to add  $CL_S - 1 = 7$  elements for the aligning purpose, so that you allocate 73735 elements.

$$adr = alloc(73735)$$

(Note: I assume here that the alloc-function returns a physical address. If the virtual page length is a multiple of the cache size then the virtual address can be used, too.) Assume the operating system returns you address adr = 12345. You need to use the start of the next cache line as the base address of your array:

$$A_{adr}(12345, 8) = 12345 + (8 - (12345 \mod 8)) \mod 8 = 12352$$

$A_{adr} = 12352$  is the base address for your array. The size of your array is 256 lines with 288 elements. The tile length is  $T_L C L_S = 4 * 8 = 32$  elements and your tile height is  $C_S / T_L = 128/4 = 32$  lines.

This array, for example, could be the Y array of the tiled matrix multiplication from figure 1 if the tile size B is 32. Note: the cross-interference with arrays X and Z would not be avoided, only the self-interference of array Y would be removed.

For padding you must change these parts of your program: the allocation of your array as described above, all accesses to that array to take into account the new array length and the new array base address, and the loops — where possible — so that they work on your array in tiles which are  $T_LCL_S$  elements long and  $T_H$  lines high.

From the text of this section you may have correctly concluded that you can save memory by choosing the tile length  $T_L$  small. Note however that your hardware may benefit from long tiles, especially if you have stream buffers. My experience shows that short tile length degenerate program speed on computers with stream buffers.

## 3.3 How can you access that array?

Why do it? to get the optimum out of padding and tiling

What to do? know the rules about accessing your array

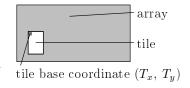

Let me first define what the tile base coordinate is. It is simple: the tile base coordinate  $(T_x, T_y)$  is the coordinate of the leftmost and topmost array element in a tile.

The basics of tiling are easy: once you access an element of a tile, the cache line which holds that element is loaded into the cache. That cache line stays in the cache until the tile is moved to some other place of the array. Therefore, you should access a once loaded cache line as often as you can before you move the tile to another position. This also implies the converse: if you access cache lines just once, tiling and padding will not improve the speed of your program.

An example for good tiling is the access to the Y array in the tiled version of the matrix multiplication algorithm from figure 1. In the i loop, all elements of the same tile of the Y array are accessed over and over again. Once for each different value of i. The elements of a tile are loaded from memory when first accessed and afterwards are always read directly from the much faster cache.

Unfortunately, things are not always so easy. Here are some rules which you need to pay attention to:

All your memory accesses must go to that tile and must stay in the

boundary of it. When you access another memory location, a cache line

belonging to the tile is kicked out of the cache and must be reloaded

from the slowly main memory when accessed later, no matter whether

you access the same array which you have tiled, another array or even a

non-array variable. In section 3.6 I tell you how to access several arrays

without causing interferences.

# Box 6: Brute-Force-Padding

Brute-Force-Padding is another method for intra-variable padding. The disadvantage of Brute-Force-Padding is that you need to use a pad up to the length of your cache minus two times the tile length. This is too much pad for Brute-Force-Padding being useful in practise. But it still may be used for theoretical considerations or in very rare programming situations.

The advantage of Brute-Force-Padding is that it can deal with odd situations. Cache size, array length and tile size must not even be multiples of a cache line size. Brute-Force-Padding chooses the array length to be either  $A_L = iC_S + T_L$  where  $i \in \mathbb{N}$  or  $A_L = iC_S - T_L$  where  $i \in \mathbb{N} \setminus \{0\}$ . Consider this all-odd-example:

cache size  $C_S = 9CL_S$ array size  $A_L = 11.75CL_S$ user tile length  $UT_L = 1.75CL_S$ real tile length  $T_L = 2.75CL_S$ possible tile base coordinates = any coordinate/no restrictions

The length of this array is a multiple of the cache size plus the length of the tile i.e.  $A_L = C_S + T_L = 9CL_S + 2.75CL_S$ . The effect is that tile line 1 is mapped precisely behind tile line 0. Tile line 2 behind tile line 1 and so on...

Furthermore, the real tile length of the example array is the user tile length plus a cache line size i. e.  $T_L = UT_L + CL_S = 1.75CL_S + 1CL_S$ . Therefore, there will always be a cache line border between the end of one line of the tile and the next one. This allows the tile base x-coordinate to start at any arbitary position and it permits the array to start at any arbitary position in a cache line.

Of course, you can create such a tile length and array length with padding. Here is how it works: (Let  $UA_L$  be the array length you want and  $UT_L$  the desired tile length, all values are given in array elements)

Consider these questions:

- 1. Does your array start at a cache line border?

- 2. Is your desired array length  $UA_L$  a multiple of the cache line size  $CL_S$ ?

- 3. Is your desired tile length  $UT_L$  a multiple of the cache line size?

- 4. Do you want to move the tile base x-coordinate only to multiples of the cache line size?

If you can answer all of the above questions with "yes" then your tile size is  $T_L = UT_L$ . If you answer some questions with "no", or if you are unsure, your must use tile size  $T_L = UT_L + CL_S$ . The maximal height of the tile is  $T_H = \lfloor C_S/T_L \rfloor$ . The length of your array must be:

$$\begin{array}{rcl} A_L & = & \textbf{if} \ t < UA_L \ \mathrm{mod} \ C_S \ \textbf{then} \ UA_L - (UA_L \ \mathrm{mod} \ C_S) + t + C_S \\ & & \textbf{else} \quad UA_L - (UA_L \ \mathrm{mod} \ C_S) + t \end{array}$$

where  $t = & \textbf{if} \ T_L < UA_L \ \mathrm{mod} \ C_S < C_S - T_L \ \textbf{then} \ C_S - T_L \ \textbf{else} \ T_L \end{array}$

Note: theorem (42) is an instance of this formula and is proven in section 4.5.

The draw back of Brute-Force-Padding is your need to add up to the length of your cache minus two times the tile length and minus one element to every array line  $A_L - UA_L \leq C_S - 2T_L - 1$ .

# Box 7: How expensive is padding?

For padding, you pay mainly with storage space. Here is how much memory you lose in the worst case (all variables are given in elements):

| cache line alignment   | all methods                                              | $CL_S-1$                                               |

|------------------------|----------------------------------------------------------|--------------------------------------------------------|

| inter-variable padding | $all\ methods$                                           | $C_S-1$                                                |

| intra-variable padding | Brute-Force-Padding<br>Odd-Padding<br>panda et al.'s DAT | $(C_S - 2T_L) - 1$<br>$2T_L - 1$<br>$(C_S - 2T_L) - 1$ |

Panda et al. [5] do not write how much pad their DAT algorithm uses in the worst case. From experiments I know that it uses much more pad in the worst case than the Odd-Padding algorithm (see also section 3.11). Since the Brute-Force-Padding algorithm would always find a solution for the parameters used in the DAT algorithm, the DAT algorithm will at least find the same solution. Therefore, I use the worst case of the Brute-Force-Padding algorithm as the worst case of the DAT algorithm.

Another important question is: how much faster will your program be? Unfortunately it is exceedingly hard to answer that question. It mainly depends on how much your program suffers from cache interference before you do padding, how your hardware works and how good your implementation of padding is — debugging cache problems is very difficult.

It would be helpful to know how much other programs win in average but padding is relatively new and I do not know any reliable data, yet. My best guess is that a padded loop will make at least 5% in most cases where padding makes sense and over 50% in very rare cases.

• The positions where you can move the tile base coordinate to are restricted. To be precise: you can move the tile y-coordinate  $T_y$  to any line you want — as long as it stays in the array, of course. If you move  $T_y$  to a far away corner of the universe, these nasty space-time-anomalies will occur and you and your computer may be swallowed by black hole. The problem is the  $T_x$  coordinate of your tile. It can only be moved to a cache line border. Since you have aligned the array base address at a cache line border — now you see why you need to do so —  $T_x$  must be a multiple of  $CL_S$ . If the base x-coordinate of a tile does not fall on a cache line border, the start of one tile line and the end of another one will fall into the same cache line and give rise to cache-interference. In sections 3.4 and 3.5 I describe how to get rid of this restriction.

Note: the frequent case where the tile is moved horizontally in such a way that the new tile starts where the old one ends is allowed because the tile length is a multiple of the cache line size.

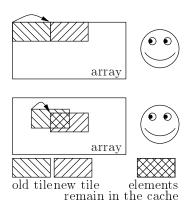

When you move the tile base coordinate to a new position, so that the old tile overlaps partly the new one, the elements in the overlapping region will stay in the cache and do not need to be reloaded.

#### 3.4 How do you pad for tiles with odd base coordinates?

Why do it? to use tiles which are not aligned at cache line borders

#### What to do? enlarge the tile by adding unused elements

What if you need to move the tile base coordinate to different positions which are not aligned at a cache line border? Assume you wish to use a tile length  $UT_L$  which is a multiple of the cache line size  $CL_S$  and not necessarily a power-of-two. The case where your intended tile length is not even a multiple of  $CL_S$  is handled in section 3.5.

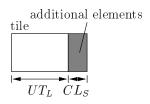

You need to make the real tile length  $T_L$  some elements longer than  $UT_L$  before you calculate the array length, using the method given in section 3.2. That is: you pad the tile length with dummy elements which you do not really use. You must make  $T_L$  at least one cache line longer than your intended tile length. That is, if  $UT_L$  and  $T_L$  are given in multiples of  $CL_S$ :

$$T_L = UT_L + 1$$

You may add more than one multiple of  $CL_S$ . This is especially helpful when you use the Odd-Padding algorithm and you need to make  $T_L$  a power of two. Note, however, that the Odd-Padding algorithm may not necessarily utilize the cache best when you do so (see the counter example on the right). You calculate the array length  $A_L$  with this new, longer  $T_L$  using the formula of section 3.2.

It is important to understand that you are not allowed to use — that is to access — these additional elements. These unused elements make sure that there is a cache line border between any tile line. Moreover, if you extend  $UT_L$  by at least one cache line size, you do not need to align your array at a cache line border because your tile base coordinates may then start at any arbitrary position.

# 3.5 How do you pad for tiles with odd sizes?

Why do it? to use tiles which are not a multiple of the cache line size

What to do? enlarge the tile by adding unused elements

My reason for including this section is to prevent people from making a simple mistake. When you have a user tile length  $UT_L$  which is not a multiple of the cache line size  $CL_S$  you cannot always choose the next multiple of the cache line size as your tile length  $T_L$ . Here, you can learn why you cannot do it and how you can find a good tile length.

In general what you need to do is: extend your intended tile length  $UT_L$  to the next multiple of  $CL_S$  and add another  $CL_S$  as pad. For example let  $UT_L$  be 22 elements and  $CL_S = 8$  elements. Extending  $UT_L$  to the next multiple of  $CL_S$  gives 24 and further adding one  $CL_S$  on it results in a real tile length of  $T_L = 4$  cache lines or 32 elements. As formula this is  $(UT_L)$  and  $CL_S$  are given in elements and  $T_L$  is given in cache lines):

$$T_L(UT_L, CL_S) = (UT_L + (CL_S - (UT_L \bmod CL_S)) \bmod CL_S))/CL_S + 1$$

As in section 3.4 you are not allowed to access these additional elements and you can add more multiples of  $CL_S$  to  $T_L$  if you want to. You can move the tile to any arbitrary base coordinate and, hence, do not need to align the array at a cache line border.

There is a special case where you do not need to add the additional cache line size. This case occurs when

$$gcd(UT_L \mod CL_S, CL_S) = (UT_L \mod CL_S)$$

and you do not move the tile base coordinate to any other position than:

$$(i(UT_L \bmod CL_S), j)$$

where  $i, j \in \mathbb{N}$

Odd-padding does not make best use of the cache when  $UT_L$  is not a power of two. Assume:  $UT_L = 5, C_S = 32$  odd-padding:  $T_L = 8, T_H = 4$  brute force padding (see box 6):  $T_L = 5, T_H = 6$  Brute force padding can utilize two tile lines more in this case.

# Box 8: Padding — a quick overview

$UT_L, UA_L$

you know your array length and your tile length

$T_L, T_H$

from your intended tile length you calculate the necessary real tile length  $T_L$  and the tile height (sections 3.4 and 3.5)

knowing  $T_L$  and  $UA_L$  you calculate the padded array length (section 3.2)

$A_{adr}, B_{adr}$

you allocate your arrays and align the first at a cache line border (section 3.2) (if necessary) and then calculate the base address of all further arrays (if any) relative to the address of the first one (section 3.6)

Note that your array must also start at such a position. If this case meets your situation, you can use this formula to calculate your tile size:

$$T_L(UT_L, CL_S) = (UT_L + (CL_S - (UT_L \bmod CL_S)) \bmod CL_S))/CL_S$$

Let me first explain this formulae and then why a smaller tile size is enough.

- Example 2: When can you use smaller tiles? -

Write  $UT_L$  as fraction — the way children do it — if there is a one on top of the fraction, after shortening, then you can use the later formula for  $T_L$ . Here are some examples:

There must be a one

| $UA_L$                        | $3.5CL_S$              | $8.25CL_S$         | $5.125CL_S$            | \$.75 <i>CL</i> €  | 5\875 <i>C L/s</i>   | 2\375 <i>C L</i> / <sub>S</sub> |

|-------------------------------|------------------------|--------------------|------------------------|--------------------|----------------------|---------------------------------|

| as fraction                   | $3\frac{0}{2}CL_S$     | $8\frac{1}{4}CL_S$ | $5\frac{1}{8}CL_S$     | $3\frac{3}{4}CL_S$ | $5\frac{1}{8}CL_{S}$ | $2\frac{3}{8}CL_S$              |

| possible base<br>x-coordinate | $\frac{1}{2}$ i $CL_S$ | $\frac{1}{4}iCL_S$ | $\frac{1}{8}$ i $CL_S$ |                    |                      |                                 |

Now, let me explain why you can use a shorter tile in some cases. A tile line with odd length uses one or two cache lines only partially, the leftmost or the rightmost or both of them. Tiles with lines which use always only one cache line partially can use shorter real tile length. Tiles which use sometimes both the leftmost and the rightmost cache line partially need a cache line more (see the example at the right). The possible x-coordinates play also a role. If the  $UT_L = 3.5CL_S$  tile could be moved in  $0.25CL_S$  steps, it would also sometimes use both cache lines at its border partially and, therefore, would need a real tile size of  $(T_L = 5)^3$ .

Note that I did not prove any of my claims of sections 3.4 and 3.5.

#### 3.6 How do you pad for several arrays?

Why do it? to avoid cross-interference when accessing several arrays in the same loop

$<sup>\</sup>overline{^3}$  For usage with the Odd-Padding algorithm you would need to use  $T_L=8$  because  $T_L$  must be a power of two.

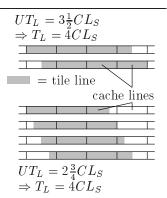

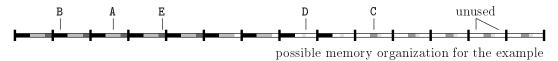

Figure 8: Here, I explain the relationship between padding for one array and padding for several arrays. All arrays in this figure are five times as long as a tile line. The cache is eight tile lines long. The padded array in figure 7 has the same relation between array length and cache size.

The tile of a single array (top) has eight lines. When using two arrays (bottom), these eight tile lines are distributed between these two arrays, so that each array has exactly four lines. Array A uses the top four tile lines of the single array and array B uses the bottom four lines. Distributing the tile lines this way avoids cross-interference between the two arrays. The trick is to find the right base address for array B.

#### What to do? pad the base address of the arrays (inter-variable padding)

The basic idea here is to distribute the available tile lines among several arrays by arranging their base address appropriately. This is done by inter-variable padding — through addition of unused elements at the begin of the array. There is a strong relation to the one-array case (see figure 8).

Assume you want to access n arrays. Let these arrays have numbers 0 (the first one) to n-1 (the last one). Each array must have the same length  $A_L$  and use the same tile length  $T_L$  and tile height  $T_H$ . Here is how you do it:

- 1. First, find the appropriate tile length  $T_L$  by referring to sections 3.4 and 3.5. If you want to use the algorithm of Panda et al. [5], a tile length which is a multiple of the cache line size  $CL_S$  will do it. If you want to use the Odd-Padding algorithm from section 3.2 you need a tile length which is a power of two.

- 2. Since you use n arrays, the height of a tile is:

$$T_H = \left\lfloor \frac{C_S}{nT_L} \right\rfloor$$

All arrays must use the same  $T_L$  and  $T_H$ .

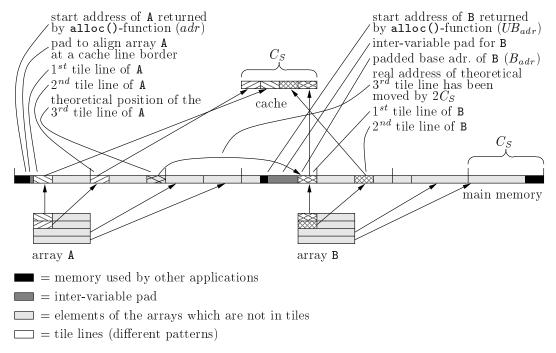

Figure 9: Inter-variable padding works by moving the base addresses of the arrays around. The arrays are three times as long as a tile and the cache is four times as long as a tile line. The long vertical lines in the main memory show where a cache mapping starts/ends. Note that the distance between the start of a cache mapping and a tile line is exactly the distance which determines where the tile line is mapped into the cache. For example the second tile line of array A starts exactly at a cache mapping begin in main memory. Consequently, it is mapped at the beginning of the cache.

The dark gray parts are inter-variable padding. For simplicisity intra-variable padding is not shown in this figure. The base address of array  ${\tt A}$  has been padded to align the array at a cache line border. The base address of array  ${\tt B}$  has been padded to the start of this theoretical  $3^{rd}$  tile line. Note that array  ${\tt B}$  is automatically aligned at a cache line border because this  $3^{rd}$  tile line starts always at whatever array  ${\tt A}$  is aligned to.

- 3. With the new tile length, calculate the array length  $A_L$ , using the Odd-Padding algorithm from section 3.2 or the method from panda et al. [5]. It is important that all arrays have the same length.

- 4. Allocate the first array (A) and align its base address  $A_{adr}$  at a cache line border:

$$A_{adr}(adr, CL_S) = adr + (CL_S - (adr \bmod CL_S)) \bmod CL_S$$

adr is the address — in array elements — which the alloc()-function of the operating system returns, when you allocate the array. You need to allocate  $C_S - 1$  elements more for your array, because the alignment leaves so much elements unused. See section 3.2 for an example. There is an exception to this rule: if you have chosen  $T_L$  appropriately and section 3.4 or 3.5 waive the requirement to align the array at a cache line border then you do not need to do it.

5. Now, you allocate the remaining arrays 1 to n-1. You calculate the base address using this formula:

$$B_{adr}(A_{adr}, UB_{adr}, o) = \mathbf{if} \ (o + A_{adr}) \bmod C_S < UB_{adr} \bmod C_S$$

$$\mathbf{then} \ UB_{adr} - UB_{adr} \bmod C_S + (o + A_{adr}) \bmod C_S + C_S$$

$$\mathbf{else} \ UB_{adr} - UB_{adr} \bmod C_S + (o + A_{adr}) \bmod C_S$$

where

$$o = (T_H A_L v) \bmod C_S$$

You must allocate  $C_S C L_S - 1$  elements more per array because so much inter-variable pad may be needed.  $UB_{adr}$  is the address the alloc()-function returns to you. v is the number of the array you are allocating (1 to n-1).  $A_{adr}$  is the padded address of the first array.

Clearly, the trick is to find the right pad for the arrays 1 to n-1. How does it work? The above  $B_{adr}$  function will result in something like  $A_{adr} + iC_S + o$ .  $iC_S$  does not matter for the cache mapping and can be ignored. Assume the case where n is 4 and the tile height  $T_H$  is 8. The resulting addresses would be:

| $A_{adr} + (0 * 8A_L) \bmod C_S$ | for array 0 |

|----------------------------------|-------------|

| $A_{adr} + (1 * 8A_L) \bmod C_S$ | for array 1 |

| $A_{adr} + (2 * 8A_L) \bmod C_S$ | for array 2 |

| $A_{adr} + (3 * 8A_L) \bmod C_S$ | for array 3 |

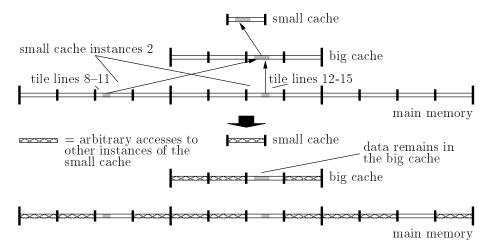

That is: array 0 uses tile lines 0–7 of a single array. Array 1 starts exactly where the  $8^{th}$  tile line of a single array would go and, therefore, uses tile lines 8–15 of that imaginary single array. Array 2 starts exactly where the  $16^{th}$  tile line of a single array would begin and uses tile lines 16–23. Array 3 uses tile lines 24-31 of that theoretical single array (enjoy also figure 9).

## 3.7 How can you access several arrays?

Why do it? to avoid cross-interference and get the maximum out of padding

What to do? know the rules

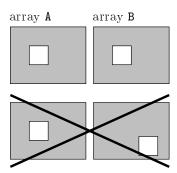

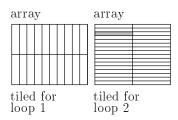

The rules are the same as those stated in section 3.3. To keep this paper small and to avoid boring the reader I do not repeat them here. There is one additional new rule when handling several arrays. This rule goes like this: For all arrays accessed at the same time, i. e. in the same loop, you must use the same base coordinate for all tiles. See figure 10 for what happens when you violate this rule. This rule is a severe restriction of the usefulness of padding. If this restriction is a problem, you my want to try one of these methods to avoid cache interference: copying (Temam et al. [8]) or Tetris.

The tile base coordinate is a concept which I introduced to explain how you must handle your arrays. It is nothing which you need to tell your hardware or operating system about. You simply access the arrays in the described way. Your hardware will then operate correctly (...er...hopefully).

## 3.8 How do you handle multi-dimensional arrays?

Why do it? to avoid cache interference when accessing arrays with more than two dimensions

What to do? chop the array into two-dimensional planes

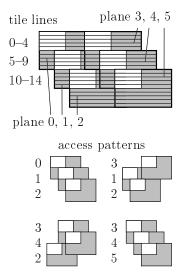

If you need to work on arrays with more than two dimensions, simply dissect them into a number of two dimensional planes and pad and access them as described in the previous sections. Sometimes you will find yourself in a situation where you need to access several — but not all — planes at once. I will show you on an example how you can handle this:

Assume you have a 3D-array with 6 planes but you access only three of them at the same time. First you access planes 0, 1 and 2. Next 1, 2, 3

cross-interference because a

tile line from each array is mapped to

same location in the cache

cache

array A

array B

Figure 10: The accesses to the arrays in this example do not use the same tile base coordinates for both arrays and, therefore, cause cache interference. Compare this with figure 8.

# Box 9: The Odd-Padding algorithm — a quick overview

- your tile length and your cache size is a power of two

- $\bullet\,$  your array and your tile start always at a cache line border

- your tile height is the cache size divided by the tile length

- your array length must be an odd multiple of your tile length

then 2, 3, 4 finally 3, 4, 5. How do you pad this? Assume your cache can hold 16 tile lines, then for three arrays each tile has a height of 5 lines and one line remains unused. Further I assume you have padded the array length appropriately.

You pad the first three planes (0, 1, 2) as if you had only these three arrays using the method described in section 3.6. You pad plane 3 using the  $B_{adr}$ -function with the same o you used for array 0. Then you pad plane 4 with the o you used for array 1 and finally you pad array 5 with the o of plane 2. The result is this:

| plane # | padded using $o$ of array | tile lines reserved |  |

|---------|---------------------------|---------------------|--|

| 0       | 0                         | 0-4                 |  |

| 1       | 1                         | 5-9                 |  |

| 2       | 2                         | 10-14               |  |

| 3       | 0                         | 0-4                 |  |

| 4       | 1                         | 5-9                 |  |

| 5       | 2                         | 10–14               |  |

This way, there will be no interference with any access combination mentioned above. For example when you access planes 2, 3, 4 then tile lines 10–14, 0–4 and 5–9 are used respectively. There are no overlapping tile lines.

## 3.9 How do you pad for hierarchical caches?

Why do it? to make best use of all caches you have

What to do? sorry, man, there is (almost) no way ...

First of all, let me clarify: in this section I discuss only padding for hierarchical tiling for *caches*. Hierarchical tiling can be used for other stuff but then it uses totally different mapping functions and, therefore, the methods described in this text do not apply.

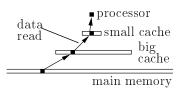

Let me assume you have two caches: a small and fast one and one which is bigger and slower but still faster than your memory. The idea behind hierarchical tiling is: to use not only the small cache but also the big one to speed up your program. You need to have or create an access pattern like this: first you access one tile, then you change the tile base coordinates and access some other tiles, later you will come back and re-access the first tile. Hierarchical tiling tries to hold the data of the first tile in the big cache, so that it need not to be read from memory when the tile is accessed the second time.

For hierarchical tiling to make sense your big cache must be

- much faster than the memory

- much bigger than the first cache (McKinley and Temam [4] found that the cache size must be made much bigger to gain a significant win.)

But this is a combination you usually do not find in real computers. The "big" cache is either small and fast or large and slow.

Nevertheless, I know possibilities to combine padding with hierarchical tiling but there is only one which makes sense to me and it is a very restricted case. I explain you that case here but my advise is to avoid hierarchical tiling as long as you have no reason to believe that it will be a great advantage in your case. Most likely you will find yourself spending much time and gaining only a small win. If you still believe hierarchical tiling is an advantage for you, consider reading about Tetris because Tetris has more powerful means to utilize several caches.

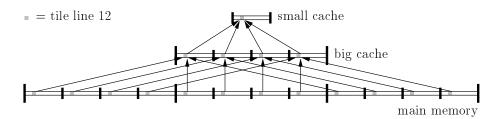

Here is how you pad for two caches: the smaller/faster cache has size  $C_S$ , and tile size  $T_H$ ,  $T_L$  with tile base coordinates  $T_x$ ,  $T_y$ . The bigger cache has size  $BC_S$  and tile size  $BT_H$ ,  $BT_L$  and tile base coordinates  $BT_x$ ,  $BT_y$ .

- The size of the big cache,  $BC_S$ , must be a power of two.

- The tile in the big cache must have the same length as the tile in the small cache, i.e.  $BT_L = T_L$ . (I told you: it is a restricted case!)

- The parameters of the small cache must meet all requirements of the Odd-Padding algorithm, that is:

- The size of your small cache is a power of two i. e.  $C_S \in \{1, 2, 4, 8, 16, 32, 64, \ldots\}$ .

- Your cache line size is a power of two i. e.  $CL_S \in \{1, 2, 4, 8, 16, 32, 64, \ldots\}$ .

- You have chosen a tile length  $T_L$  which is also a power of two and is given in multiples of cache lines.

- You know that your array must be at least  $UA_L$  cache lines long.

- You pad the length and the start address of your array using the parameters of the small cache. You must use the Odd-Padding algorithm, as described in section 3.2 or section 3.6 if you deal with several arrays.

Figure 11: The top figure shows how the untiled stencil operation processes the array. The bottom figure shows the tiled one, using tile size T1. Note that the arrays are three times  $T_L$  long but the tiled loop leaves out one element of the left and right column. Letting a tile start one element from the left is not legal because a tile must start at a cache line border.

That is all you need to do. The small and the big tile have the same length but not the same height:

$$T_H = \frac{C_S}{T_L}$$

$BT_H = \frac{BC_S}{BT_L} = \frac{BC_S}{T_L} = \frac{T_H(BC_S)}{C_S}$

You can access each tile using the rules of section 3.3 or section 3.7 if you use several arrays (in that case you need to divide  $T_H$  and  $BT_H$  by n). But you need to follow this additional rule: The small tile must always be inside the big tile, especially  $T_x = BT_x$ . When you access a cache line for the first time, the cache line is loaded into the big and the small cache. It will remain in the small cache until you change the base coordinates of the small tile. It will remain in the big cache until you change the base coordinates for the big tile, no matter how often you change the base coordinates of the small tile.

## 3.10 How do you pad for stencil operations?

Why do it? to avoid cache-interference when doing stencil operations

What to do? apply the methods of the former sections

I do not want to discuss stencil operations in general. See the paper of Rivera and Tseng [7] for a more general discussion. Instead I concentrate upon the relation between stencil operations and padding. Furthermore, I discuss only the example shown in figure 6 on page 11. Please, have a look on that figure.

If the arrays are small enough, you do not need to use tiling. For the example from figure 6, if the cache holds a little bit more than two complete lines of the arrays then tiling would be unnecessary. I assume that the arrays are greater than that, so that you must tile the loop as shown in figure 11.

How to choose  $T_L$ ? Assume you have a cache with 128 cache lines. I advise you to split your cache in four tile lines, each 32 cache lines long, as shown in the figure at the right. Then the access to  $\bf A$  and each access to a line of  $\bf B$  get an own tile line. That is a bit generous because the accesses to  $\bf B$  require only to protect the gray area from any other use but the Odd-Padding algorithm can only pad the arrays for a power of two number of

tile lines and that is four here. You could use the remaining white space for access to other arrays if you have such possibilities.

Note: the access to A is a write. In contrast to read-accesses writes may be delayed by the write back buffer of your CPU. That is: they may happen later than they appear in the program. Therefore, you need to reserve two to eight cache lines behind a write access to avoid conflicts with the next cache operation.

Tile your loop in such a way that it will use only 31 cache lines, that is: leave one cache line unaccessed. In figure 11 Tl should be  $(T_L-1)CL_S$ . The reason is that the accesses to array elements B[i,j-1] and B[i,j+1] will have a look into the neighbor tile. If you leave one cache line unused, this cache line is used for that glimpse and no useful data is thrown out of the cache.

You need to pad the whole thing as described in section 3.6. To be more precise: you first pad the length of both arrays. They will need to have the same length but not the same height. You do not need the first and last "frame" line of array A. The situation is exactly as shown in figure 6.

The array  ${\tt A}$  is the one with number 0 and is aligned at a cache line border as described in section 3.2. Then array  ${\tt B}$  is allocated (with  $C_SCL_S-1$  elements more for padding) and its base address is calculated using the  $B_{adr}$ -function from section 3.6. Here is an important difference to that section: your arrays use different tile heights therefore you use  $o=T_L$  for this  $B_{adr}$  calculation (see the picture at the right). Technical speaking you can choose any o between 1 and  $2T_L-2$  or so. This would just move the gray area with the accesses to  ${\tt B}$  around in the cache. With such o's you could also place other array accesses appropriately in the cache.

The distance between the B-accesses is defined by the array length and — since you have padded the array length — by tile length  $T_L$ . Note: I do not prove anything from this section.

# 3.11 How do you choose a padding algorithm?

For intra-variable padding you can choose between several algorithms. This is interesting because it is the kind of padding where you most likely spent most memory for. Choosing the right algorithm for intra-variable padding can save you much memory. (For inter-variable padding and cache line alignment there is only one possible method, so you do not have a choice.) You do not want to use the following techniques for padding:

Lam, Rothberg and Wolf's method [3] often utilizes only a small part of the cache. Moreover, it is not a padding technique because it tells you your tile size after you choose your array length. But most of all: you can not choose your tile size, it tells you what size you must use.

Coleman and McKinley's algorithm [2] is also not a padding technique. As Lam, Rothberg and Wolf's method [3] it tells you a tile size after you choose your array length. This tile size is rectangular and uses most of the cache but again: you can not choose your tile size or shape. You must accept whatever tile size this algorithm returns. It may be a very degenerate tile.

Rivera and Tseng's method [6] does only worst case padding. That is: they only avoid cases which are described in box 4. This technique does not guarantee you that there will be no cache interference. Consequently, you do not know which size your tile may have.

Rivera and Tseng's method [7] does only worst case padding and inter-variable padding. It is specially designed to handle stencil operations.

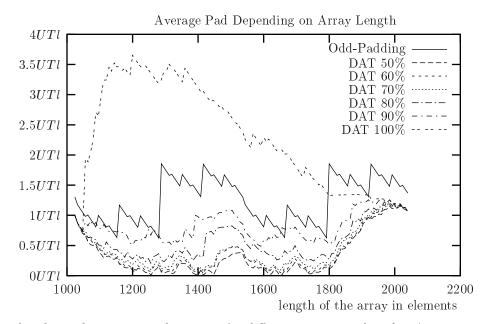

Figure 12: This plot shows the average pad required for different user array length  $UA_L$ . I assume a cache with 1024 elements and a cache line length of 8 elements. Other values of  $C_S$  and  $CL_S$  will give very similar curves. For each user array length between 1024 and 2048 — I measure one point all 8 elements — I calculate the average pad length. That is: I calculate the pad for all tile sizes between 8 elements and 256 elements in steps of 8 elements, dividing each single pad by the tile length and use the average as the value for that point. The meaning of the different percentage numbers for Panda et al.'s DAT algorithm are described in box 12.

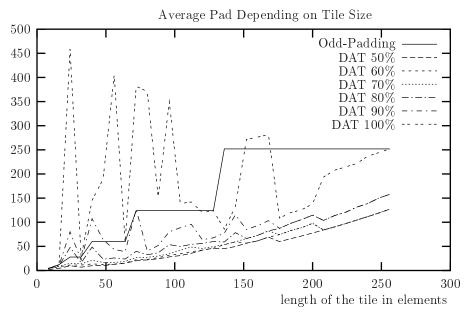

Figure 13: This plot shows the average pad for different tile length. I assume a cache with 1024 elements and a cache line length of 8 elements. Other values of  $C_S$  and  $CL_S$  will give very similar curves. For each user tile length  $UT_L$  between 8 and 256 I calculate the average pad length. For each given tile length the average pad is produced by calculating the required pads for all array lengths from 1024 to 2048 in steps of 8 elements. The meaning of the different percentage numbers for Panda et al.'s DAT algorithm are described in box 12.

# Box 10: Which one is better: Odd-Padding or DAT?

Which algorithm is better: Odd-Padding or DAT? Panda et al.'s DAT [5] algorithm is better than the Odd-Padding algorithm if you ignore the worst case behavior of DAT. Odd-Padding has been designed to handle power-of-two tile lengths when you want to utilize the whole cache. For this case the Odd-Padding algorithm finds the shortest possible pad. But the DAT algorithm finds the same pad in that case. In all other cases the Odd-Padding algorithm will perform poorly: