# COOPERATIVE HARDWARE/SOFTWARE CACHING FOR NEXT-GENERATION MEMORY SYSTEMS

A Dissertation Presented

by

ZHENLIN WANG

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

February 2004

Department of Computer Science

© Copyright by Zhenlin Wang 2004 All Rights Reserved

# COOPERATIVE HARDWARE/SOFTWARE CACHING FOR NEXT-GENERATION MEMORY SYSTEMS

A Dissertation Presented

by

## ZHENLIN WANG

| Approved as to style and content by: |          |                  |            |  |

|--------------------------------------|----------|------------------|------------|--|

|                                      |          | -                |            |  |

| Kathryn S. McKinley, Chair           |          |                  |            |  |

| Charles C. Weems, Member             |          | -                |            |  |

| J. Eliot B. Moss, Member             |          | -                |            |  |

| Csaba Andras Moritz, Member          |          | -                |            |  |

| Doug Burger, Member                  |          | -                |            |  |

|                                      | W. Bruce | e Croft, Departn | nent Chair |  |

Department of Computer Science

### **ACKNOWLEDGMENTS**

I am deeply indebted to my advisor, Kathryn McKinley, for her research guidance as well as moral support. She kindly adopted me when I joined UMass six years ago and could barely express myself in English. She has been an outstanding advisor and I have been sufficiently guided even when we only had remote contact for three years.

I must thank Eliot Moss and Chip Weems for their leadership in ALI group. They have been providing us an enjoyable research environment. A special thank goes to Chip who has been acting as my local advisor when Kathryn was a thousand miles away. Both Eliot and Chip served as members of my committee. I thank them for their thoughtful suggestions and comments. I thank Eliot for his careful reading of every detail of my dissertation.

I'd like to thank all members of ALI group, particularly James Burrill, Brendon Cahoon, Steve Blackburn, Xianglong Huang, Steve Dropso, Chris Hoffmann, Matthew Hertz, and John Cavazos, whom I always come to for help on both technical issues and English usage. It is my pleasure to work with such a wonderful team. Also I owe thanks to Benyuan Liu, Wei Wei, and Tian Bu whom I went downstairs to talk with when I was bored by research.

I enjoyed doing research with Doug Burger, Steve Reinhardt, and Csaba Andras Moritz. Their insights in system research inspired me and will benefit my career in the long run. As my committee members, Doug and Andras also suggested quite a few technical updates indispensable to my thesis.

I am grateful to Zhuoqun Xu who was my master thesis advisor in China. I built a solid background in computer science during my work with him in Beijing University.

I thank my parents who had always encouraged me to move on for a higher degree. I cannot imagine a life without the big, warm family they had created. I must thank my wife, Ruihong, and my daughter, Maggie. I could not have finished my thesis without their support, love, and forbearance.

#### **ABSTRACT**

## COOPERATIVE HARDWARE/SOFTWARE CACHING FOR NEXT-GENERATION MEMORY SYSTEMS

FEBRUARY 2004

#### **ZHENLIN WANG**

**B.S., BEIJING UNIVERSITY**

M.S., UNIVERSITY OF MASSACHUSETTS, AMHERST

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Kathryn S. McKinley

The memory system remains a major performance bottleneck in modern and future architectures. In this dissertation, we propose a hardware/software cooperative approach and demonstrate its effectiveness. This approach combines the global yet imperfect view of the compiler with the timely yet narrow-scope context of the hardware. It relies on a light-weight extension to the instruction set architecture to convey compile-time knowledge (hints) to the hardware. The hardware then uses these hints to make better decisions.

Our work shows that a cooperative hardware/software approach to (1) cache replacement, (2) prefetching, and (3) their combination eliminates or tolerates much of the memory performance bottleneck. (1) Our work enhances cache replacement decisions using compiler hints. The compiler detects which data will or will not be reused and annotates loads accordingly. The compiler sets one bit (the *evict-me* bit) to denote a preferred eviction candidate. On a miss, the cache replacement algorithm preferentially replaces a cache

vii

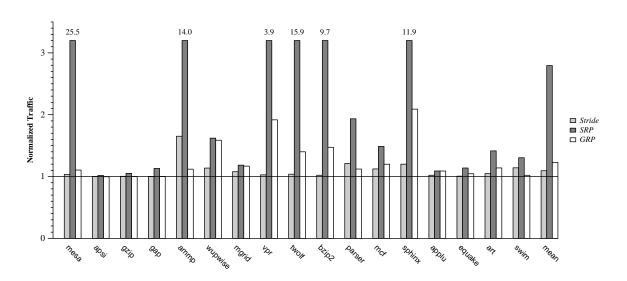

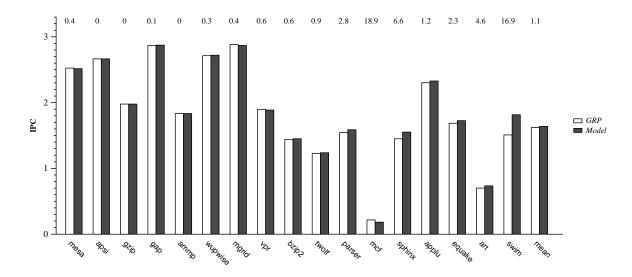

line with its evict-me bit set. Otherwise, it follows the LRU policy. The evict-me replacement scheme improves cache replacement decisions and is effective in both L1 and L2 caches. (2) We also use compiler hints to direct aggressive hardware region prefetching and content-aware pointer prefetching. The original SRP (scheduled region prefetching) engine queues prefetching requests on every outstanding L2 miss and tolerates latencies at the cost of dramatically increasing the memory traffic. GRP (guided region prefetching) enhances SRP by restricting prefetching to compiler-marked loads. Our compiler algorithms effectively mark spatial reuses across the SPEC CPU2000 benchmarks, and thus GRP achieves the performance of SRP with only one eighth of the additional traffic. (3) The evict-me cache replacement scheme helps alleviate the side effects of cache pollution introduced by useless region prefetches. The combination of evict-me caching and region prefetching further improves cache performance. These results demonstrate significant promise for overcoming the memory bottleneck with cooperative hardware/software techniques.

# TABLE OF CONTENTS

|            |                                         |        |                                                  | Page |

|------------|-----------------------------------------|--------|--------------------------------------------------|------|

| <b>A</b> ( | CKNO                                    | WLEI   | DGMENTS                                          | v    |

| ΑŦ         | BSTR                                    | ACT .  |                                                  | vii  |

| 111        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |        |                                                  |      |

| LI         | ST O                                    | F TABI | LES                                              | xiii |

| LI         | ST O                                    | F FIGU | URES                                             | xv   |

|            |                                         |        |                                                  |      |

| CI         | HAPT                                    | ER     |                                                  |      |

| 1.         | INT                                     | RODU   | CTION                                            | 1    |

|            | 1.1                                     | Our H  | ardware/Software Cooperative Approach            | 4    |

|            | 1.2                                     |        | d Cache Replacement                              |      |

|            | 1.3                                     | Guide  | d Region Prefetching                             | 7    |

|            | 1.4                                     | Comb   | ining Cache Replacement and Region Prefetching   | 9    |

|            | 1.5                                     |        | tation Organization                              |      |

|            | 1.6                                     | Summ   | nary of Contributions                            | 10   |

| 2.         | BAC                                     | CKGRO  | OUND AND RELATED WORK                            | 13   |

|            | 2.1                                     | Memo   | ory System                                       | 13   |

|            |                                         | 2.1.1  | Cache Architecture and Cache Miss Classification | 13   |

|            |                                         | 2.1.2  | DRAM Architecture                                | 15   |

|            | 2.2                                     | Impro  | ving Cache Performance                           | 17   |

|            |                                         | 2.2.1  | Program Locality                                 | 17   |

|            |                                         | 2.2.2  | Trace-based Cache Studies                        |      |

|            |                                         | 2.2.3  | Cache Miss Analysis                              | 19   |

|            |                                         | 2.2.4  | Hardware Enhancement of Cache Replacement        | 19   |

|            |                                         | 2.2.5  | Page/Cache Coloring and Data Remapping           |      |

|            |                                         | 2.2.6  | Improving Cache Locality—Program Transformations |      |

|            |                                         | 2.2.7  | Out-of-order Execution and Lock-up Free Caches   |      |

|    | 2.3               | Prefeto                          | ching Tech                               | nniques                            | 24       |

|----|-------------------|----------------------------------|------------------------------------------|------------------------------------|----------|

|    |                   | 2.3.1                            | Software                                 | Prefetching                        | 24       |

|    |                   |                                  | 2.3.1.1<br>2.3.1.2                       | Software Array Prefetching         |          |

|    |                   | 2.3.2                            | Hardwar                                  | e Prefetching                      | 29       |

|    |                   |                                  | 2.3.2.1<br>2.3.2.2<br>2.3.2.3<br>2.3.2.4 | Scheduled Region Prefetching       | 31       |

|    |                   | 2.3.3<br>2.3.4                   |                                          | e/Software Cooperative Prefetching |          |

|    | 2.4<br>2.5        |                                  | -                                        | ve Work                            |          |

| 3. | CON               | MPILE                            | R-GUIDE                                  | CD CACHE REPLACEMENT               | 45       |

|    | 3.1               | Proble                           | m Formul                                 | ation                              | 46       |

|    |                   | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4 | Perfect I<br>Reuse Lo                    | eplacement Policies                | 47       |

|    | 3.2               | Cache                            | Replacem                                 | ent Algorithms                     | 53       |

|    |                   | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4 | 16-Bit E<br>Evict-me                     | ng LRU Cache Replacement           | 58<br>63 |

|    | 3.3<br>3.4<br>3.5 | Compi                            | ler Impler                               | mentation                          | 68       |

|    |                   | 3.5.1<br>3.5.2<br>3.5.3<br>3.5.4 | URSIM<br>Experim                         | Scalar 2.0 and Experiments Setting | 72       |

|    |                   |                                  | 3.5.4.1<br>3.5.4.2                       | Miss Rates Results                 |          |

|    |            |                                                             | 3.5.4.3<br>3.5.4.4                                                                       | Simulated Performance Results                                                                                                                                                                                                                                            |                             |

|----|------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|    | 3.6        | Chapte                                                      | er Summai                                                                                | ry                                                                                                                                                                                                                                                                       | 82                          |

| 4. | CO         | MPILE                                                       | R-GUIDE                                                                                  | CD REGION PREFETCHING                                                                                                                                                                                                                                                    | 84                          |

|    | 4.1        | Hardw                                                       | are Prefet                                                                               | ching Engine                                                                                                                                                                                                                                                             | 86                          |

|    |            | 4.1.1<br>4.1.2<br>4.1.3                                     | Hardwar                                                                                  | ed Region Prefetching                                                                                                                                                                                                                                                    | 89                          |

|    |            |                                                             | 4.1.3.1<br>4.1.3.2<br>4.1.3.3<br>4.1.3.4                                                 | GRP for Spatial Region Prefetching                                                                                                                                                                                                                                       | 92                          |

|    | 4.2<br>4.3 |                                                             |                                                                                          | iler Hints                                                                                                                                                                                                                                                               |                             |

|    |            | 4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                   | Spatial L<br>Indirect .<br>Variable                                                      | Locality Analysis for Arrays                                                                                                                                                                                                                                             | 99<br>99<br>100             |

|    | 4.4<br>4.5 |                                                             |                                                                                          | nentation                                                                                                                                                                                                                                                                |                             |

|    |            | 4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5<br>4.5.6<br>4.5.7 | Compari<br>Compari<br>Prefetchi<br>Compile<br>Performa<br>Case Stu<br>4.5.7.1<br>4.5.7.2 | ental Methodology son of Region Prefetch and Pointer prefetching son of Stride Prefetching, SRP, and GRP ing Accuracy, Coverage, and Memory Traffic r Sensitivity ance Improvement and Miss Reduction dies  Remaining L2 Cache Misses Discussion of Prefetching Accuracy | 103 105 107 109 110 111 111 |

|    | 4.6        | Chapte                                                      | er Summai                                                                                | ry                                                                                                                                                                                                                                                                       | 116                         |

| 5. | CO         | MBINI                                                       | NG CACE                                                                                  | HE REPLACEMENT AND PREFETCHING                                                                                                                                                                                                                                           | 118                         |

|    | <b>5</b> 1 | I 1 Day                                                     | h Cahama                                                                                 |                                                                                                                                                                                                                                                                          | 110                         |

|    |       | 5.1.1  | Hardwa     | re Description                    | 119 |

|----|-------|--------|------------|-----------------------------------|-----|

|    |       | 5.1.2  | Results    | of the Push Scheme                | 120 |

|    |       |        | 5.1.2.1    | Push Performance                  | 120 |

|    |       |        | 5.1.2.2    | Push Accuracy and Coverage        | 121 |

|    | 5.2   | Comb   | ination of | Evict-me and Hardware Prefetching | 123 |

|    |       | 5.2.1  | Perform    | nance                             |     |

|    |       | 5.2.2  | Cache P    | Pollution                         |     |

|    |       | 5.2.3  | Discussi   | ion                               | 126 |

|    | 5.3   | Chapte | er Summa   | nry                               |     |

| 6. | CO    | NCLUS  | ION        |                                   | 128 |

|    | 6.1   | Contri | butions    |                                   | 128 |

|    | 6.2   | Future | Work       |                                   |     |

|    | 6.3   |        |            | narks                             |     |

|    |       |        |            |                                   |     |

| RI | RI IC | CRAP   | HV         |                                   | 133 |

# LIST OF TABLES

| Tabl | Page                                                    |

|------|---------------------------------------------------------|

| 1.1  | 8                                                       |

| 3.1  | LRU versus Prediction for a 2-way set-associative cache |

| 3.2  | Encoding for 16-bit reuse level                         |

| 3.3  | Associativity extension by victim cache                 |

| 3.4  | Three cache configurations                              |

| 3.5  | Static and dynamic statistics on evict-me               |

| 3.6  | Percent performance improvement by evict-me             |

| 4.1  | 86                                                      |

| 4.2  | Size distribution of pointed-to structures              |

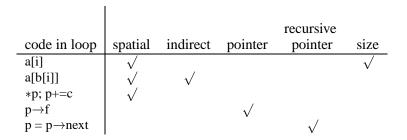

| 4.3  | Compiler hints for representative references in loops   |

| 4.4  | Bounds of memory instruction displacement fields        |

| 4.5  | Performance impact of using 12-bit displacement field   |

| 4.6  | System parameters                                       |

| 4.7  | Number of compiler hints for each benchmark             |

| 4.8  | GRP/Var versus GRP/Fix                                  |

| 4.9  | Prefetching accuracy, coverage, and memory traffic      |

| 4.10 | Level 2 miss characteristics                            |

| 5.1 | Performance impact of the L1 push scheme and placement policies 121 |

|-----|---------------------------------------------------------------------|

| 5.2 | Coverage and accuracy of the L1 push scheme, GRP/LRU plus Push/MRU  |

| 5.3 | Coverage and accuracy of the other push schemes                     |

# LIST OF FIGURES

| Figu | Page Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.1  | Processor and memory performance trend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 |

| 1.2  | Peak instructions per memory access of Intel family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3 |

| 1.3  | Processor performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3 |

| 2.1  | Conventional DRAM block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5 |

| 2.2  | Predictor-directed stream buffer architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 |

| 2.3  | Scale data flow diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 |

| 3.1  | A simple example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 |

| 3.2  | Another sample program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 |

| 3.3  | Locality graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2 |

| 3.4  | Proof of claim 2 (1. Claim 1 shows that there are no more than $w$ distinct references between time $t_j$ and time $t_i$ . 2. Claim 2 shows that if reference $f(i)$ at time $t_i$ is not a hit for the Prediction algorithm, then at time $t_k$ when $f(j) = f(i)$ is evicted, all references in the cache set should be accessed at least once between time $t_j$ and $t_i$ . (a) If a reference in the cache set at time $t_k$ was in set $X$ , it must be accessed again before time $t_i$ because it has a reuse level less than that of $f(j)$ . (b) if a reference in the cache set at time $t_k$ was not in $X$ , then it must be recently accessed after time $t_j$ . Otherwise, it must be in set $Y$ and should be evicted before the eviction of $f(j)$ at time $t_k$ . It will then not appear in the cache set at time $t_k$ .) | 5 |

| 3.5  | A sample loop nest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ) |

| 3.6  | 16-bit reuse-level generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ) |

| 3.7  | Reuse levels for the sample program 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 |

| 3.8  | Update function                                          |

|------|----------------------------------------------------------|

| 3.9  | Algorithms for computing data volume in a nest           |

| 3.10 | Algorithm for setting evict-me tag                       |

| 3.11 | Vpenta                                                   |

| 3.12 | Liv1874                                                  |

| 3.13 | Appsp                                                    |

| 3.14 | Tomcatv                                                  |

| 3.15 | Swim                                                     |

| 3.16 | Jacobi                                                   |

| 3.17 | Erlebacher                                               |

| 3.18 | Arc2d                                                    |

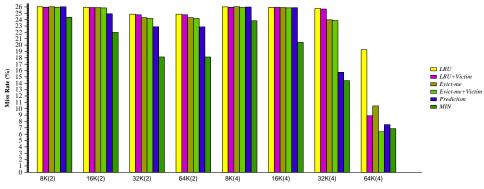

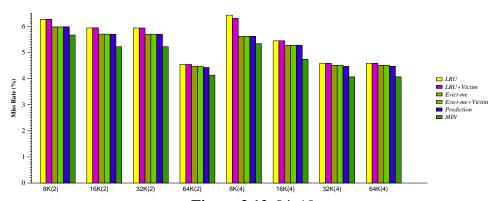

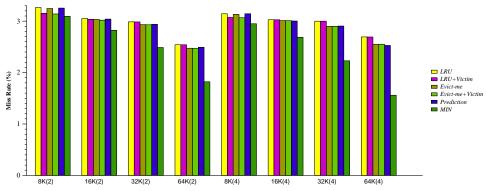

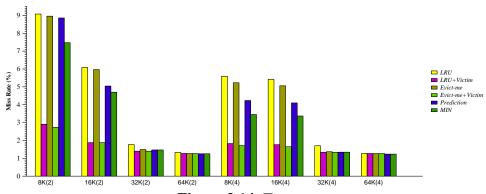

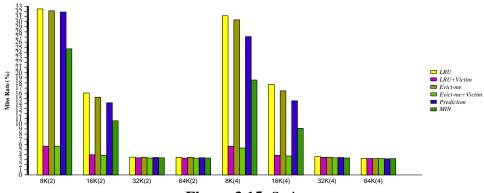

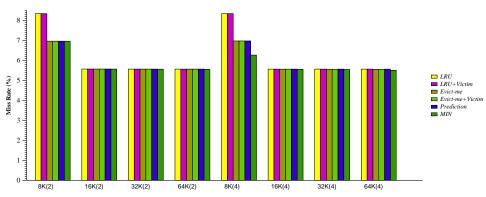

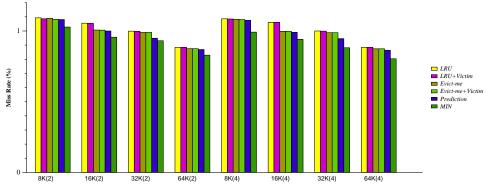

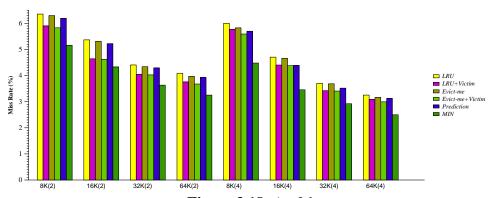

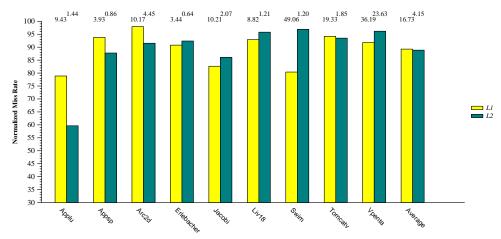

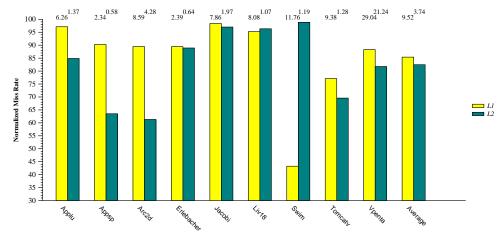

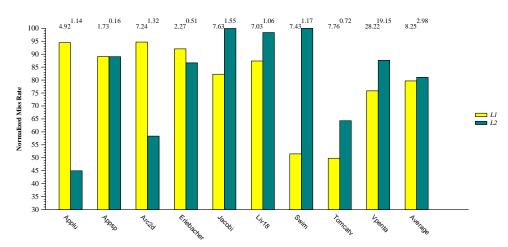

| 3.19 | Miss reduction by evict-me (Conf. 1)                     |

| 3.20 | Miss reduction by evict-me (Conf. 2)                     |

| 3.21 | Miss reduction by evict-me (Conf. 3)                     |

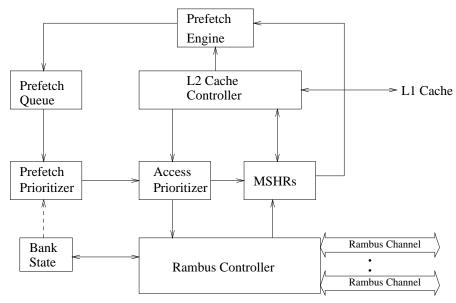

| 4.1  | Prefetch engine organization                             |

| 4.2  | Fortran array                                            |

| 4.3  | C heap array                                             |

| 4.4  | C induction pointer                                      |

| 4.5  | C recursive pointer                                      |

| 4.6  | Algorithm for generating spatial hints                   |

| 4.7  | Algorithm generating pointer and recursive pointer hints |

| 18   | Performance gains from pointer prefetching 104           |

| 4.9  | Code segment in 183.equake (quake.c)                                                           |

|------|------------------------------------------------------------------------------------------------|

| 4.10 | Code segment in 181.mcf (mcfutil.c)                                                            |

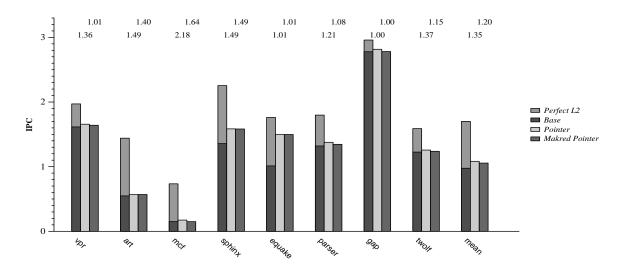

| 4.11 | Pointer vs. marked pointer prefetching                                                         |

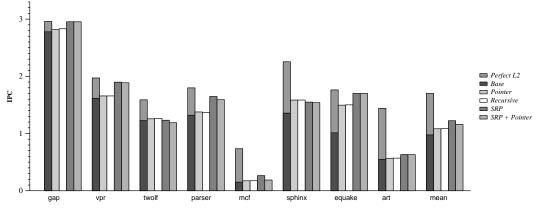

| 4.12 | Performance gains from region prefetching and stride prefetching for integer benchmarks        |

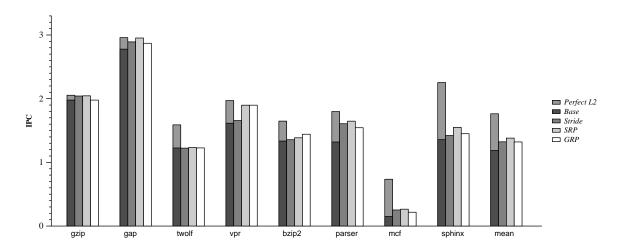

| 4.13 | Performance gains from region prefetching and stride prefetching for floating-point benchmarks |

| 4.14 | Normalized traffic                                                                             |

| 4.15 | Miss reduction versus performance improvement                                                  |

| 4.16 | Code segment in 168.wupwise                                                                    |

| 4.17 | Code segment in 181.mcf                                                                        |

| 4.18 | Code segment in 300.twolf                                                                      |

| 4.19 | Code segment in 188.ammp                                                                       |

| 4.20 | Code segment in 175.vpr                                                                        |

| 4.21 | Code segment in 256.bzip2                                                                      |

| 5.1  | Evict-me and GRP                                                                               |

| 5.2  | Cache pollution                                                                                |

#### CHAPTER 1

## INTRODUCTION

In this dissertation we propose a hardware/software cooperative approach to improve computer system performance. We demonstrate that this approach is very effective and promising for the memory system, improving cache replacement, data prefetching, and their combination.

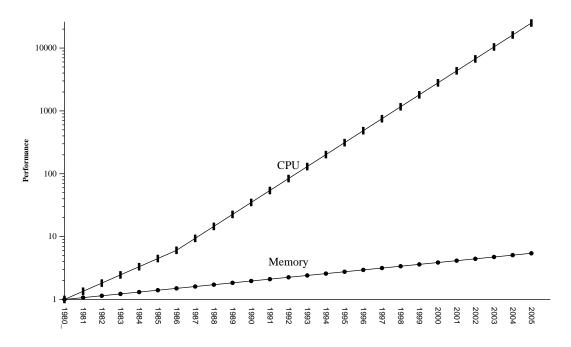

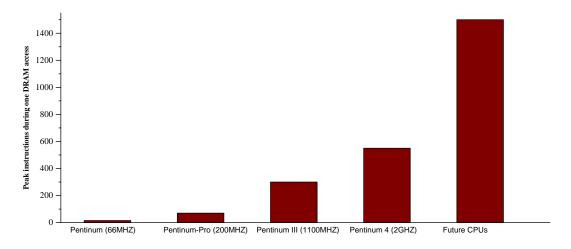

Modern processor speed continues to outpace memory speed [45]. Researchers project the performance gap will be even larger in the next ten years [3]. Hennessy and Patterson [45] illustrate the trend of memory-processor speed disparity as shown in Figure 1.1. The figure is based on the assumption that processor performance increases 55% per year from 1987 on, and 35% per year until 1986. In contrast, memory speed shows only 7% growth each year. This figure more or less reflects the reality of commercial systems. Figure 1.2 shows the gap of an Intel family [37], where each bar displays the peak number of instructions per memory access. It is easy to observe that there is an exponential increase of the bar height.

Both Figure 1.1 and Figure 1.2 describe the worst case scenario. In reality, a typical commercial architecture relies on a memory hierarchy to alleviate memory bottlenecks. A modern system usually contains two or more levels of cache, starting with the fastest Level 1 cache, which is closest to the CPU. Caches, which exploit program locality, perform well for some applications but are not always effective. Applications that have poor locality or large working sets often show poor cache performance. Several modern architectural features, such as out-of-order execution and lock-up free caches, effectively hide the Level 1 latencies for many programs [17, 100], though not all. These techniques, however, cannot

Figure 1.1. Processor and memory performance trend

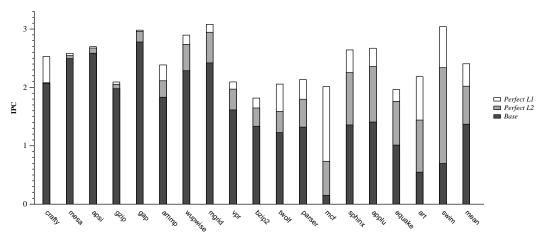

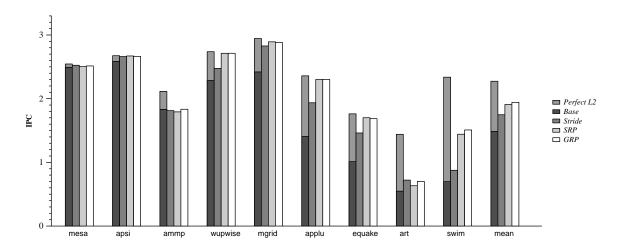

hide the latencies of the Level 2 cache and beyond. Hundreds of cycles that result from DRAM accesses cannot be tolerated, thus causing significant performance degradation. For the SPEC CPU2000 benchmarks running on a modern high-performance microprocessor, over half of the time is spent stalling for loads that miss in the Level 2 cache [69]. We observe similar results in our simulations for a subset of SPEC CPU2000 benchmarks and *sphinx*, a speech recognition application [68]. Figure 1.3 compares the performance of a system with a configuration of a modern processor and a realistic memory hierarchy with two levels of cache versus a system with a perfect L1 cache and one with a perfect L2 cache with the stacked bar for each benchmark. The benchmarks are sorted by the size of the gap between a realistic system and one with a perfect L2 cache. The geometric mean of this performance gap is 33.7%.

Despite an enormous amount of research, memory stalls remain a challenge to computer performance. One reason is that past work does not fully exploit the strengths of both software and hardware. As we shall discuss in Chapter 2, existing techniques dominantly lean towards either a pure software solution, such as loop transformations and software

Figure 1.2. Peak instructions per memory access of Intel family

Figure 1.3. Processor performance

prefetching, or a pure hardware solution, such as the victim cache and hardware prefetching. Even the limited amount of research on hardware/software cooperation that we discuss in Section 2.3.3 is typically restrained by the current hardware/software interfaces. In this dissertation, we propose a novel hardware/software cooperative approach with a new hardware/software interface to address the increasing performance gap between the main memory and the processor.

## 1.1 Our Hardware/Software Cooperative Approach

Memory system performance can be improved with closer cooperation between software and hardware. Software has the advantage of its global view of the whole program, which is obtained through static compiler analysis. This static knowledge is typically coarse-grained and imprecise. For example, at compile time it is easy to detect if an array is accessed in a loop nest and reused in the following nest. But it is hard or impossible to calculate exactly how many array elements are reused if the loop bounds are unknown. However, even this imprecise view can serve as valuable guidance for run-time decisions. Run-time knowledge is typically precise but its scope is very limited. The information of the future execution at a point is unknown. Prediction from past behavior is usually restricted by a limited history because retaining a complete history of run-time status is prohibitive due to its very high storage and retrieval cost. By combining the strengths of software and hardware, the run-time system attains greater power to predict. Relying on compiler prediction combined with current run-time status and limited history, the run-time system can achieve high performance with relatively low cost. This dissertation investigates the memory system, but this approach can also be used to improve instruction level parallelism in a processor core and in other circumstances.

In the past, a limited amount of research has used a similar hardware/software approach to improve performance. As we discuss in Chapter 2, that research is typically specific to a particular application domain and restricted by poor interfaces between hardware and software. In most modern computer architectures, the hardware/software interface is limited to simple load/store instructions. The compiler generates memory access instructions. At run time, the processor sends requests to the memory system upon the execution of these instructions. It has no control beyond that. A memory request contains an address used to look up a value in the main memory or the cache. The request does not specify more details such as which slot the accessed data should sit in a cache set in order to exploit the best cache performance.

Our work extends the instruction set architecture (ISA) with a few bits in the memory instructions. The compiler encodes its global view of the whole problem into these bits. Combined with precise run-time status, the hardware is enhanced to use these bits to control memory system behavior and thus is able to utilize system resources better. This dissertation shows that this ISA extension is effective given its light-weight hardware support and compiler implementation. However, as the memory-processor performance gap keeps getting larger, we expect to need a richer interface, which can convey more information.

The cooperative approach can be applied to improve almost every aspect of the memory system including cache replacement, data prefetching, memory disambiguation, and cache coherence, to name a few.

- Cache replacement. A typical cache replacement decision is made based on runtime history. Using the cooperative approach, the decision can be improved with knowledge of the future access pattern detected statically through compiler analysis.

- 2. Data prefetching. Cooperative data prefetching can achieve both the accuracy of soft-ware prefetching and the high performance of hardware prefetching. We can enhance hardware prefetching with compile-time locality information. We can depend on the run-time status to schedule prefetch requests and the compiler analysis to select what to prefetch.

- 3. Memory disambiguation. The interaction of the compiler and the hardware can supply us with a cost-effective run-time memory disambiguation technique to increase parallelism of memory instructions. Specifically, compile-time dependence testing and alias analysis can speed up speculative execution by predicting if a RAW (read after write) dependence exists between a store and a load.

- 4. Cache coherence. One application is to use the compiler to mark if a read or write is non-shared. This can reduce false sharing misses and speed up parallel execution.

In this dissertation we focus on application of our approach to cache replacement and data prefetching, aiming to improve cache performance. To achieve high cache performance we can rely on 1) hardware advances, which reduce the cycle penalty of cache misses, 2) techniques to reduce cache misses, or 3) approaches to tolerate latencies [45]. Our cache replacement work falls into the second category and our prefetching work into the third. Our work emphasizes the importance of software/hardware interaction to improve memory system performance.

## 1.2 Guided Cache Replacement

To attain fast cache access times, current microarchitectures have direct-mapped or low, 2 or 4-way, set-associative organizations [45, 47]. This choice trades off lower cache hit rates for higher clock rates to achieve better total performance. In set-associative caches, cache replacement policies determine which line to evict on a miss and will cause extra misses when making poor decisions. Current cache replacement policies typically rely only on run-time knowledge to make replacement choices. These policies do not always use cache memory effectively; i.e., even though the cache has sufficient capacity to retain data that will be reused in the future, they do not retain it [3, 14, 79]. Using a cooperative approach, we propose a novel compiler and architecture mechanism that uses compiler prediction of future accesses to improve cache replacement decisions directly. We particularly focus on enhancing the widely used LRU (least recently used) replacement policy.

Our new compiler mechanism guides cache replacements by selectively predicting when data will or will not be reused. We encode the compile-time prediction into memory instructions. We develop a comparative model that uses dependence and array section analysis to determine static locality patterns in a program. In Chapter 3, we first prove that our model matches or improves hit rates when compared to LRU. We then present an implementation that uses a single tag bit called the *evict-me* bit. On a miss, the architecture replaces a line with this bit set. Our compiler algorithm aggressively marks data as evict-

me if the data volume accessed between its reuse is (or it predicts the reuse is) greater than twice the cache size. The compiler can mark data aggressively since, if all the data fits in the cache, there will be no replacements. By applying the evict-me bit to both Level 1 and Level 2 caches, we observe up to 21% simulated performance improvements for current technology on a selection of scientific benchmarks and 34% for a technology prediction for 5 years from now [3]. On average, we reduce simulated execution time on our benchmarks by 5% to 16%, depending on the cache configuration. These results suggest that run-time cache replacements can benefit from the static compiler oracle, which tells data reuse patterns, to reduce cache misses and thus improve overall performance.

## 1.3 Guided Region Prefetching

The cache replacement techniques discussed in Section 1.2 help to reduce cache misses. But they cannot eliminate them all. For example, they help little on compulsory misses, which are caused by the first run-time accesses in an application. Prefetching is a popular technique to tolerate memory latencies. Researchers have proposed a large number of software and hardware prefetching schemes. Each of these two classes of prefetch solutions have distinct advantages and drawbacks. Pure software prefetching is typically highly accurate, but incurs run-time overhead and cannot issue prefetches sufficiently far in advance of a load to hide main memory access latencies [69]. Hardware-only schemes can prefetch spatial regions [23, 24, 54, 84, 92], pointer chains [32, 53, 89], or recurring patterns [66]. While these schemes can hide much of the main memory access time, they can also consume substantial amounts of memory bandwidth. This additional traffic does not always degrade uniprocessor performance, but it increases power consumption, and will likely degrade performance on multiprocessors. Since off-chip bandwidth will be the dominant limiter of scalability for future chip multiprocessors (CMPs) [51], prefetch schemes that consume bandwidth inefficiently will not be practical. While some schemes throttle

|                    |         | traffic  | Performance gap     |

|--------------------|---------|----------|---------------------|

|                    | Speedup | increase | from perfect L2 (%) |

| No prefetching     | 1       | 1        | 34                  |

| Stride prefetching | 1.15    | 1.09     | 24                  |

| SRP                | 1.23    | 2.80     | 19                  |

| GRP                | 1.21    | 1.23     | 20                  |

**Table 1.1.** Summary of prefetching performance and traffic

prefetching when the accuracy drops below a threshold, they then miss opportunities for issuing useful prefetches and thus trade performance against accuracy [36].

We propose an approach that builds on the strength of hardware and software prefetching, called Guided Region Prefetching (GRP). In GRP, sophisticated compiler analysis produces a rich set of load hints, including the presence or absence of spatial locality, pointer structures, or indirect array accesses. A run-time hardware engine, triggered by L2 cache misses, generates prefetches based on the compiler's hints. GRP thus benefits from compiler analysis of application reference patterns, but—unlike traditional software prefetching—the compiler is not required to generate or schedule individual prefetch addresses. Because the hardware generates the prefetches, it can run far ahead of the missing references. Because the compiler guides it, the hardware need not struggle to deduce future references with complex pattern matching on prior accesses stored in large tables.

Table 1.1 shows a summary of GRP results using the geometric mean of the SPEC CPU2000 benchmarks plus *sphinx*. Without prefetching, the mean performance across the benchmark suite is 34% lower than a perfect Level 2 cache. Stride prefetching (using the Sherwood et al. design [92]) provides a 15% speedup over no prefetching. SRP, which uses no compiler analysis, outperforms stride prefetching by 7%, but consumes excessive memory bandwidth, a 180% increase over a system with no prefetching. GRP provides near-equivalent performance to SRP but with substantially less traffic, an increase of only 23% over no prefetching. This reduction in traffic saves power and is more amenable to multiprocessor systems, where additional traffic can directly affect performance. To summarize, GRP as a cooperative prefetcher is able to make SRP, the hardware-only prefetcher,

practical by using compiler guidance. On the other hand, as is shown in previous work [69], SRP itself outperforms a state-of-the-art software prefetcher. The cooperative prefetcher thus provides a cost-effective solution for high performance.

## 1.4 Combining Cache Replacement and Region Prefetching

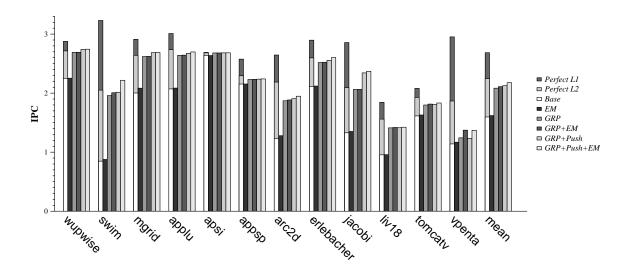

GRP is targeted to the Level 2 cache. Due to the complexity of the prefetching engine, it is impractical to implement a similar prefetching engine for the Level 1 cache. As shown in Figure 1.3, there is still a significant performance loss due to L1 stalls. Guided cache replacements alleviate this problem. However, even an optimal cache replacement policy usually cannot eliminate all misses. Given the high prefetching accuracy of GRP, most data prefetched to L2 will be used at L1. Accesses to these data at the Level 1 cache are L1 misses and thus suffer the L2 latencies. To tolerate these latencies, we design a prefetching engine between the Level 2 and Level 1 cache, which pushes the prefetched data into the Level 1 cache. Our results show that pushing prefetched data into the L1 cache can further improve memory system performance.

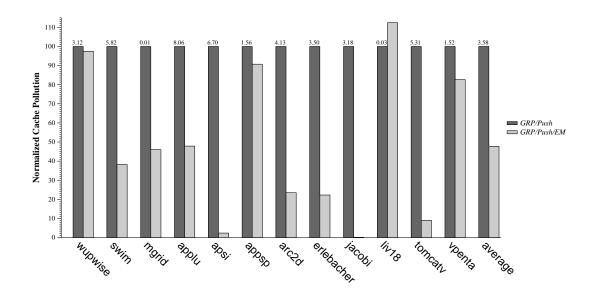

Typically, the Level 1 cache size is much smaller than the Level 2 cache. Pushing data into L1 introduces cache replacements and can pollute the cache. In Chapter 5, we examine the impact of the LRU and MRU placement policies. Furthermore, we combine guided cache replacement with L2 region prefetching and L1 data pushing. By marking a cache line as *evict-me*, the compiler optimistically predicts that the cache line will not be reused in the near future. The side effects of an unused prefetch or pushed line are reduced if it replaces an evict-me line. We find that compiler-guided replacement helps reduce the cache pollution of the push scheme by roughly half.

## 1.5 Dissertation Organization

We organize this dissertation as follows. In Chapter 2, we briefly cover some background material and discuss related work. We introduce basic notations for the memory hierarchy and survey related techniques for tolerating cache latencies. We focus on the literature targeting cache replacement policies and data prefetching that are directly related to this dissertation. Finally, we introduce the Scale compiler infrastructure in which we implemented all our compiler algorithms.

In Chapter 3, we describe our cooperative cache replacement algorithms. We present a theoretical model in which we formulate our algorithms. We prove that the algorithms will generate hit rates at least matching LRU. We then present two implementation techniques. In one implementation, we use an impractical 16-bit hint to determine an upper bound of our approach. We then focus on a one-bit (evict-me) implementation and present the compiler analysis to generate this bit.

In Chapter 4, we introduce guided region prefetching and compare it with hardware-only region prefetching and stride prefetching. We present a series of compiler algorithms generating various compiler hints. We use these hints to enhance region prefetching and pointer prefetching. We show that our locality analysis is sufficient to catch most spatial reuses, so GRP is able to match the performance of SRP but reduce SRP's bus utilization to a practical level.

In Chapter 5, we first design a new prefetching engine, which pushes to the Level 1 cache the data prefetched into the Level 2 cache. We then put this push scheme, guided region prefetching, and guided cache replacement together. We show that the three methods interact well to improve performance further. We also observe that guided cache replacement can alleviate the pressure on cache replacement introduced by pushed data.

We conclude this dissertation in Chapter 6 by discussing the remaining problems and possible future work, and listing other applications of our cooperative approach.

# 1.6 Summary of Contributions

We make the following contributions in this dissertation:

- 1. Emphasizing the importance of hardware/software cooperation: There is only a limited amount of work that uses software/hardware collaboration to attack the memory wall problem. Within the research area, we emphasize the importance of the flexibility of using ISA extension to enrich the interface between software and hardware and propose practical applications of the extension. We develop and implement a series of compiler algorithms to manipulate the new ISA. We use simulators to explore the effectiveness of the compiler hints on performance and traffic.

- 2. A new cache replacement policy: We are the first to use those specific static compiler hints to direct run-time cache replacements. We describe a volume-based compile-time analysis to generate compiler hints and propose a practical cache architecture implementation based on a one-bit extension to the ISA and caches. We find that this new replacement policy is able to cut misses and often achieves miss rates close to optimal. Its performance depends on cache parameters and input data set sizes.

- 3. A new region prefetching technique: Our work distinguishes itself from previous region prefetching work in its compiler control. We use compiler hints to help hardware decide when to exercise prefetching and what is the appropriate prefetching region size. We find that compiler-guided region prefetching matches the performance of hardware-only region prefetching while reducing bus traffic to a practical level.

- 4. A thorough study of region prefetching and pointer prefetching: Our work thoroughly studies the interaction between region prefetching and pointer prefetching. We find region prefetching outperforms pointer prefetching in most cases, and their combination does not lead to a performance improvement.

- 5. A study of the interaction between cache replacement and prefetching: We study how a cache replacement policy can affect prefetching efficiency. Our results show that a well-tuned cache replacement policy can reduce the side effects of prefetching, such as cache pollution.

We show that our cooperative approach is an effective direction for addressing the memory wall problem. Through its applications for cache replacement and data prefetching, we demonstrate that compile-time analysis is able to supply copious information that the hardware can exploit to improve memory system performance. On the other hand, the run-time status tracked by hardware is critical for fully exploiting compiler hints. The limitation of this approach lies in its dependence on the ISA extension since the budget on ISA bits usage is very tight, particularly for RISC architectures. However, our work suggests it is a cost-effective way to improve memory system performance.

#### **CHAPTER 2**

#### BACKGROUND AND RELATED WORK

This chapter provides background material and discusses related work. It first describes the most pertinent knowledge on how modern memory systems work and how our techniques benefit from state-of-the-art technologies. It then concentrates on related work in cache replacement, cache miss characteristics, and various prefetching techniques. We emphasize our contribution in both its underlying methodology and its breakthroughs in solving existing problems in memory systems. We also include a brief introduction to Scale, the compiler infrastructure we use to implement all of the compiler analyses described in this dissertation.

# 2.1 Memory System

In this section, we first address the role of the memory hierarchy in modern systems. We then focus on those recent advances in cache, DRAM, and processor core architectures that are most related to memory system performance and the hardware or software techniques discussed in this dissertation.

#### 2.1.1 Cache Architecture and Cache Miss Classification

As latencies for accessing main memory keep growing, numerous techniques have been proposed and implemented to bridge the gap. Most of these techniques concentrate on the memory hierarchy. A typical *memory hierarchy* consists of register files, several levels of caches, the main memory, and the disk. The levels of a memory hierarchy usually follow an *inclusion* paradigm: all data in one level can be found in the level below. A higher level

(closer to the CPU) is faster but smaller than lower levels. Generally, the literature refers to all the levels between the CPU and the main memory as *caches*. We refer the reader to an early survey by Smith [98] for a comprehensive introduction to cache design and some techniques used to improve cache performance.

A *block* or a *line* is the minimum unit of information that can be present in the cache (*hit* in the cache) or not (*miss* in the cache). The restrictions on where a block can be placed in a cache create three categories of cache organizations. If each block has only one place it can appear in the cache, the cache is *direct mapped*. If it can be placed anywhere in the cache, the cache is *fully associative*. If it can be placed in a restricted set of places, the cache is *set associative*. In a set-associative cache, a *set* refers to a group of places each of which a block can be mapped to. A fully-associative cache can be considered as a special set-associative cache where the whole cache is a single set.

The memory hierarchy will speed up execution if accesses can be served at the upper levels (hits). Otherwise, it will suffer the longer latency due in misses to the higher levels. Hill and Smith classify cache misses into three categories: compulsory, conflict, or capacity [48]. A compulsory miss is the first access to a cache line. A capacity miss occurs when the cache size is too small to hold all the cache lines referenced by a program. With sufficient capacity, a conflict miss occurs when multiple cache lines are mapped to the same set in the cache, and the program subsequently references an evicted line. One can use the least recently used (LRU) replacement policy and a fully associative cache to define the three types of misses [46, 48, 67]. A capacity miss happens when a data item that is reused cannot be kept even in a fully associative cache. A conflict miss occurs when a reused data item can be kept in a fully associative cache, but is evicted due to limited cache associativity or a poor cache replacement decision in a given cache configuration. Using the LRU replacement policy makes statistics on different categories of cache misses simpler. Stricter statistics following the original definition require optimal cache replacement. Sugumar and

Figure 2.1. Conventional DRAM block diagram

Abraham suggest a measurement using optimal cache replacement [102] as we discuss in Section 2.2.2.

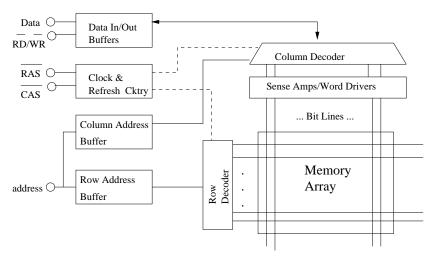

#### 2.1.2 DRAM Architecture

Main memory is typically organized as DRAM (Dynamic Random Access Memory). Figure 2.1 illustrates a conventional DRAM. The term DRAM implies that an access to any randomly chosen location requires about the same amount of time. However, this is not the case since DRAM manufacturers have created several new DRAM architectures to respond to the memory wall problem. DRAM is conventionally arranged as a matrix of "cells". The memory accessing address is divided into a *row address* and a *column address*, which are then decoded to access the memory array. A data access sequence consists of a *row address strobe* ( $\overline{RAS}$ ) signal followed by one or more *column address strobe* ( $\overline{CAS}$ ) signals. The data in the storage cells of the decoded row address is moved into a bank of sense amplifiers during  $\overline{RAS}$ . In the following  $\overline{CAS}$ , the decoded column address selects data from the amplifiers.

In a conventional DRAM, there is only one  $\overline{CAS}$  following each  $\overline{RAS}$ . In *fast page mode* DRAM, multiple  $\overline{CAS}$  signals are allowed, and the amplifier set is called a *page* or a *hot row*. This DRAM is thus designed to exploit more spatial locality. We refer the reader to

Cuppu et al. [34] for characteristics of a list of representative DRAM techniques such as Synchronous DRAM (SDRAM) and Rambus DRAM (RDRAM).

Cuppu et al. [33] experiment with the performance effect of the system-level parameters of a DRAM system, such as the number of memory channels, burst sizes, queue sizes and organizations, turnaround overhead, memory controller page protocol, and algorithms for assigning request priorities and scheduling requests dynamically. They find that concurrency in the primary memory system is very important, even for a uniprocessor, and support for concurrent transactions improves performance by roughly a factor of two. They suggest that improving concurrency by subdividing the memory bus into multiple channels is risky, as it relies on the ability of the application to sustain the level of concurrency equal to the number of channels, otherwise the extra channels lie unused. From this point of view, the intra-channel concurrency is safer to exploit than inter-channel concurrency. Taking advantage of the Rambus design, Region Prefetching, as proposed by Lin et al. [69], issues prefetches only when a free channel is available and thus avoids channel contention with regular memory accesses. Our prefetching technique is an extension of this work and includes this optimization.

McKee et al. [76] find DRAM performance is largely dependent on the the order of accesses for streaming type workloads. They propose a stream buffer and a memory scheduling unit between the CPU/Cache and main memory. The compiler detects streams and generates stream access instructions. The memory scheduling unit is able to reorder the streaming accesses and the regular requests from caches and issue the accesses to main memory in an optimal order. The "optimality" comes from better hit rates to hot pages in modern DRAM systems. Generally, the access time of a page hit is a factor of two to three faster than a page miss. Modern DRAM designs, such as SDRAM and Rambus DRAM, make the access pattern and scheduling of main memory accesses more critical to the overall performance of the hierarchy. Varying cache replacements and prefetching policies change the data stream into and out of main memory. It is not the focus of this

dissertation to discuss the effect on main memory; however, both of our techniques aim to reduce the number of main memory accesses. Region prefetching takes direct advantage of the Rambus DRAM design. The prefetching requests are prioritized based on the availability of free channels.

## 2.2 Improving Cache Performance

In this section, we first introduce concepts of program locality, to which almost all cache improving approaches can be related. We list several theoretical studies of cache replacement policies. Then we discuss research on cache miss characteristics. We focus on hardware and software enhancements for improving cache performance and cache replacement algorithms. We single out related work in data prefetching and discuss it separately in Section 2.3. We conclude with some recent work on data remapping and cache coloring, and their impact on our work.

## 2.2.1 Program Locality

The performance benefits of a memory hierarchy stem from *program locality*. The classical notions of locality found in programs are: *temporal locality*—if an item is referenced, it will be referenced again soon; and *spatial locality*—if an item is referenced, an adjacent item will tend to be referenced soon [45]. When a program exhibits good locality, we expect most data will be available in the higher levels of the memory hierarchy; and thus we will avoid the longer latencies of the lower levels.

To improve cache performance, we can either improve program locality, exploit program locality better, or hide latencies of accessing data with poor locality. Examples of improving program locality are loop transformations, such as loop tiling and loop permutation. Our work on cache replacement policies is an example of exploiting program locality. Region prefetching exploits spatial locality and hides latencies.

#### 2.2.2 Trace-based Cache Studies

A lot of theoretical cache work depends on having a complete program trace. Although our work does not depend on traces, some theoretical research motivates it. The notion of a program trace also facilitates our introduction to notations of data reuse.

Belady [10] pioneered research on replacement policies by comparing random cache replacement, LRU, and an optimal algorithm. His research originally targeted virtual memory page replacement, but the overall logic applies well to cache replacement. Given the trace of page accesses, the optimal algorithm should always replace the page with the largest reuse distance. A *reuse* of an access is the next access to the same address. *Reuse distance* is the number of distinct accesses between an access and its reuse. Belady proposed an optimal page replacement algorithm, called the MIN algorithm, given the entire program access sequence. Our cache replacement policy is inspired by the optimal cache replacement policy. Rather than relying on the whole program trace, we instead use static compiler analysis to predict the reuse distance.

Sugumar and Abraham [102] use Belady's algorithm to characterize capacity and conflict misses. They present three techniques for fast simulation of optimal cache replacement. Using a limited lookahead strategy, they are able to simulate multiple optimal caches with a one-pass scan. They also propose a tree-based fully-associative cache simulation and a partial inclusion scheme for simulating multiple set associativities. They find that the optimal miss rate is up to 70% lower than those under an LRU policy for 9 selected benchmarks. A simulator, *sim-cheetah*, implemented all these techniques. Sim-cheetah is the version adapted for SimpleScalar, a simulation tool set we use in this dissertation [15].

Temam [103] extends Belady's optimality result by simultaneously exploiting spatial and temporal locality. By considering both types of localities, the study evaluates the potential benefits of future memory optimizations and provides a performance upper bound for higher memory levels. Burger [13] uses the MIN algorithm to obtain a formal lower bound of the amount of bus traffic that a cache may produce.

All the studies discussed above seek to understand cache characteristics rather than to implement a real cache and related algorithms. Although our theoretical model in Section 3.2.1 is also based on static traces, we apply it to a real cache using compiler analysis. In Chapter 3, we also compare our algorithms to the optimal cache policy using Sugumar and Arbraham's simulation techniques [102].

### 2.2.3 Cache Miss Analysis

Ghosh et al. [39] suggest a set of miss equations for precisely analyzing cache misses for individual loop nests. Their framework enables compiler algorithms to find optimal solution for transformations like blocking, loop fusion, and padding. It also helps when reasoning about how different transformations work together.

Chatterjee et al. [22] set up a set of Presburger formulas to characterize and count cache misses. Chatterjee's model is powerful enough to handle imperfectly nested loops and various non-linear array layouts.

Both models could probably be extended to suggest evictions by calculating cache misses when applying different eviction schemes. They currently drive optimizations by comparing the number of misses between runs of the program compiled with different options. Our work uses heuristics and is less precise for an individual nest, but computes or estimates the data volume between nests and between reuses. A better cache miss analysis could improve our results.

#### 2.2.4 Hardware Enhancement of Cache Replacement

Direct-mapped first level caches have been popular because of their low hit cycle time. They can yield good system performance, even though set-associative caches have lower miss rates [45, 47]. Due to rapid increases in miss cycle penalties, many recent architectures use at least 2-way set-associative L1 caches, e.g., the Compaq Alpha 21364 and Sun SPARC 2. To attain fast access time to L1 caches in future technologies, processors will probably have small L1 caches with a low degree of associativity [3]. We observe that the

industry is starting to deliver 3-cycle L1 caches. Some architectures trade higher associativity with a simpler cache replacement policy. For example, the IBM RS/6000 7043 has a 64K 128-way Level 1 cache that uses random replacement.

In Chapter 3, we propose an *evict-me* cache to enhance cache replacement. Each line is tagged with a bit called the *evict-me* bit. A line with the evict-me bit set is preferred for eviction on a cache miss. The hardware mechanisms of an evict-me cache do not increase cycle time and are effective only on set-associative caches; i.e., the hit time is unchanged. The replacement logic on a miss considers one more bit. Our work tries to achieve both fast hit cycle time and low miss rates.

The evict-me bit is similar to, but not the same as, the Alpha's *evict* instruction, which evicts a cache line immediately and thus cannot tolerate imprecision [58]. The evict instruction is designed to help maintain cache coherence, rather than to enhance locality. Our approach works for variable cache and data sizes because only when the data do not all fit in the cache will the replacement algorithm use our information. The Alpha's *prefetch and evict-next* instruction loads the line to the Level 1 cache and evicts it on the next miss to the cache set [58], but we instead tag actual loads, not speculative prefetches.

Numerous dynamic or hardware techniques have been proposed to reduce cache misses or alleviate cache pollution to improve hit rates, e.g., [2, 52, 54]. The victim cache was originally designed to enhance direct-mapped caches [54]. It is a small fully-associative buffer between the Level 1 and 2 cache, which stores replaced data to reduce conflict misses that occur close together in time. The evicted L1 cache line exchanges with the hit line in the victim buffer. The victim cache is probabilistic, rather than predictive.

Wong and Baer [112] enhance LRU with a temporal bit for each cache line. Temporal bits act oppositely to our evict-me bits: they specify lines to *retain* rather than lines to *evict*. Wong and Baer determine temporal bit settings using profiling or an online hardware history table. The temporal bit of a cache line is reset when the line is hit. To avoid a marked dead line polluting the cache, the temporal bit of the LRU line is reset when a non-

LRU line is evicted. Rivers et al. [87] use a (hardware) detection unit, similar to a history table, to track reuses at run time and to categorize access as temporal/non-temporal and cacheable/non-cacheable. A non-cacheable access bypasses the cache to avoid pollution. Lai et al. [66] use a hardware history table to predict when a cache block is dead and which block to prefetch to replace the dead one. Our technique is based on static compiler analysis and does not require substantially additional hardware.

Hannnor and Reinhardt [43] present a practical, fully associative, software-managed secondary cache. Their system consists of an *indirect index cache* (IIC) and a replacement algorithm, *generational replacement*. The IIC's tag array is organized as a hash table and each tag entry contains a pointer to the data block, which makes the cache fully associative because the pointer can legally point to any block in the cache. Hannor and Reinhardt group cache blocks into a small number of prioritized pools. The software-managed generational replacement promotes and demotes cache blocks on a miss depending on their recent reference history. The software replacement algorithm achieves miss rate reductions from 8 to 85% compared to a 4-way LRU. Hannor and Reinhardt use software management to reduce the complexity of the hardware implementation of their design. Their replacement algorithm totally relies on run-time history and does not use any compiler-time analysis.

McKee et al. [77] use a stream buffer for stream-like data to bypass the cache. They rely on the compiler to detect stream array accesses and generate a special instruction to start a stream at run time. We mark stream data as *evict-me*, but our technique works on cache replacement directly and does not require an extra buffer.

The Intel IA-64 provides instructions to control caching [38]. Non-temporal loads/stores bypass the cache to avoid cache pollution due to streaming data. The IA-64 supports locality hints used by prefetch, load, and store instructions to control placements of cache lines in either a *temporal structure* or a *non-temporal structure*. The hints do not direct cache replacement, but our compiler analysis could specify the non-temporal instructions and locality hints. We do not explore that application in this dissertation.

# 2.2.5 Page/Cache Coloring and Data Remapping

Coloring is an approach to classify pages and cache lines used to assist varies runtime decisions. On-line page coloring and other mechanisms decrease paging, but are too expensive for higher levels of the memory hierarchy. For example, Early Eviction LRU (EELRU) [96] dynamically chooses to evict the LRU page or the  $e^{th}$  most recently used page. The reference history determines e, the  $early\ eviction\ point$ , but is too expensive to store and use for caches. This approach eliminates capacity page misses in a fully associative memory, whereas our technique removes conflict misses for caches, using static compiler control.

Some work uses cache coloring or data remapping to improve cache effectiveness and reduce conflict misses due to poor mapping [12, 18, 29, 91]. Calder et al. [18] use profiling to build a *Temporal Relationship Graph* (TRG), which shows a metric of cache interference among stack (local variables), global variables, heap objects, and constants. Using TRG, they propose an algorithm to decide the placement of each object in order to reduce cache interferences.

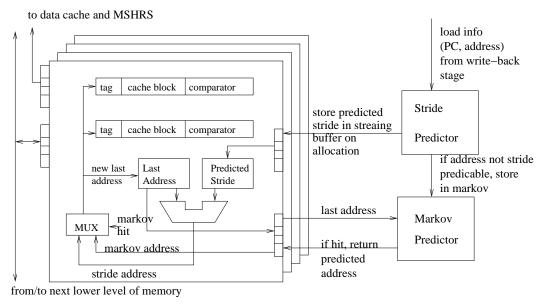

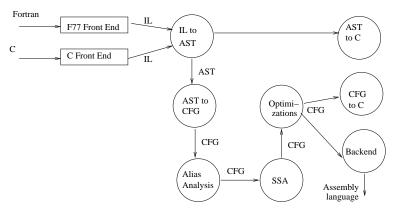

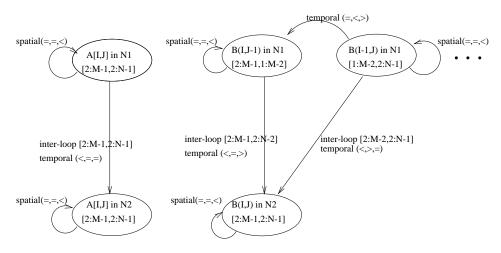

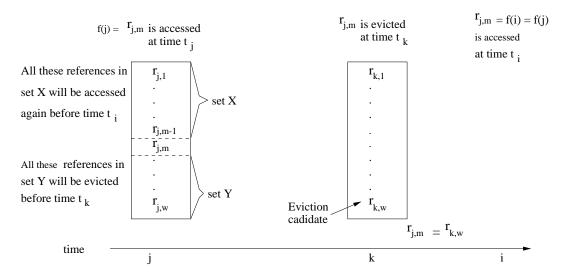

Sherwood et al. propose a hardware and a software approach to reduce cache misses by reordering pages in cache [91]. The software approach provides a color mapping at compile time for code and data pages, which can then be used by the operating system to guide its allocation of physical pages. The hardware approach works by adding a page remap field to the TLB, which is used to allow a page to be remapped to a different color in the physically indexed cache while keeping the same physical page in memory. Bugnion et al. implement a similar software page coloring approach for multi-processor systems [12]. They use compiler analysis of access patterns to direct the operating system to allocate physical pages.